00 «

00

о ьо

N5

Изобретение относится к импульсной технике и может быть использовано для построения устройств синхронизации с дискретным управлением.

Целью изобретения является повышение точности подстройки фазы выходного сигнала цифрового управляемого генератора.

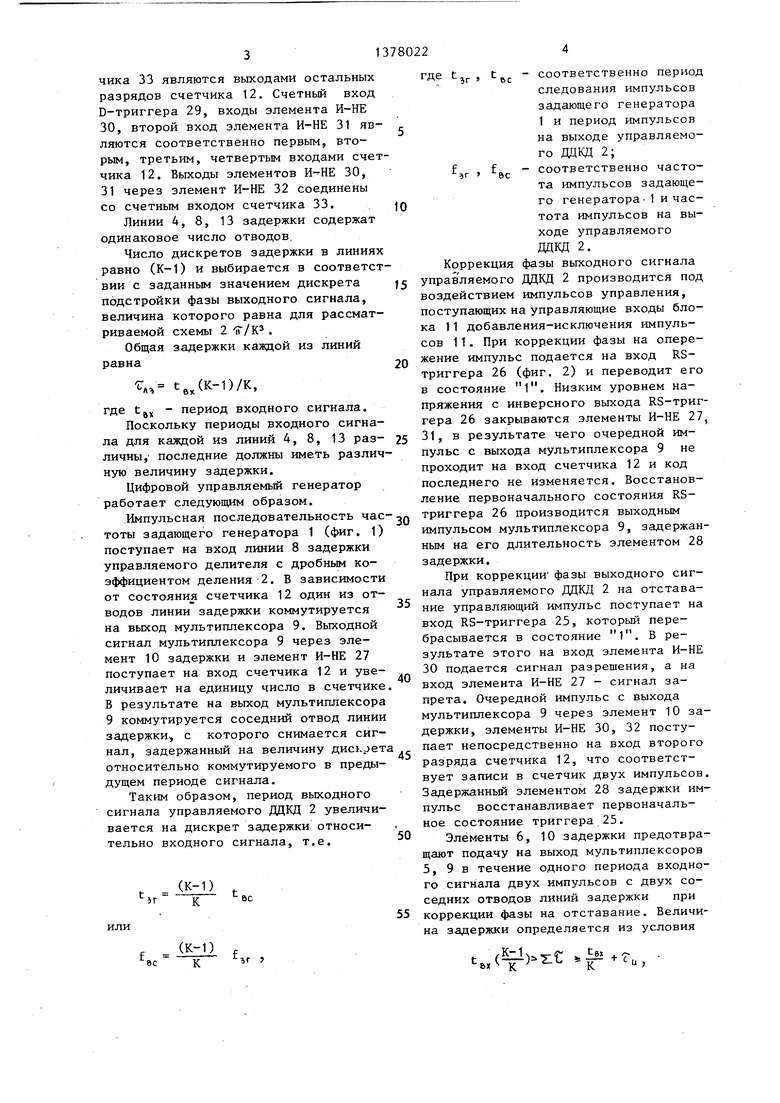

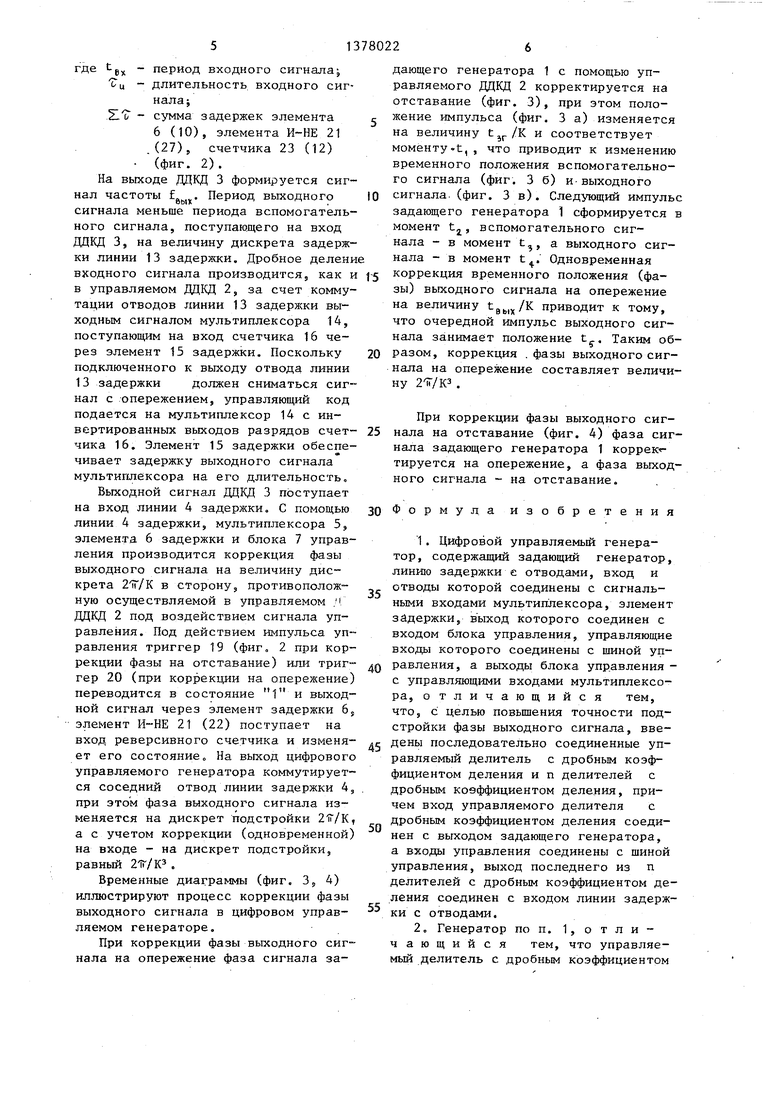

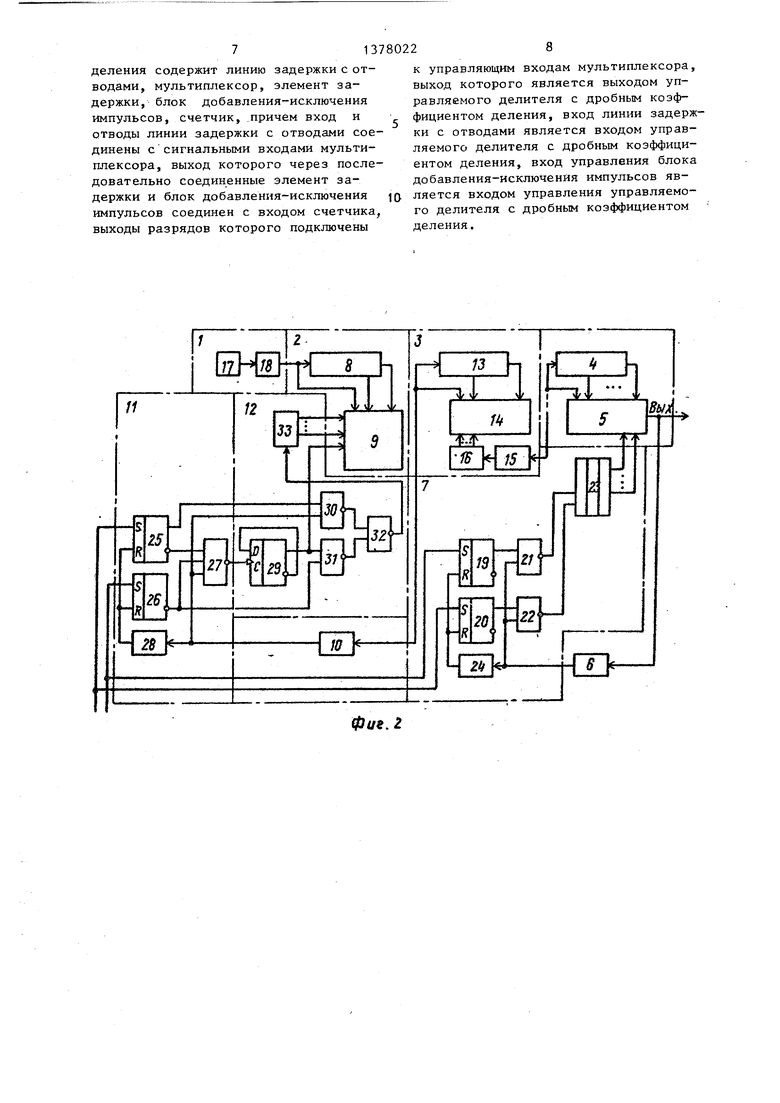

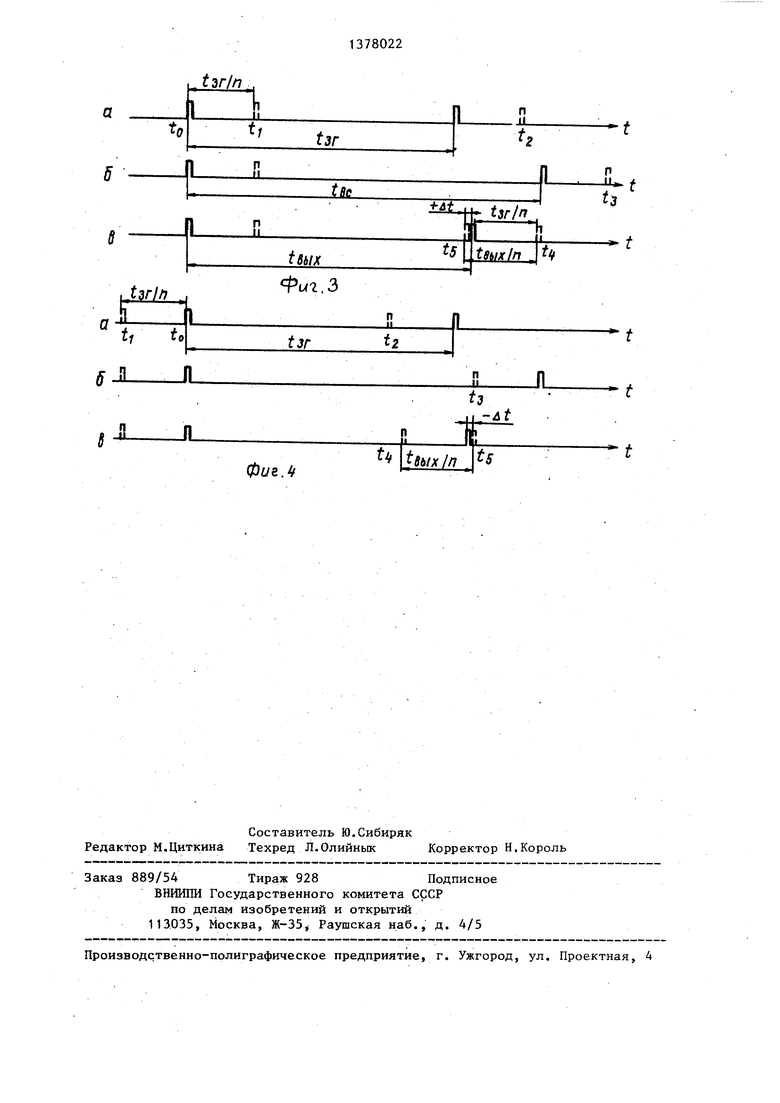

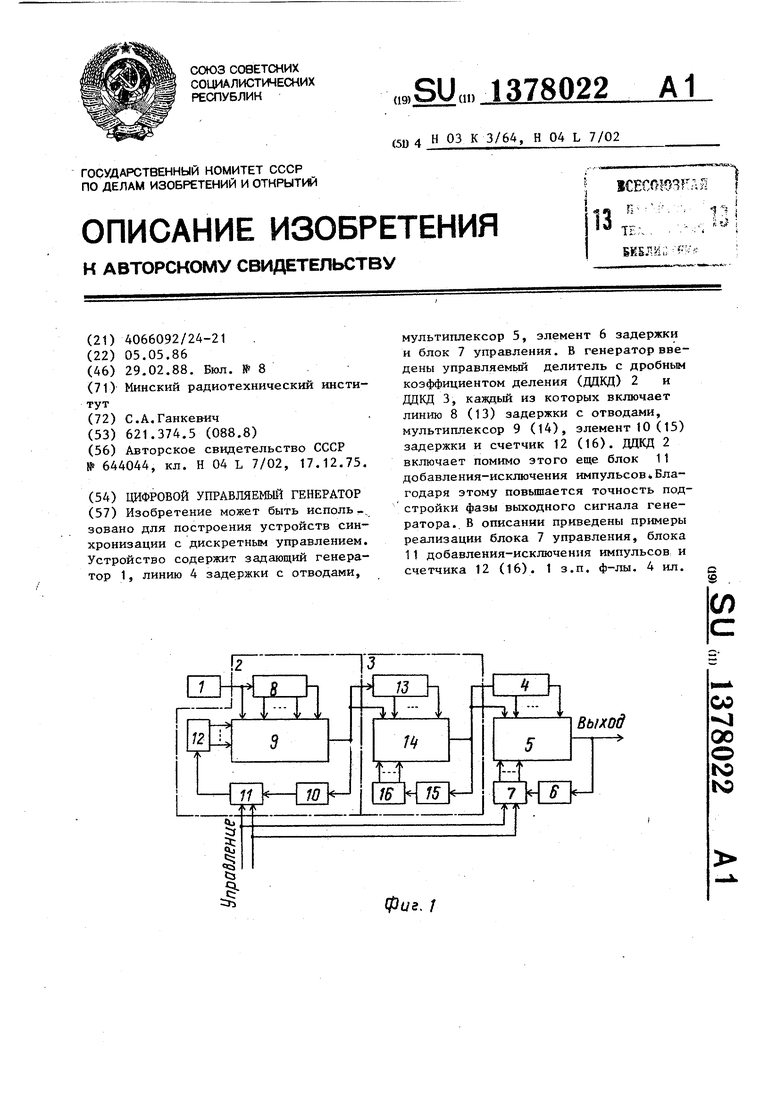

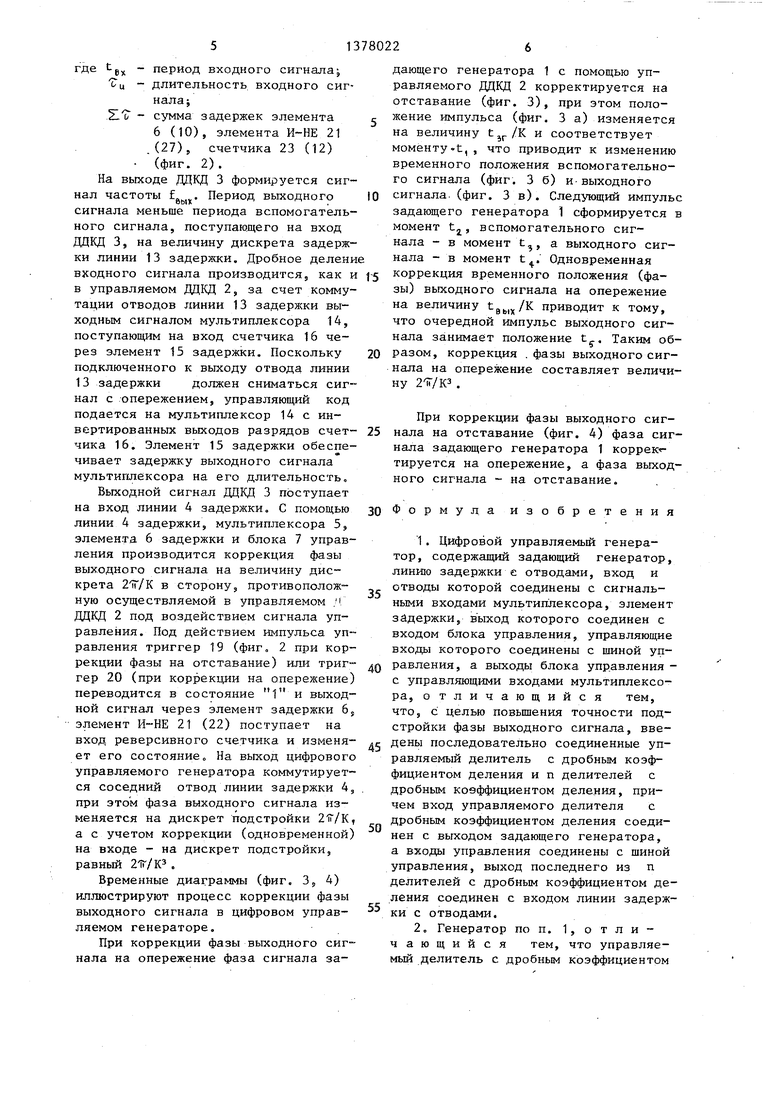

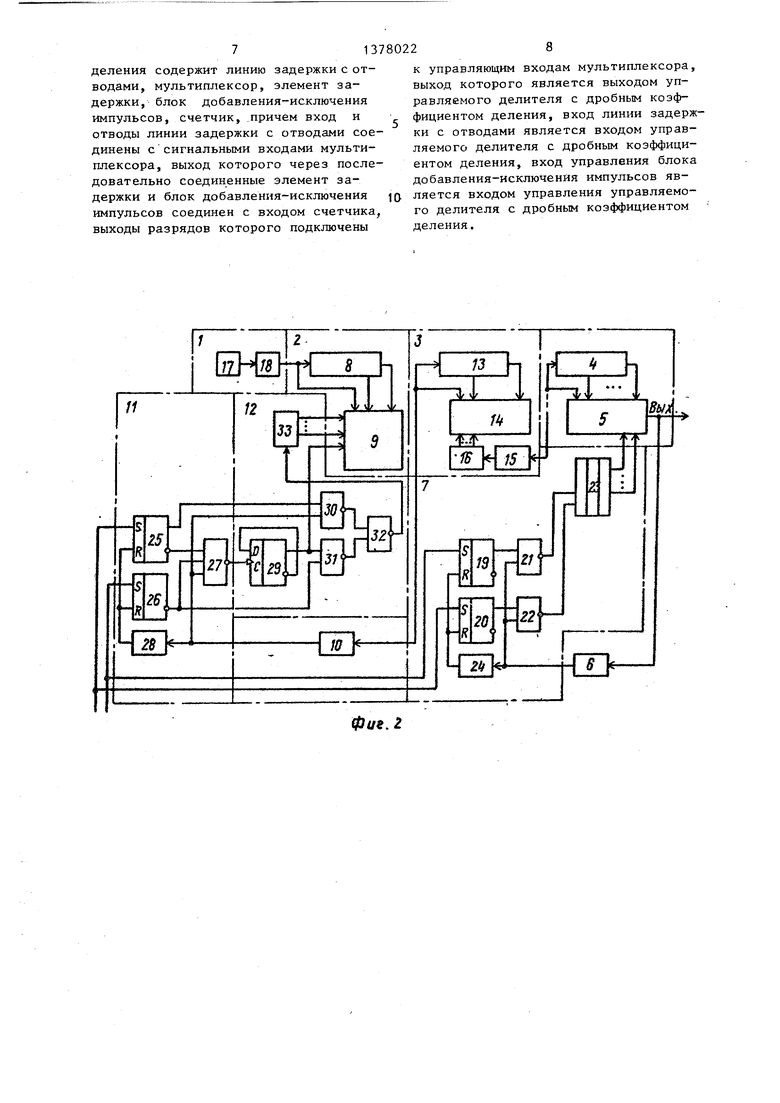

На фиг. 1 представлена функциональная схема цифрового управляемого генератора; на фиг. 2 - блок управления, блок добавления-исключения импульсов, счетчик; на фиг. 3, 4 - временные диаграммы работы цифрового управляемого генератора.

Цифровой управляемый генератор (фиг. 1) содержит последовательно соединенные задакнций генератор 1 , управляемый делитель 2 с дробным коэффициентом деления (ДЦКД), ДДКД 3, линию 4 задержки с отводами, мультиплексор 5, элемент 6 задержки, блок 7 управления. Вход и отводы линии 4 задержки соединены с сигнальными входами мультиплексора 5, управляющи входы которого подключены к соответствующим выходам блока 7 управления. Шина управления подключена к входам

которого подключены к управляющим входам мультиплексора 14. Вход линии

13задержки с отводами является вхо- дом ДДКД 3, а выход мультиплексора

14- его выходом.

Задающий генератор 1 (фиг. 2) содержит последовательно соединенные генератор 17, стабилизированньш кварцем, и формирователь 18, который формирует импульсную последовательность, соответствующую фронтам выходного сигнала генератора 17. Блок 7 управления (фиг. 2) содержит RS-триггеры

19, 20, элементы И-НЕ 21, 22, реверсивный счетчик 23, элемент 24 задержки.

Прямые выходы RS-триггеров 19,- 20 соединены с соответствующими первыми

входами элементов И-НЕ 21, 22, вторые входы которых объединены и соединены с входом элемента 24 задержки, выход которого соединен с входами установки RS-триггеров 19, 20. Выходы элементов И-НЕ 21, 22 соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика 23, выходы разрядов которого являются выходами блока 7 управления.Вход

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой управляемый генератор | 1987 |

|

SU1415448A1 |

| Программируемый делитель частоты | 1980 |

|

SU871340A2 |

| Цифровой управляемый генератор | 1989 |

|

SU1748247A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| Устройство фазирования шкалы времени электронных часов | 1990 |

|

SU1746356A1 |

| Устройство для коррекции сигналов времени | 1982 |

|

SU1158968A1 |

| Широкодиапазонный генератор импульсов с кратно дробной автоподстройкой частоты | 2019 |

|

RU2716222C1 |

| Устройство для фазовой синхронизации | 1983 |

|

SU1149425A2 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ВРЕМЕННОГО ИНТЕРВАЛА | 1991 |

|

RU2040854C1 |

| Устройство компенсации сдвига частот | 1985 |

|

SU1316097A2 |

Изобретение может быть исполь - зовано для построения устройств синхронизации с дискретным управлением. Устройство содержит задающий генератор 1, линию 4 задержки с отводами. мультиплексор 5, элемент 6 задержки и блок 7 управления. В генератор введены управляемьй делитель с дробным коэффициентом деления (ДДКД) 2 и ДДКД 3, каждый из которых включает линию 8 (13) задержки с отводами, мультиплексор 9 (14), элемент 10 (15) задержки и счетчик 12 (16). ДДКД 2 включает помимо этого еще блок 11 добавления-исключения импульсов . Благодаря этому повьшается точность подстройки фазы выходного сигнала генератора.. В описании приведены примеры реализации блока 7 управления, блока 11 добавления-исключения импульсоВ: и счетчика 12 (16). 1 з.п. ф-лы. 4 ил.

управления управляемого ДЦКД 2 и бло- зо элемента 24 задержки является входом

ка 7 управления.

1

Управляемый ДДКД 2 (фиг . 1) содержит линию 8 задержки с отводами, мультиплексор 9, элемент 10 задержки, блок 11 добавления-исключения

35

блока 7 управления. Входы предустановки RS-триггеров 19, 20 являются входами управления блока 7 управления.

Блок 11 добавления-исключения импульсов (фиг. 2) содержит RS-триггеры 25, 26,-элемент И-НЕ 27, элемент 28 задержки.

импульсов 11, счетчик 12.

Вхрд, выход и отводы линии 8 задержки подключены к сигнальным входам мультиплексора 9, а его выход через последовательно соединенные элемент 10 задержки, блок 11 добавления-исключения импульсов 11 соединены с входом счетчика 12, выходы разрядов которого подключены к управляющим входам мультиплексора 9, Вход линии 8 задержки с отводами является входом управляемого ДДКД 2, а выход мультиплексора 9 - его выходом Вход управления блок 11 добавления- исключения импульсов 11 является вхо дом управления управляемого ДДКД. 2.

ДДКД 3 (фиг. 1) содержит линию 13 задержки с отводами, мультиплексор 14, элемент 15 задержки и счетчик 16.

Вход, выход и отводы линии 13 задержки подключены к сигнальным входам мультиплексора 14, а его выход через элемент. 15 задержки соединен с входом счетчика 16, выходы разрядов

блока 7 управления. Входы предустановки RS-триггеров 19, 20 являются входами управления блока 7 управления.

Блок 11 добавления-исключения импульсов (фиг. 2) содержит RS-триггеры 25, 26,-элемент И-НЕ 27, элемент 28 задержки.

Инверсные выходы RS-триггеров 25, 26 и вход элемента 28 задержки соединены с соответствующими входами элемента И-НЕ 27. Выход элемента 28 задержки соединен с входами установки RS-триггеров 25, 26. Прямой выход RS-триггера 25, выход элемента И-НЕ 27 и в.ход элемента 28 задержки являются соответственно первым, вторым, третьим выходами блока 11 добавления-исключения импульсов 11. Входы предустановки RS-триггеров 25, 26 являются входами управления блока 11 добавления-исключения импульсов 11.

Счетчик 12 содержит D-триггер 29, элементы И-НЕ 30-32, счетчик 33.

Прямой выход D-триггера 29 соединен с первым входом элемента И-НЕ 31 и является выходом первого разряда счетчика 12. Выходы разрядов счет

чика 33 являются выходами остальных разрядов счетчика 12. Счетный вход D-триггера 29, входы элемента И-НЕ 30, второй вход элемента И-НЕ 31 являются соответственно первым, вторым, третьим, четвертым входами счетчика 12. Выходы элементов И-НЕ 30, 31 через элемент И-НЕ 32 соединены со счетным входом счетчика 33.

Линии 4, 8, 13 задержки содержат одинаковое число отводов,

Число дискретов задержки в линиях равно (К-1) и выбирается в соответствии с заданным значением дискрета подстройки фазы выходного сигнала, величина которого равна для рассматриваемой схемы 2 IT/K .

Общая задержки каждой из линий равна

t(K-i)/K,

где tj - период входного сигнала.

Поскольку периоды входного сигнала для каждой из линий 4, 8, 13 различны,- последние должны иметь различную величину задержки.

Цифровой управляемый генератор работает следующим образом.

Импульсная последовательность частоты задающего генератора 1 (фиг. 1) поступает на вход линии 8 задержки управляемого делителя с дробным коэффициентом деления 2. В зависимости от состояния счетчика 12 один из отводов линии задержки коммутируется на выход мультиплексора 9. Выходной сигнал мультиплексора 9 через элемент 10 задержки и элемент И-НЕ 27 поступает на вход счетчика 12 и увеличивает на единицу число в счетчике

8результате на выход мультиплексора

9коммутируется соседний отвод линии

задержки.

которого снимается сигнал, задержанный на величину дискрета относительно коммутируемого в предыдущем периоде сигнала.

Таким образом, период выходного сигнала управляемого ДДКД 2 увеличивается на дискрет задержки относительно входного сигнала, т.е.

ът

(К-1) К

ее

или

f.c

(К-1)

к

ъг

10

15

20

25

30

35

40

45

0

5

где tjj. , . - соответственно период следования импульсов задающего генератора 1 и период импульсов на выходе управляемого ДЦКД 2;

5г вс соответственно частота импульсов задающего генератора 1 и частота импульсов на выходе управляемого ДЦВД 2.

Коррекция фазы выходного сигнала управ ляемого ДДКД 2 производится под воздействием импульсов управления, поступающих на управляющие входы блока 11 добавления-исключения импульсов 11. При коррекции фазы на опережение импульс подается на вход RS- триггера 26 (фиг. 2) и переводит его в состояние 1. Низким уровнем напряжения с инверсного выхода RS-триг- гера 26 закрываются элементы И-НЕ 27, 31, в результате чего очередной импульс с выхода мультиплексора 9 не проходит на вход счетчика 12 и код последнего не изменяется. Восстановление первоначального состояния RS- триггера 26 производится выходным импульсом мультиплексора 9, задержанным на его длительность элементом 28 задержки.

При коррекции фазы выходного сигнала управляемого ДЦКД 2 на отставание управляющий импульс поступает на вход RS-триггера 25, который перебрасывается в состояние 1. В результате этого на вход элемента И-НЕ 30 подается сигнал разрешения, а на вход элемента И-НЕ 27 - сигнал запрета. Очередной импульс с выхода мультиплексора 9 через элемент 10 задержки, элементы И-НЕ 30, 32 поступает непосредственно на вход второго разряда счетчика 12, что соответствует записи в счетчик двух импульсов. Задержанньй элементом 28 задержки импульс восстанавливает первоначальное состояние триггера 25.

Элементы 6, 10 задержки предотвращают подачу на выход мультиплексоров 5, 9 в течение одного периода входного сигнала двух импульсов с двух соседних отводов линий задержки при коррекции фазы на отставание. Величина задержки определяется из условия

Чх( .|.г,,

де tg - период входного сигналаj TU - длительность входного сигнала;

51 - сумма задержек элемента 6 (10), элемента И-НЕ 21 .(27), счетчика 23 (12) (фиг. 2).

На выходе ДДКД 3 формируется сигал частоты f. ,. Период выходного

DDiX

игнала меньше периода вспомогателього сигнала, поступающего на вход ДКД 3, на величину дискрета задержи линии 13 задержки. Дробное деление ходного сигнала производится, как и в управляемом ДЦКД 2, за счет коммутации отводов линии 13 задержки выходным сигналом мультиплексора 14, поступающим на вход счетчика 16 через элемент 15 задержки. Поскольку подключенного к выходу отвода линии 13 задержки должен сниматься сигнал с опережением, управляющий код подается на мультиплексор 14 с инвертированных выходов разрядов счетчика 16, Элемент 15 задержки обеспечивает задержку выходного сигнала мультиплексора на его длительность.

Выходной сигнал ДДКД 3 поступает на вход линии 4 задержки С помощью линии 4 задержки, мультиплексора 5, элемента 6 задержки и блока 7 управления производится коррекция фазы выходного сигнала на величину дискрета 21Г/К в сторону, противоположную осуществляемой в управляемом , 1 ДДКД 2 под воздействием сигнала управления. Под действием импульса управления триггер 19 (фиг. 2 при коррекции фазы на отставание) или триггер 20 (при коррекции на опережение) переводится в состояние и выходной сигнал через элемент задержки 6, элемент И-НЕ 21 (22) поступает на вход реверсивного счетчика и изменяет его состояние На выход цифрового управляемого генератора коммутируется соседний отвод линии задержки 4, при этом фаза выходного сигнала изменяется на дискрет подстройки 21Т /К, а с учетом коррекции (одновременной) на входе - на дискрет подстройки, равный 21Г/КЗ .

Временные диаграммы (фиг. 3, 4) иллюстрируют процесс коррекции фазы выходного сигнала в цифровом управляемом генераторе.

При коррекции фазы выходного сигнала на опережение фаза сигнала задающего генератора 1 с помощью управляемого ДДКД 2 корректируется на отставание (фиг. 3), при этом положение импульса (фиг. 3 а) изменяется на величину и соответствует моменту-t,, что приводит к изменению временного положения вспомогательного сигнала (фиг. 3 б) и-выходного

сигнала, (фиг. 3 в). Следующий импульс задающего генератора 1 сформируется в момент tJ, вспомогательного ей:- нала - в момент t, а выходного сигнала - в момент t. Одновременная

коррекция временного положения (фазы) выходного сигнала на опережение на величину tgj,/K приводит к тому, что очередной импульс выходного сигнала занимает положение t.. Таким образом, коррекция . фазы выходного сигнала на опережение составляет величину 21Г/КЗ .

При коррекции фазы выходного сиг- нала на отставание (фиг. 4) фаза сигнала задающего генератора 1 коррек- тируется на опережение, а фаза выходного сигнала - на отставание.

Формула изобретения

5

0

0

5

а входы управления соединены с шиной управления, выход последнего из п делителей с дробным коэффициентом деления соединен с входом линии задержки с отводами.

деления содержит линию задержки с отводами, мультиплексор, элемент задержки, блок добавления-исключения импульсов, счетчик, причем вход и отводы линии задержки с отводами соединены с сигнальными входами мультиплексора, выход которого через последовательно соединенные элемент задержки и блок добавления-исключения импульсов соединен с входом счетчика, выходы разрядов которого подключены

LEmhC-I

к управляющим входам мультиплексора, выход которого является выходом управляемого делителя с дробным коэффициентом деления, вход линии задержки с отводами является входом управляемого делителя с дробным коэффициентом деления, вход управления блока добавления-исключения импульсов является входом управления управляемого делителя с дробным коэффициентом деления.

W I Ф

0(/г. 2

| Устройство синхронизации | 1975 |

|

SU644044A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-02-28—Публикация

1986-05-05—Подача