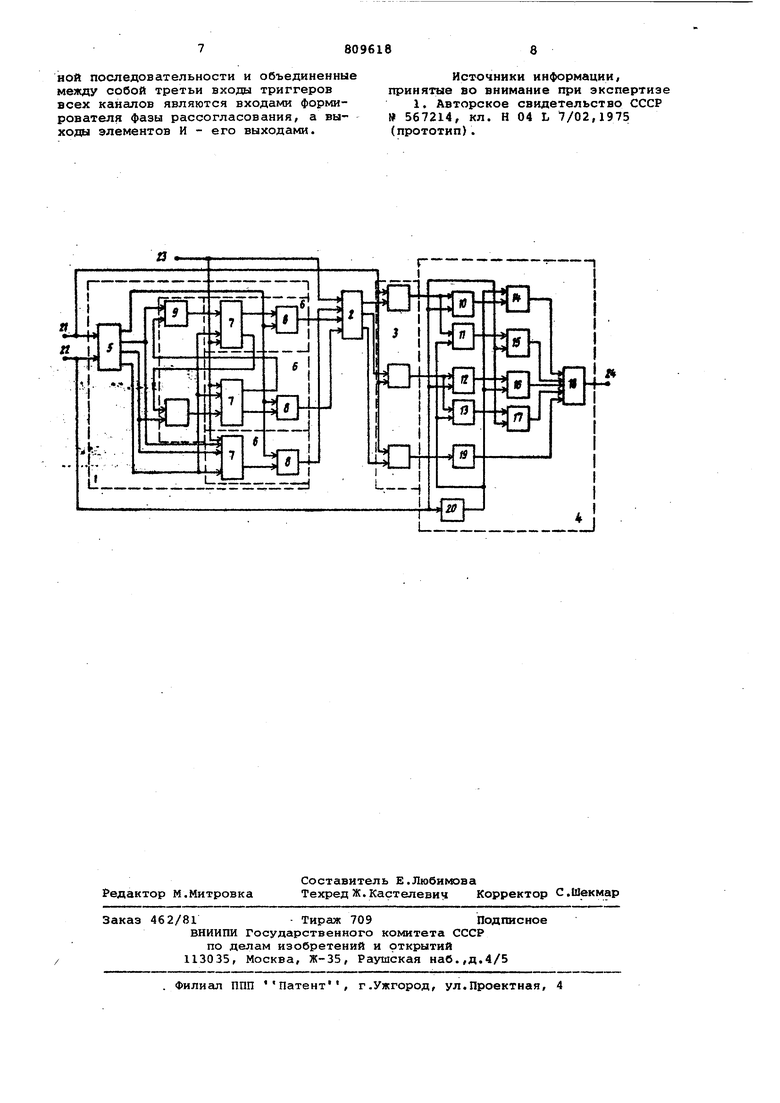

(54) УСТРОЙСТВО СИНХРОНИЗАЦИИ ЦИФРОВОЙ ПОСЛЕДОВАТЕЛЬНОСТИ ментов И трех каналов, при этом входы селектора входной последовательно ти и объединенные между собой третьи входы триггеров всех каналов являютс входами формирователя фазы рассогласования, а выходы элементов И - его выходами, На чертеже представлена структурная электрическая схема предлагаемого устройства. Устройство синхронизации цифровой последовательности содержит формирователь 1 фазы рассогласования, триггер 2, блок 3 элементов И, узел 4 фазирования, причем формирователь 1 фазы рассогласования содержит селектор 5 входной последовательности, три канала 6, каждый из которых состоит из триггера 7 и элемента 8 И, и блок 9 элементов И, а узел 4 фазирования содержит четыре триггера 1013, четыре элемента 14-17 И, элемент 18 ИЛИ, элемент 19 задержки и инвертор 20, а также шину 21 входной последовательности, шину 22 тактовой частоты, шину 23 установки исходного состояния и выходную шину 24, Устройство работает следующим образом. Входная последовательность и тактовая частота с соответствующих шин 21 и 22 поступают на входы формирователя 1 и подаются на входы селектора 5, с первых двух выходов которого сигналы несовпадений поступают на первые входы блока 9,а также на второй и третий нулевые входы триггера 7 третьего канала б. Сигнал совпадений с третьего выхода селектора 5 подается на единичный вход триггера 7 третьего канала 6 и вторые нулевые входы триггеров 7 первог и второго каналов 6. Сигнал совпадений четвертого выхода селектора 5 поступает на первые входы элементов 8 И каждого канала б, на вторые входы которых подаются разрешающие потенциалы с выходов триггеров 7 всех трех каналов 6. На вторые входы блока 9 элементов И подаются разрешающие потенциалы с нулевых плеч тригге ров 7 соответственно первого и второ го каналов 6. Установка нуля тригге ров 7 осуществляется после прохожде ния сигнала с шины 23. Сигнгшы с вы дов трех элементов 8 И управляют вх дами триггера 2, обеспечивающего вы дачу сигнала по одному из трех выхо дов в зависимости от подачи сигнало управления на соответствующий вход. Триггер 2 устанавливается в нулевое состояние при прохождении сигнала н второй вход с шины 23. Разрешающие потенциалы с выходов триггера 2 отк вают, элементы И блока 3 для прохождения входной последовательности с |шины 21 соответственно на первый, в 1рой и третий входы узла 4. Информация с первого входа узла 4 поступает на входы триггеров 10 и , со второго входа узла 4 - на входы триггеров 12 и 13 и с третьего входа узла 4 - на вход элемента 19 задержки. Входы триггеров 10 и 12 непосредственно, а триггеров 11 и 13 через инвертор 20 подключены к шине 22. Выходы триггеров 10-13 управляют первыми входами элементов 14-17 И,вторые входы элементов 14-16 И через инвер - . тор 20, а элементов 15 и 17 И непосредственно стробируются тактовой частотой с шины 22. Информация с выходов элементов 14-17 И и с выхода элемента 19 задержки через элемент 18 ИЛИ поступает на выходную шину 24. В начальный момент времени после прохождения сигнала с шины 23 триггеры 7 и 2 устанавливаются в нулевые состояния. Нулевое состояние триггера 2 разрешает прохождение информации с шины 21 через блок 3 на третий вход узла 4 и далэе через элемент 19 задержки и элементов ИЛИ на выходную шину 24. Нулевые состояния первого и второго триггеров 7 разрешают прохождение сигналов несовпадений с выходов селектора 5 через блок 9.Если входная последовательность отстает от тактовой частоты, сигнал, пройдя с первого выхода селектора 5 через открытый нулевым состоянием второго триггера 7 элемент И блока 9, установит триггер 7 первого канала б в единичное состояние, закрывающее элемент И блока 9 для возможного прохождения сигнала со второго, выхода селектора 5 и открывающее элемент 8 И первого канала б для прохождения сигнала с четвертого выхода селектора 5 на вход триггера 2, устанавливая последний в состояние, открывающее элемент И блока 3 для прохождения входной последовательности с шины 21 на первый вход узла 4, а элементы 8 И второго и третьего каналов 6 закрыты нулевыми потенциалами с единичных плеч триггеров 7. Элементы И блока 3 закрыты нулевыми потенциалами соответствующих плеч триггера 2. Информация с шины 21 поступает далее на входы двухтактных триггеров 10 и 11, в которых осуществляется ее.синхронизация соответственно прямой и инверсной тактовой частотой. Необходимость иметь два триггера 10 и 11 диктуется возможностью равенства длительности тактовой частоты и входной последовательности. При этом триггер 10 запоминает и синхронизирует значение входной последовательности при наличии единицы на шине 22, а триггер 11 - при наличии нуля. Подобное построение обеспечивает ёинхронизацию входной последовательности без возможной потери единичных символов при равенстве длительностей символов тактовой частоты и информа ции. Информация с выходов триггеров 10 и И поступает на элементы 14 и И, которые стробируются соответстве но инверсной и прямой тактовой частотой, Стробирование исключает воз.можность появления на выходе устрой ства ложных символов информации, во никающих при пропуске одним из триг геров 10 и 11 единичного символа ин формации при ее изменении в момент наличия нуля на входе. Сигналы с выходов элементов 14 и 15 И сумми руются элементом 18 ИЛИ и поступают на выход устройства - шину 24. Если входная последовательность начинает совпадат-ь с тактовой часто той, то единичное состояние триггер 7 третьего канала б открывает элемент 8 И для прохождения сигнала. Сигнал поступает на вход триггера 2 устанавливая его в состояние, откры вающее элемент И блока 3 для прохожд ния информации с шины 21 на третий вход узла 4 и далее через элемент 1 задержки, элемент 18 ИЛИ н.а выходную шину 24. Элементы 8 И закрыты нулевыми состояниями триггеров 7, а элементы И блока 3 - нулевыми потенциалами на соответствующих выходах триг гера 2. Элемент 19 задержки осуществляет задержку символов входной последовательности на время, равное длительности импульса тактовой частоты, обеспечивая тем самым синхронизацию входной последовательности по фиксированной точке тактовой частоты (ее заднему фронту). Если входная последовательность опережает тактовую частоту,то сигнал пройдя через открытый нулевым состо янием триггера 7 первого канала 6 элемент И блока 3, установит тригге 7 другого канала 6 в единичное состояние. На вход триггера 2 проходит сигнал, устанавливая его в состояние, открывающее элемент И блока 3 для прохождения входной последовательности с шины 21 на второй вход узла 4. Элементы 8 И закрыты нулевыми потенциалами с единичных плеч триггеров 7. Элементы И блока 3 закрыты нулевыми потенцис1лами соответствующих плеч триггера 2. Информация с шины 21 поступает далее на входы однотактных триггеров 12 и 13, .в которых осуществляется ее синхронизация соответственно прямой и инверсной тактовой частотой. Необходимость иметь два триггера 12 и 13 объясняется теми же причинами, что и для триггеров 10 и 11. при этом триггер 12 синхронизирует и запоминает значение входной последовательности при наличии единицы на шине 22, а триггер 13 - при наличии нуля. Информация с выходов триггеров 12 и 13 подается на элементы 16 и 17 И, которые стрсбируются соответственно инверсной и прямой тактовой частотой. Сигналы свыходов элементов 16 и 17 И суммируются элементом 18 ИЛИ и поступают на выход устройства шину 24. Формула изобретения 1.Устройство синхронизации цифровой последовательности, содержащее последовательно соединенные фор.мирователь фазы рассогласования и триггер, выходы которого через блок элементов И подключены к входам узла фазирования, отлича.ющееся тем, что, с целью повышения точности, первый вход формирователя фазы рассогласования подключен к вторым входам блока элементов И, а второй вход - к другому. входу узла фазирования. 2.Устройство по п.1, о т л и чающееся тем, что, узел фазирования выполнен в виде четырех триггеров, выходы которых через соответствующие элементы И подключены к входа 1 элемента ИЛИ, причем другой вход элемента ИЛИ соединен с выходом элемента задержки, вход инвертора соединен с входами первого и третьего триггеров и второго и четвертого элементов И, а выход подключен к вторым входам первого и третьего элементов И и входам второго и четвертого триггеров, при этом другие входы триггеров, вход элемента задержки и вход инвертора являются входами узла фазирования, а выход элемента ИЛИ его выходом. 3.Устройство ПОП.1, отличающееся тем, что формирователь фазы рассогласования состоит из селектора входной последовательности, трех каналов, каждый из которых состоит из последовательно соединенных триггера и элемента И, блока элементов И, причем первый и второй выходы селектора входной последовательности подключены соответственно к первым входам блока эле ентов И и первому и второму входам триггера третьего канала, третий вход которого соединен с третьим выходом селектора входной последовательности и первыми входами триггеров первого и второго каналов, другие выходы которых подключены к вторым входам блока элементов И, выходы которого подключены к вторым входам триггеров первого и второго каналов, причем четвертый выход селектора входной последовательности подключен к торым входам элементов И трех канаов, при этом входы селектора входной последовательности и объединенные между собой третьи входы триггеров всех каналов являются входами формирователя фазы рассогласования, а выходы элементов И - его выходами.

Источники информации, принятие во внимание при экспертизе

1. Авторское свидетельство СССР 567214, кл. Н 04 L 7/02,1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации фазы двух цифровых последовательностей | 1975 |

|

SU567214A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1774497A1 |

| Устройство для сопряжения электронно-вычислительной машины с каналом связи и периферийным устройством | 1983 |

|

SU1161948A1 |

| Селектор импульсов | 1977 |

|

SU746899A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| Устройство тактовой синхронизации с пропорциональным регулированием | 1978 |

|

SU731604A2 |

| Устройство для обмена информацией | 1981 |

|

SU1003064A1 |

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

Я

I

Авторы

Даты

1981-02-28—Публикация

1978-07-03—Подача