Изобретение относится к технике связи и может быть использовано в устройствах автоматической подстройки частоты.

По основному авт. св. № 314320 известно устройство тактовой синхронизации с пропорциональным регулированием при коэффициенте усреднения 2, содержащее задающий генератор, делитель частоты, узел управления коэффициентом деления, фазо вый дискриминатор и узел выделения фронтов, делитель частоты выполнен с дополнительным числом /С разрядов, при этом выход Д-го разряда делителя частоты подключен к входу фазового дискриминатора 1.

Однако такое устройство имеет невысокую помехоустойчивость.

Цель изобретения - повыщение помехоустойчивости.

Для этого в устройство тактовой синхронизации с пропорциональным регулированием при коэффициенте усреднения V, содержащее задающий генератор, делитель частоты, узел управления коэффициентом деления, фазовый дискриминатор и узел выделения фронтов, делитель частоты выполнен с дополнительным числом /С разрядов, при этом выход /С-го разряда делителя частоты подключен к входу фазового дискриминатора, введен временной селектор

входных сигналов, выход которого подключен к узлу выделения фронтов, а вход соединен с выходом задающего генератора, временной селектор входных сигналов вы5 полней в виде двух цепей, каждая из которых состоит из последовательно соединенных элементов И, счетчика п дешифратора, выход которого через инвертор подключен к входу элемента И, выходы дешифраторов обоих цепей подключены к входу триггера, причем второй вход элемента И второй цепи соединен с выходом инвертора, вход которого соединен с вторым входо.м элемента И первой цепи, причем второй

15 вход элемента И первой цепи, третьи входы элементов И и третий вход триггера, а также выход триггера являются соответственно входами и выходом временного селектора входных сигналов.

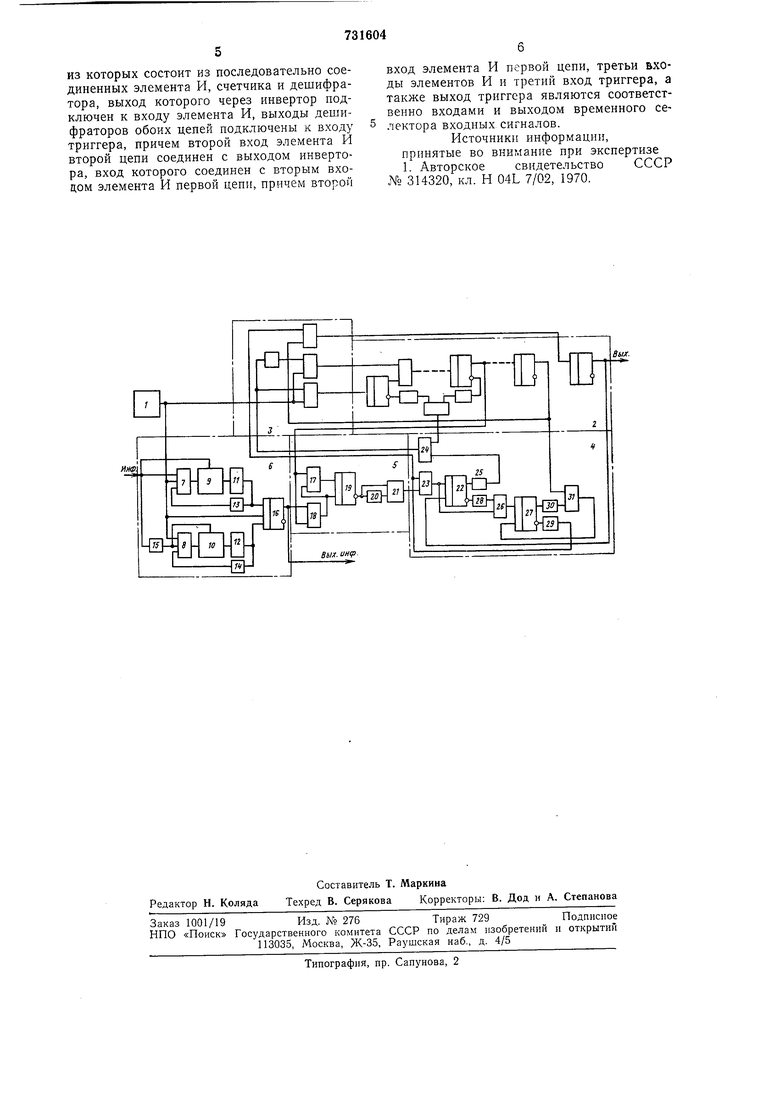

На чертеже дана структурная электрическая схема предложенного устройства.

Устройство содержит задающий генератор 1, делитель 2 частоты, узел 3 управления коэффициентом деления, фазовый дискриминатор 4, узел 5 выделения фронтов и временной селектор 6 входных сигналов, который состоит из элементов И 7, 8, счетчиков 9, 10, дешифраторов 11, 12, ннверто30 ров 13-15 и триггера 16.

Устройство работает следующим образом.

Импульсы с задающего генератора 1 с периодом повторения 6 поступают на делитель 2 с коэффициентом . На выходе делителя 2 вырабатывается последовательность стробирующих импульсов с периодом Т (Т - длительность элементарной посылки принимаемого сигнала), синфазная с фронтами принимаемого сигнала. Входной сигнал поступает в временной селектор 6, где производится оценка входного сигнала по длительности. В качестве временных меток используются импульсы задающего генератора 1. Емкости счетчиков 9, 10 и число, на которое собраны дешифраторы И, 12, определяются исходя из максимального значения длительности помехи. В отсутствие сигнала на входе счетчик 9 стоит в исходном состоянии, а со счетчика 10 снят сигнал «сброс. При появлении на входе элемента И 7 импульсных посылок со счетчика 9 снимается сигнал «сброс, а счетчик 10 устанавливается в исходное состояние. Счетчиком 9 производится подсчет импульсов задающего генератора 1 за время действия сигнала на входе, и, если этот сигнал по длительности превышает значение, установленное на счетчике 9, то на выходе дешифратора И появляется сигнал «1, который поступает на вход / триггера 16 и через инвертор 13 запирает вход элемента И 7, при этом импульсом с задающего генератора 1 производится запись «1 Е триггере 16. При снятии сигнала на входе включается счетчик 10, а счетчик 9 устанавливается в исходное состояние, на выходе дешифратора 12 появляется сигнал «О, который поступает на вход К. триггера 16 и через инвертор 14 запирает вход элемента И 8, при этом производится запись «О в триггере 16. Выход триггера 16 является выходом принимаемой информации. С выхода триггера 16 информация поступает в узел 5. В узле 5 формируются передние и задние фронты посылок принимаемого сигнала и подаются на фазовый дискриминатор 4, в котором сравнивается момент прихода импульса фронта -ti с узла 5 и момент прихода импульса с выхода делителя 2 (t). На выходе фазового дискриминатора 4 вырабатывается пачка из

t,-t

г -

импульсов, которые поступают на узел 3. При этом происходит добавление г импульсов на вход делителя 2. Кроме того, с линпи задержки фазового дискриминатора 4 на вход узла 3 поступает с приходом каледого фронта сигнал, вызывающий как бы исключение импульсов на входе делителя 2. Таким образом, в режиме синхронизма на выходе фазового дискриминатора 4 вырабатывается импульсов добавления, смещающих стробирующий импульс на время . На эту же величину происходит сдвиг стробирующего импульса вследствие исключения одного импульса на входе (п-1)-го разряда делителя 2.

Импульс с выхода Л-го разряда делителя 2 переписывает информацию с триггера 16 через элементы И 17 и 18 в триггер 19. Сигнал с триггера 19 непосредственно п через линию задержки 20 поступает на два входа полусумматора 21, на выходе которого образуется импульс фронта длительно6стью -, поступающий на фазовый дискриминатор 4.

Импульс с узла 5 поступает на триггер 22 через элемент И 23, в результате чего с выхода триггера 22 через линию задержки 24 подается разрешающий потенциал на

элемент И 25.

Элемент И 25 запирается при поступлении на триггер 22 стробирующего импульса с выхода делителя 2. При отсутствии рассогласования стробирующий импульс

расположен в середине принятой элементарной посылки. На элемент И 25 поступают с делителя 2 импульсы длительностью б и с периодом повторения 6-2. На выходе

Т

элемента И 25 появляется пачка из -

g.2

импульсов, где Гр - -интервал времени между импульсом фронта и следующим за ним стробирующим импульсом. Импульс фронта с элемента И 23 поступает через

элемент И 26 на установку триггера 27. На время Гр элемент И 26 блокируется подаваемым на него через линию задержки 28 потенциалом с триггера 22. Сигнал с триггера 27 через линию задержки 29 воздействует на узел 3, а через линию задержки 30 открывает элемент И 31. В результате этого очередной импульс с выхода (п-1)-го разряда делителя 2 поступает не на «-и разряд, а на сброс триггера 27.

Импульсы добавления с выхода элемента И 25 подаются на вход узла 3.

Высокая помехоустойчивость устройства достигается за счет введения временного селектора 6, позволяющего предварительно

контролировать входные сигналы по длительности.

Формула изобретения

1. Устройство тактовой синхронизации с пропорциональным регулированием по авт. св. № 314320, отличающееся тем, что, с целью повышения помехоустойчивости, введен временной селектор входных

сигналов, выход которого подключен к узлу выделения фронтов, а вход соединен с выходом задающего генератора.

2. Устройство по п. 1, отличающееся тем, что временной селектор входных сигналов выполнен в виде двух цепей, каждая

из которых состоит из последовательно соединенных элемента И, счетчика и дешифратора, выход которого через инвертор иодключен к входу элемента И, выходы дешифраторов обоих цепей подключены к входу триггера, причем второй вход элемента И второй цепи соединен с выходом инвертора, вход которого соединен с вторым вхоцом элемента И первой цепи, причем второй

вход элемента И первой цепи, третьи входы элементов И и третий вход триггера, а также выход триггера являются соответственно входами и выходом временного селектора входных сигналов.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 314320, кл. Н 04L 7/02, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ с ПРОПОРЦИОНАЛЬНЫМ РЕГУЛИРОВАНИЕМ | 1971 |

|

SU314320A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1254589A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Логический пробник | 1987 |

|

SU1525636A1 |

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

Авторы

Даты

1980-04-30—Публикация

1978-09-22—Подача