(54) УСТРОЙСТВО СИНХРОНИЗАЦИИ КАНАЛОВ СВЯЗИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации каналов связи | 1976 |

|

SU625315A1 |

| Устройство для фазовой автоподстройки частоты | 1977 |

|

SU680140A1 |

| Следящий измеритель частоты | 1978 |

|

SU766024A1 |

| Цифровая динамическая следящая система | 1980 |

|

SU890358A1 |

| Преобразователь сигнал-время | 1973 |

|

SU443478A1 |

| Устройство синхронизации | 1981 |

|

SU1053314A1 |

| Устройство измерения фазы | 1981 |

|

SU968767A2 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| Цифровой управляемый генератор | 1989 |

|

SU1748247A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2019 |

|

RU2713624C1 |

1

Изобретение относится к радистахнике и может быть использовано в устройствах синхронизации подвижных объектов в системах радионавигации и радиосвязи.

Известное устройство синхронизации каналов связи содержит последовательно соединенные приемопередатчик, блок выделения эталонного сигнала, первый дискриминатор, первый фильтрэкстраполятор и перестраиваемый генератор, а также генератор цифровых сигналов, выход которого подключен ко входу приемопередатчика 1.

Однако известное устройство имеет большое время повторной синхронизации.

Цель изобретения - уменьшение времени повторной синхронизации.

Поставленная цель достигается тем, что в устройство синхронизации каналов связи, содержащее последовательно соединенные приемопередатчик, блок выделения эталонного сигнала, первый дискриминатор, первый фильтр-экстрапап ятор и перестраиваемый генератор, а также генератор цифровых сигналов, выход которого подключен ко входу приемопередатчика, введены четыре переключателя, последовательно соединенные хронизатор, блок временной коррекции и первый блок задержки, а также второй и третий блок згшержки и последовательно соединенные второй дискриминатор и второй фильтр-экстраполятор, выход которого подключен к управляющим входам блоков задержек, при этом к nepBOisv входу второго дискриминатора через первый и второй

0 контакты первого переключателя подключены выход второго блока задержки и третий контакт второго переключателя, а к третьему контакту первого переключателя подключен выход первого блока задержки, выход генератора цифровых сигналов через третий блок задержки подключен ко входу второго блока задержки и через первый и второй контакты третьего переключателя

0 ко второму входу блока временной коррекции, причем второй выход приемопередатчика через первый и второй контакты второго переключателя подключен ко второму входу первого ди5скриминатора и через первый и второй контакты четвертого переключателя ко второму входу второго дискриминатора, а третий контакт четвертого переключателя соединен с первым входом

0 первого дискриминатора, при этом выход перестраиваемого генератора подключен ко входу генератора цифровых сигналов.

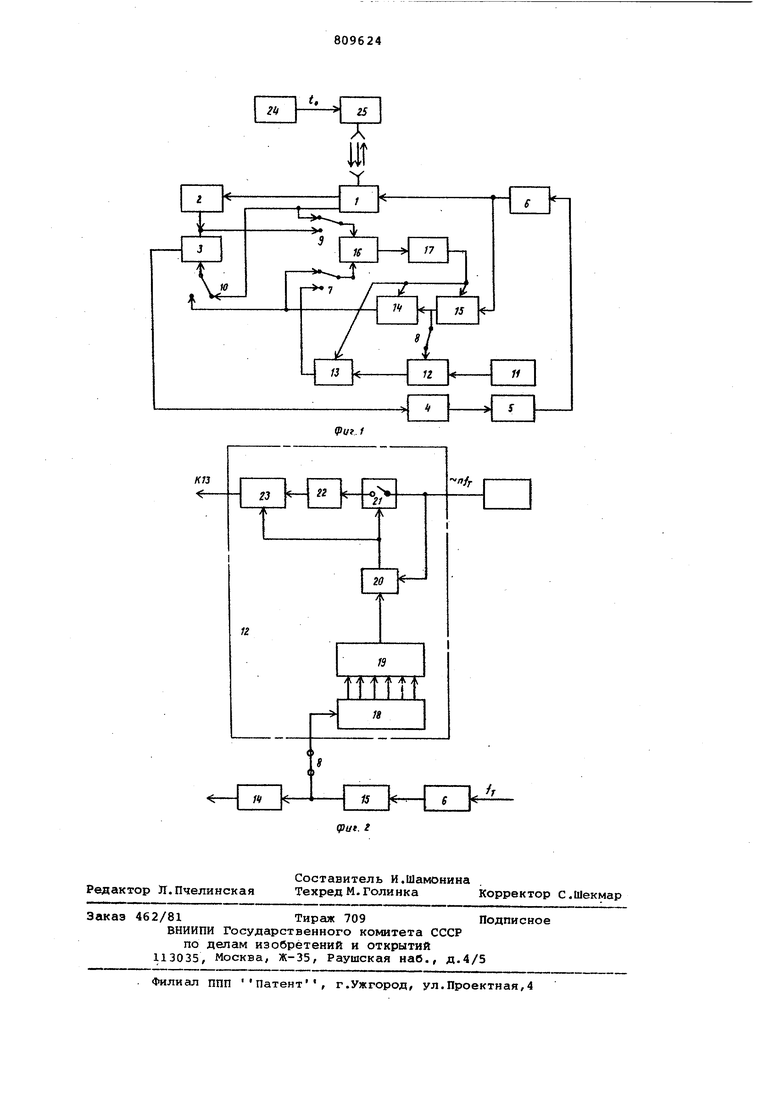

На фиг. 1 изображена структурная электрическая схема предлагаемого устройства; на фит.2 - структурная электрическая схема блока временной коррекции.

Предлагаемое устройство содержит , приемопередатчик 1, блок 2 выделения эталонного сигнала, первый дискриминатор 3, первый фильтр экстраполятор 4, перестраиваемый генератор 5, генератор б цифровых сигналов, переключатели 7 - 10, хронизатор 11, блок 12 временной коррекции, блоки 13-15 задержки, второй дискриминатор 16, второй фильтр-экстраполятор 17.

Блок 12 временной коррекции содержит регистр сдвига 18, дешифратор 19, схему совпадения 20, переключатель 21, делитель 22, генератор 23 цифровых сигналов.

Станция- ретранслятор включает в себя опорные часы 24 и пpиe vюпepeдатчик 25. .

Устройство работает следующим образом.

Временной сигнал,опорных часов 24 излучается приемопередатчиком 25 станции ретранслятора и принимается приемопередатчиком 1. Принятый сигнал с выхода блока 2 выделения эталонного сигнала как опорный поступает на вход первого дискриминатора 3. Сигнал управления с выхода дискриминатора 3 через фильтр-экстраполятор 4 поступает на управляющий вход перестраиваемого генератора 5, изменяя его фазу (частоту) и соответственно фазу сигнала генератора 6 цифровых сигналов, который излучается приемопередатчиком 1, переизлучается приемопередатчиком 25, принимается приемопередатчиком 1, через переключатель 10 поступает на другой вход дискриминатора 3, замыкая кольцо автоматического регулирования фазы ретранслированного цифрового сигнала.

При синхронизации кольца фаза ретранслированного цифрового сигнала Рр и фаза эталонного сигнала Чд на входах дискриминатора 3 равны между собой, а учитьдаая одинаковую задержку их распрбстранемия от приемопередатчика 25, это равенство (с точностью до аппаратуршйх ошибок) сохраняется и на выходе приемопередатчика 25« Кроме того, цифровой сигнал чере приемопередатчик 1, приемопередатчик 25, приемопередатчик 1 н переключатель i9 поступает на один вход, а через блоки 15 и 14 задержки и переключатель 7 - на другой вход дискриминатора 16. Сигнал рассогласования с выхода дискриминатора 16 через фильтр-экстраполятор 17 поступает . на управляющие входы идентичных блоков 13 - 15 задержки, замыкая тем

самлм кольцо авторегулирования. При синхронизации сигнал рассогласования на выходе дискриминатора 16 стре№1тся к нулю, когда фазы сигналов на его входах равны, т.е. при выполнении равенства

.

где Т - время задержки блока 14; время задержки блока 15; tp- время однопутевого распространения сигнала;

время задержки в приемопередатчике 25;

рр - время сигнала рассогласованИя.

Учитывая, что , имеем

W

л., at - где

Таким образом, временной сигнал на выходе блока 15 задержки с точностью до половинного значения суммарной аппаратурной ошибки соответствует моменту излучения этого же сигнала приемопередатчиком-25, а следовательно, временному сигналу to опорных часов24. Этот сигнал

через переключатель 8 поступает на управляющий вход блока 12 временной коррекции, обеспечивая синхронизацию временной шкалы хронизатора 11.

Блок 12 временной коррекции работает следующим образом.

Цифровой сигнал через переключатель 8 поступает на регистр 18 сдвига, тактовая частота которого соответствует тактовой частоте входного сигнала. Выходы разрядов регистра поступают на дешифратор 19, на выходе которого выделяется импульс в момент, когда регистр сдвига будет заполнен определенным сегментом последовательности цифрового сигнала. Импульс с

выхода дешифратора 19 поступает на схему совпадения 20, на другой вход которой с выхода хронизатора 11 поступают тактовые импульсы с частотой следования -nff-.

При совпадении импульсов замыкаются контакты переключателя 21, при этом тактовыми импульсами хронизатора 11 запускается делитель 22, и все разряды генератора 23 цифровых сигналов устанавливаются в определенное состояние, например все единицы. Далее тактовые импульсы с частотой с выхода делителя запускают генератор 23 цифровых сигналов. Таким образом осуществляется моментная привязка временной шкалы кронштейна

к временному сигналу на выходе блока 15 задержки. По окончании сеанса связи переключатель 8 выключается и в дальнейшем поддерживается автономный режим работы генератора 23 цифровых сигналов от тактовых импульсов хронизатора 11.

Повторное включение сеанса связи производится установкой переключателей 7-10 в исходное положение, при этом переключатель 21 размыкается и блок 12 временной коррекции переходит в исходное состояние.

По окончании сеанса связи выключается излучение сигнала приемопередатчика 1, а все переключатели 7-10 переводятся в другое положение. При этом обеспечивается отслеживание изменяющейся задержки эталонного сигнала .

Работа в этом режиме происходит следующим образом.

Временной сигнал с выхода блока 2 выделения эталонного сигнала поступает через переключатель 9 на вход дискриминатора 16, на другой вход которого через переключатель 7 и блок 13 задержки поступает скорректированный по фазе в блоке 12 сигнал хрониэатора 11. Первоначально значение времени задержки блоков 13 и 14 соответствует времени однопутевого распространения сигнала от станции ретранслятора до станции связи, и фазы сигналов на их выходах равны фазе эталонного сигнала, поступающего на другие входы дискриминаторов 3 и 16. В дальнейшем, например, при увеличении задержки эталонного сигнала на величину дЧ за счет увеличения расстояния между станцией связи и станцией ретранслятора, происходит отслеживание этого рассогласования кольцом авторегулирования, Образованным дискриминатором 16, фильтром-экстраполятором 17 и блоком задержки 13. При этом сигнал рассогласования одновременно увеличивает и время задержки -блоков 14 и 15 и фаза сигнала на входе дискриминатора 3 изменится на +2. Кольцо авторегулирования фазы (частоты), образованное дискриминатором 3, фильтром-экстраполятором 4, перестраиваемом генератором 5, генератором цифровых сигналов и последовательно включенными блоками задержки 15 и 14, изменяет фазу сигнала на выходе генератора 6 цифровых сигналов таким образом, чтобы компенсировать возникшее рассогласование,, т.е. на , При этом временной сигнал на выходе генератора б, задержанный на время однопутевого распространения, совпадает с временными метками опорных часов 24 с точностью, соответствующей ошибке хранения шксшы времени хронизатора 11.

Изобретение позволяет уменьшить время повторной синхронизации.

Формула изобретения

Q Устройство синхронизации каналов связи, содержащее последовательно соединенные приемопередатчик, блок выделения эталонного сигнала, первый дискриминатор, первый фильтр-экстраполятор и перестраиваемый генератор,

15 а также генератор цифровых сигналов, выход которого подключен ко входу приемопередатчика, отличающееся тем, что, с целью уменьшения .. времени повторной синхронизации,

0 в неговведены четыре переключателя, последовательно соединенные хронизатор, блок временной коррекции и первый блок задержки, а также второй и третий блоки задержки и последова5 тельно соединенные второй дискриминатор и второй фильтр-экстраполятор, выход которого подключен к управляющим входам блоков задержек, при этом к первому входу второго дискримина0 тора через первый и второй контакты первого переключателя подключены выход второго блока задержки и третий контакт второго переключателя, а к третьему контакту первого переключа теля подключен выход перво.го блока задержкиJ выход генератора цифровых сигналов через третий блок задержки подключен ко входу второго блока задержки и через первый и второй контакты третьего переключателя ко второ0

му входу блока временной коррекции, причем второй выход приемопередатчика через первый и второй контакты второго переключателя подключен ко второму входу первого дискриминатора

5 и через первый и второй контакты четвертого переключателя - ко второму . входу второго дискриминатора, а третий контакт четвертого переключателя соединен с первым входом первого

0 дискриминатора, при этом выход перестраиваемого генератора подключен ко входу генератора цифровых сигналов.

Источники информации, принятые во внимание при экспертизе

5 1 Авторское свидетельство СССР 625315, кл. Н 04 L 7/04, 1976.

Авторы

Даты

1981-02-28—Публикация

1979-03-16—Подача