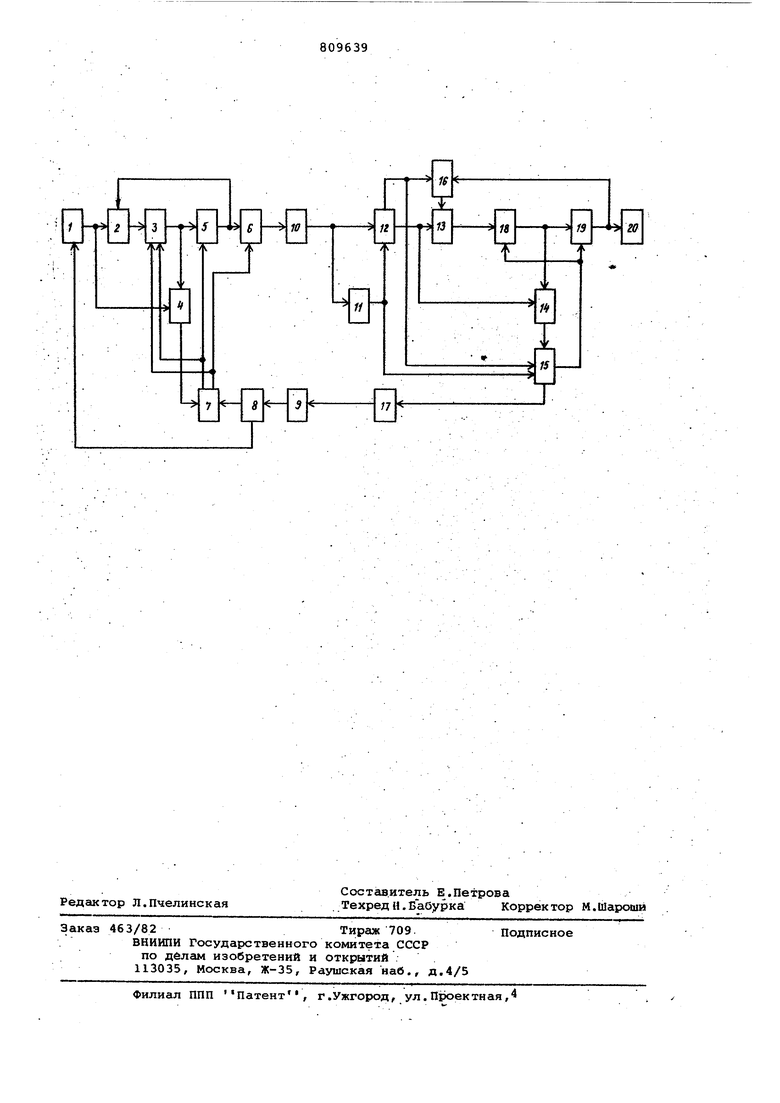

Изобретение относится к. связи и может использоваться, для организации; обмена информацией между двумя пункт ми. Известна система для передачи и приема данных с решающей обратной связью, содержащая на передающей сто роне последовательно соединенные дат чик информацииi элемент ИЛИ, накопитёль и элемент И, выход которого под лючен ко второму входу элемента ИЛИ, и последовательно соединенные канал обратной связи, блок дешифрирования сигналов обратной связи и блок управ ления, выход которого подключен ко вторым входам накопителя и элемента И а. также кодирукиций блок, выход кот ого оединен со входом аискретногр канала связи; на приемной стороне - декодирующий блок, первый вход -которого соединен с выходом дискретного канала связи, решающий блок, выход которого подключен к пер вому входу блока управления, выходы которого соединены со входом блока формирования сигналов обратной связи и первыми входами накопителя и элемента И, второй вход и выход которог соединены соответственно с вькодом накопителя и входом получателя мации, при этом выход блока формиро|вания сигналов обратной связи подклю чан ко входу обратного канала связи l . Однако известная система имеет сравнительно невысокую помехоустой-. чивость. Цель изобретения - повышение помехоустойчивости. Поставленная цель достигается .тем, что на передающей стороне введен ком-. паратор, входы которого соединены с выходами накопителя .и датчика информации, ко входу которого подключен дополнительный выход блока дешифрирования сигналов обратной связи, а выход компаратора соединен со ВТОЕЯЛМ входом блока управления, дополниггельный выход которого подключен к третьему входу накопителя к первому входу кодирующего блока, рторой t вход которого соединен с выходом элемента И на приемной стороне введены элемент ИЛИ, ключ и компаратор, выход которого подключен ко второму входу блока управления, третий которого соединен с первьил выходом декодирующего блока и первым входом ключа, второй вход и выход которого соединены соответственно с выходом элемента и и первым входом элемента ИЛИ, второй вход которого соединен со вторым выходом декодирующего блока и первым входом компаратора, ко второму входу которого подключен выход накопителя, вход которого соединен с выходом элемента ИЛИ, причем второй вход декодирующего блока соединен с выходом решающего блока. На чертеже приведена структурная j электрическая схема предлагаемой сиетемы. Система для передачи и приема дан ных с решающей обратной связью содер жит на передающей стороне датчик 1 информации, элемент 2 ИЛИ, накопител 3, компаратор 4, элемент 5 И, кодирующий блок б, блок 7 управления, блок 8 дешифрирования сигналов обрат ной связи, канал 9 обратной связи, дискретный канал 10 связи, а на прие ной стороне - решающий блок 11, деко дирующий блок 12, элемент 13 ИЛИ, компаратор 14, блок 15 управления, ключ 16, блок 17 формирования сигналов обратной свяэи, накопитель 18 элемент 19 И и получатель 20 информации. Система работает следующим образом. Сообщения от датчика 1 поступают на первый вход элемента- 2 ИЛИ и с его выхода - на дервый вход накопите ля 3.Сообщение,поступающее в накопитель 3,сдвигает на его выход нулевую (если до этого момента информация в нем отсутствовала) информацию,котора приходит на входы компаратора 4 и эл мента 5 И. Одновременно на другой вход компа ратора 4 с выхода датчика 1 поступае первое сообщение. В результате сравнения компаратор 4 вырабатывает сигнал несовпадение, поступающий на второй вход блока 7. Блок 7 по этому сигналу разрешает прохождение первог сообщения из накопителя 3 через эле.мент 5 И в кодирующий блок 6 и через элемент 2 ИЛИ на вход накопителя 3 для перезаписи.Кодирующий блок б пре разует сообщение в кодовую комбинацию, которая поступает в дискретный канал 10. С выхода дискретного канал 10 кодовая комбинация поступает на входы дeкoдйiiэyющeгo блока 12 и решаю щего блока 11. Решающий блок 11 вырабатывает сигналы Верно или Неверно , поступающие на йервый вход блока 15 и на второй вход декодирующего блока ,12. По сигналу Неверно декодирую щий блок 12 стирает принятую кодов комбинацию, а блок 15 выдает в блок 17 сигнал на формирование и выдачу:, в канал 9 комбинации Запрос, Пос ледняя поступает на вход блока 8, с выхода которого сигнал З апррс поступает на вход блока 7. Блок 7 о сигналу Запрос разрешает повторное прохождение первого сообщения из накопителя 3 через соответствуюие узлы системы в дискретный канал 10. По сигналу Верно со второго выхода декодирующего блока 12 декоированное сообщение через элемент 13 ИЛИ поступает в накопитель 18 и на первый вход компаратора 14. Одновременно на первом выходе декодирующего блока 12 появляется сигнал, котррый открывает ключ 16, а также поступает на третий вход блока 15. Если до этого момента информация в накопителе 18 отсутствует, то в результате сравнения на выходе компаратора 14 появляется сигнал Несовпадение, который поступает на второй вход блока 15. Последний разрешает по сигналу прохождение первого сообщения через элемент 19 И к получателю 20 и через ключ 16 и элемент 13 ИЛИ - на перезапись в накопитель 18 . По сумме сигналов Верно и Несовпадение блок 15 выдает в блок 17 сигнал на формирование комбинации Подтверждение, которая через канал 9 принимается блоком 8. С выхода блока 8 сигнал Подтверждение поступает в датчик 1, разрешая выдачу второго сообщения. Второе сообщение вьвдвигает на вход компаратора 4 первое сообщение из накопителя 3 в то время, как на другой вход компаратора 4 поступает второе сообщение непосредственно из датчика 1. Если второе сообщение одинаковое с первым, на выходе компаратора 4, а следовательно, и на втором входе блока 7, появляется сигнал Совпадение, по которому на дополнительном выходе блока 7 формируется сигнал на стирание информации в накопителе 3 и формирование в кодирующем блоке 6 специальной кодовой комбинации х из числа размещенных. Последняя, аналогично предыдущей кодовой комбинации, через дискретный канал 10 поступает на входы решающего 11 и декодирующего 12 блоков. Таким образом, в результате выдачи датчиком 1 подряд двух одинаковых сообщений в дискретный канал 10 не посылаются подряд две одинаковые кодовые комбинации. Рещающий блок 11 и декодирующий блок 12 обрабатывает полученную кодовую комбинацию X. Если решающий блок 11 выдает сигнал Неверно, то работа системы аналогична ранее рассмотренной ее работе по сигналу Неверно. Если роиающий блок 11 выдает сигнал Верно а декодирующий блок 12 выдает сигнал о приеме комбинации X, то на первом выходе декодирующего блока 12 возникает сигнал, соответствующий сообщению X, по которому ключ 16 закрьшается. Вто рой выход декодирующего блока 12 по сообщению X остается закрытым. По сягналам Верно и X блок 15 разре шает прохождение записанного первого сообщения из накопителя 18 через элемент 19 И получателю 20. Так как ключ 16 при этом закрыт, то перезапись информации в накопитель 18 не происходит. Сигнсш Подтверждение формируется и выдается в канал 9 и обрабатывается на передающей стороне так же, как и в рассмотренном выше случае. Таким образом, в результате выдачи получателю 20 второго сообщения ; одинакового с перзам, приемная часть системы находится в том же состоянии что и перед выдачей первого сообщения Если в дальнейшем датчиком 1 выдается третье сообщение, то оно обрабатывает-20

ся TciK же,.как и первое, а четвертое, если оно одинаково с третьим, обрабатывается как и второе, и т.д. Любое отличное от предыдущего сообщение обрабатывается, как и первое сообщение. При трансформации сигнала Лодтверзедение в Запрос с передающей стороны повторно посылается ранее выданная кодовая комбинация.При этсм на первый и второй входы компаратора 14 поступают одинаковые сообщения и он Кащаёт в блок 15 сигнал Совпадение. Из решсшзщего блока 11 поступает сюда же сигнал Верно. По этим сигналам блок 15 выдает в блок 17 сигнал на выдачу сигнала подтверждение. На вторые входы накопителя 18 и эл мента 19 И сигнсш неподается, и сооб щение в получатель 20 не поступает, т.е. вставка информации исключается. Предлагаемая система дЛя передачи и приема данных обладает высокой эффективностью, так как при ее использо вании вероятность ошибочного приема уменьшается на несколько порядков. Формула изобретения Система для передачи и приема данных с решающей обратной связью, содержащая на передающей стороне последовательно соединенные датчик информа ции, элемент ИЛИ, накопитель и эле.мент И, выход которого подключен ко

ратного канала овяэи, о т л и ч а ющ а я с я тем, что, с целью повышеция помехоустойчивости, в нее на пер дающей стороне введен компаратор, вховторому входу элемента ИЛИ, и последовательно соединенные канал обратной связи, блок дешифрирования сигналов обратной связи и блок управления, выход которого подключен ко вторым входам накопителя и злеменфа И, а также кодирующий блок, выход которого соединен со йходом дискретного канала связи; на приемной стороне - декодирующий блок, первый вход которого соединен с выходом дискретного канала связи, рещающий блок, выход которого подключен к первому входу блока управления, выходы которого соединены со входом блока формирования сигна -. лов обратной связи и первыми входами накопителя и элемента И, второй вход и выход которого соединены соответственно с выходом накопителя и входом получателя информации, при этом выход блока формирования сигналов об- . ратной связи подключен ко входу обДы которого соединены с выходами накопителя и датчик.а информации, ко входу которого подключен дополнительный выход блока дешифрирования сигналов обратной связи, а выход компаратора соединен со вторым входом блока управления, дополнительный выход которого подключен к третьему входу накопителя и первому входу кодирующего блока, второй вход которого соединен с выходом элемента И; на приемной стороне введены элемент ИЛИ, ключ и компаратор, выход подключен ко второму входу блока управления, третий вход которого соединен с первым выходом декодирующего блока и первым входом ключа, второй вход и выход которого соединены соответственно с выходом элемента И и первым входом элемента ИЛИ, второй вход которого соединен со s-roftat выходом декодирующего блока и первым входом компаратора, ко второму входу которого подключен выход нгисопителя, вход которого соединен с выходом элемента ИЛИ,причем второй вход декодирующего блока соединен с выходом решающего блока. Источники информации, принятые во внимание при экспертизе 1. Пуртов Л.П. Элементы теории передачи дискретной информации, Н., Связь, 1972, с.161-167, 185-191 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для передачи и приема данных с решающей обратной связью | 1978 |

|

SU734893A1 |

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью | 1977 |

|

SU660288A2 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С МОНОКАНАЛОМ | 1991 |

|

RU2032213C1 |

| Устройство сопряжения ЭВМ с общим каналом связи | 1988 |

|

SU1668980A1 |

| Устройство передачи и приема дискретной информации | 1989 |

|

SU1646066A1 |

| Устройство для приема двоичных сигналов телеуправления | 1977 |

|

SU708391A1 |

| Устройство для исправления ошибок в кодовой комбинации | 1977 |

|

SU634469A1 |

| Адаптивное устройство для анализаКОдОВыХ КОМбиНАций B СиСТЕМАХ пЕРЕ-дАчи диСКРЕТНыХ СООбщЕНий C РЕшАю-щЕй ОбРАТНОй СВязью | 1979 |

|

SU809613A1 |

| Устройство для предотвращения ошибок | 1975 |

|

SU716057A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С ОБШИМ КАНАЛОМ СВЯЗИ | 1995 |

|

RU2103730C1 |

Авторы

Даты

1981-02-28—Публикация

1979-04-13—Подача