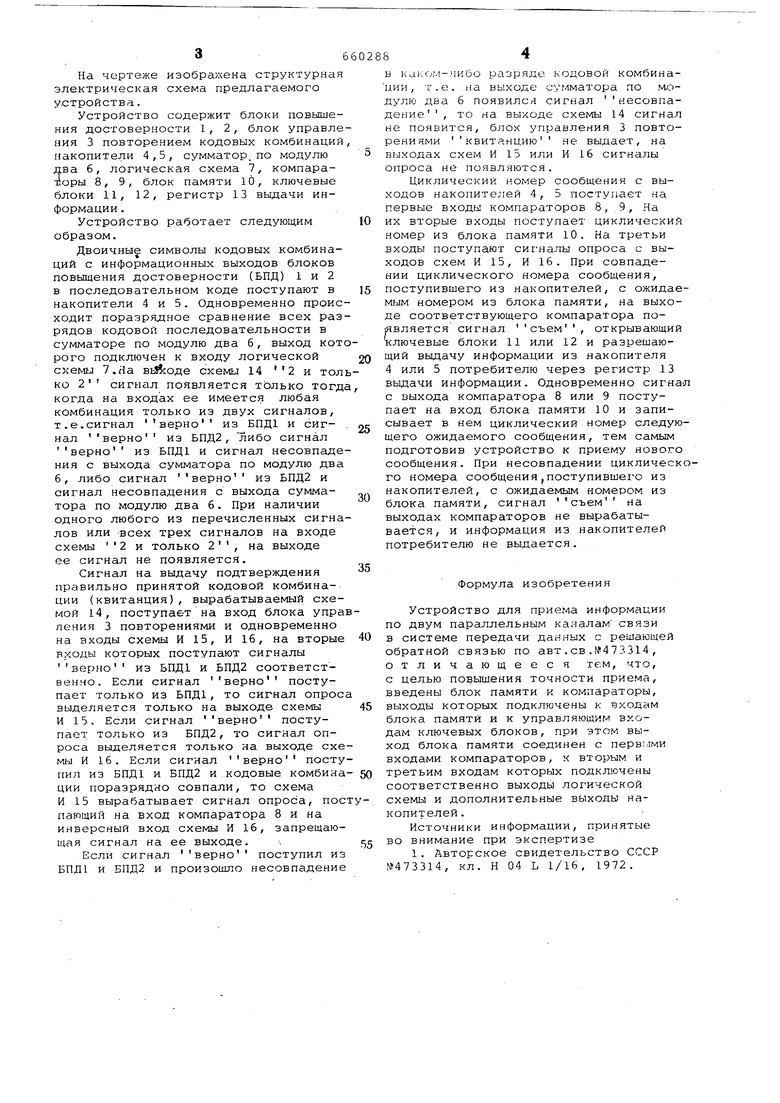

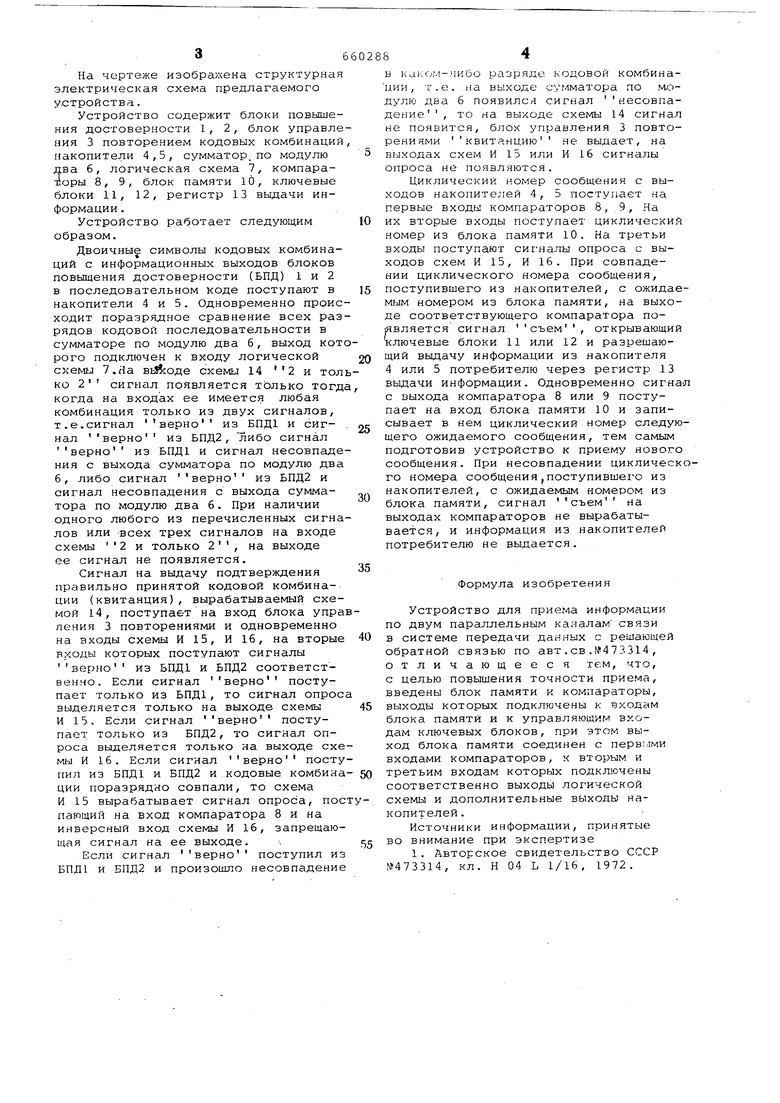

На чертеже изображена структурна электрическая схема предлагаемого устройства. Устройство содержит блоки повыше ния достоверности 1, 2, блок управл ния 3 повторением кодовых комбинаци накопители 4,5, сумматор.по модулю два б, логическая схема 7, компараторы 8, 9, блок памяти 10, ключевые блоки 11, 12, регистр 13 выдачи информации . Устройство работает следующим образом. Двоичные символы кодовых комбинаций с информационных выходов блоков повышения достоверности (ЬПД) 1 и 2 в последовательном коде поступают в накопители 4 и 5. Одновременно проис ходит поразрядное сравнение всех раз рядов кодовой последовательности в сумматоре по модулю два б, выход кот рого подключен к входу логической схемы 7.Ла схемы 14 2 и тол ко 2 сигнал появляется только тогд когда на входах ее имеется любая комбинация только из двух сигналов, верно из БПД1 и сигт.е.сигнал из БПД2, либо сигнал верно из БПД1 и сигнал несовпаде ния с выхода сумматора по модулю два б, либо сигнал верно из ЬПД2 и сигнал несовпадения с выхода сумматора по модулю два б. При наличии одного любого из перечисленных сигна лов или всех трех сигналов на входе схемы 2 и только 2, на выходе ее сигнал не появляется. Сигнал на выдачу подтверждения правильно принятой кодовой комбинации (квитанция), вырабатываемый схемой 14, поступает на вход блока упра ления 3 повторениями и одновременно на входы схемы И 15, И 16, на вторые входы которых поступают сигналы верно из ЬПД1 и ЬПД2 соответственно. Если сигнал верно поступает только из БПД1, то сигнал опрос выделяется только на выходе схемы И 15. Если сигнал верно поступает только из БПД2, то сигнал опроса вьщеляется только на выходе схе мы И 16. Если сигнал верно посту пил из БПД1 и БПД2 и кодовые комбина ции поразрядно совпали, то схема И 15 вырабатывает сигнал опроса, по пающий на вход компаратора 8 и на инверсный вход схемы И 16, запрещаю щая сигнал на ее выходе. , Если сигнал верно поступил и БПД1 и БПД2 и произошло несовпадени в ка1чом-. разряде кодовой комбинации, т.е. на выходе сумматора по модулю два б появился сигнал несовпадение , то на выходе схемы 14 сигнал не появится, блок управления 3 повторениями квитанцию не выдает, на выходах схем И 15 или И 16 сигналы опроса не появляются. Циклический номер сообщения с выходов накопителей 4, 5 nocTyriaeT яа первые входы компараторов 8,9, На их вторые входы поступает циклический номер из блока памяти 10. На третьи входы поступают сигналы опроса с выходов схем И 15, И 16. При совпадении циклического номера сообщения, поступившего из накопителей, с ожидаемым номером из блока памяти, на выходе соответствующего компаратора по1является сигнал съем , открывающий Ключевые блоки 11 или 12 и разрешающий выдачу информации из накопителя 4 или 5 потребителю через регистр 13 выдачи информации. Одновременно сигнал с выхода компаратора 8 или 9 поступает на вход блока памяти 10 и записывает в нем циклический номер следующего ожидаемого сообщения, тем самым подготовив устройство к приему нового сообщения. При несовпадении циклического номера сообщения,поступившего из накопителей, с ожидаемым номером из блока памяти, сигнал съем на выходах компараторов не вырабатывается, и информация из накопителей потребителю не выдается. Формула изобретения Устройство для информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью по авт.ев.№473314, отличающеес я тем, что, с целью повышения точности приема, введены блок памяти и компараторы, выходы которых подключены к входам блока памяти и к управляющим входам ключевых блоков, при этом выход блока памяти соединен с первыми входами компараторов, к вторым, и третьим входам которых подключены соответственно выходы логической схемы и дополнительные выходы накопителей . Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР №473314, кл. Н 04 L 1/16, 1972.

И

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решаюшей обратной связью | 1977 |

|

SU657635A2 |

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью | 1979 |

|

SU866767A2 |

| Система для передачи и приема данныхС РЕшАющЕй ОбРАТНОй СВязью | 1979 |

|

SU809639A1 |

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью | 1981 |

|

SU1008918A2 |

| Устройство для приема информации по двум параллельным каналам связи в системе передачи данных с решающей обратной связью | 1977 |

|

SU655081A2 |

| Устройство для приема информации по двум параллельным каналам связи в системе для передачи данных с решающей обратной связью | 2018 |

|

RU2696329C2 |

| Устройство для приема информации по двумпАРАллЕльНыМ КАНАлАМ СВязи B СиСТЕМЕ дляпЕРЕдАчи дАННыХ C РЕшАющЕй ОбРАТНОй СВязью | 1979 |

|

SU836806A2 |

| Устройство для передачи и приема дискретной информации с коррекцией ошибок | 1988 |

|

SU1578825A2 |

| Устройство для приема информации по двум параллельным каналам связи | 1979 |

|

SU873437A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ С ПОВЫШЕННОЙ ДОСТОВЕРНОСТЬЮ | 2013 |

|

RU2530335C1 |

Авторы

Даты

1979-04-30—Публикация

1977-07-01—Подача