Поставленная цель достигается тем, что в адаптивное устройство для анализа кодовых комбинаций в системах передачи дискретных сообщений с решающей обратной связью, содержащее блок обнаружения ошибок, сигнальный вход которого объединен со входом jiepBoro ключа, выходы которого под1слючены. соответственно к первому входу накопителя и к первому входу первого блока сравнения, второй вход которого соединен с первым выходом накопителя, а выход первого бцока сравнения подключен к одному из входов блока управления, соединенного со счетчиком блокировки, ко входам которого подключены соответственнЬ выход блока обнаружения ошибок и выход дешифратора, ко входу которого подключен второй выход накопителя, третий выход которого подключен ко входу второго ключа, к управляющему входу которого и ко второму входу накопителя подключен первый выход блока управления, а выход второго ключа подключен к одному из входов эледтанта ИЛИ, другой вход которого соединен с выходом третьего ключа, к информационному входу которого подключен первый выход накопителя, а-к управляющему входу - подключен второй выход блока управления и третий вход накопителя, четвертый вход которого соединен с выходом первого элемента И, к одному из входов которого подключен второй выход первого блока сравнения, а к другому входу выход элемента Пирса, ко входам которого подключен выход блока обнаружения ошибок непосредственно и через накопитель ошибок, выход счетчика блокировки подключен к одному из входов второго элемента И, к другому входу которого подключен выход дешифратора, а выход второго элемента И подключен к пятому входу накопители, введены последовательно соеди ненные сигнализатор пакетов ошибок, счетчик пакетов ошибок, блок определения разностного сигнала и второй блок сравнения, к другому входу которого подключен выход порогового блок а также блок памяти, включенный между выходом счетчика пакетов ошибок и другим входом блока определения разно тного сцгнала, при этом к первому вхбду сигнализатора пакетов ошибок и к другому входу блока памяти подключен выход накопителя ошибок, к двум другим входам сигнализатора пакетов ошибок подключены соответственно выход первого блока сравнения и выход блока обнаружения ошибок, выход второго блока сравнения подключен к соответствующему входу блока управления, третий выход которого подключен к шестому входу накопителя.

При этом накопитель состоит из блока регистров, первый выход которого через последовательно соединенные первый ключ и первый элемент ИЛИ подключен к первому входу блока регистров , а другие выходы блока регистров через последовательно соединенные блок вентилей, второй ключ и второй элемент ИЛИ подключены ко второму входу блока регистров, при этом дру1ГОЙ выход первого ключа подключен к другому входу второго элемента ИЛИ, а соответствующий выход блока регистров, подключен к другому входу первого элемента ИЛИ, причем соответствующие входы блока регистров, первого ключа и блока вентилей, являются соответственно первым, вторым, третьим, четвертым, пятым и шестым входами накопителя, а соответствующие выходы блока регистров и блока вентилей - соответственно первым, вторым и третьим выходами накопители.

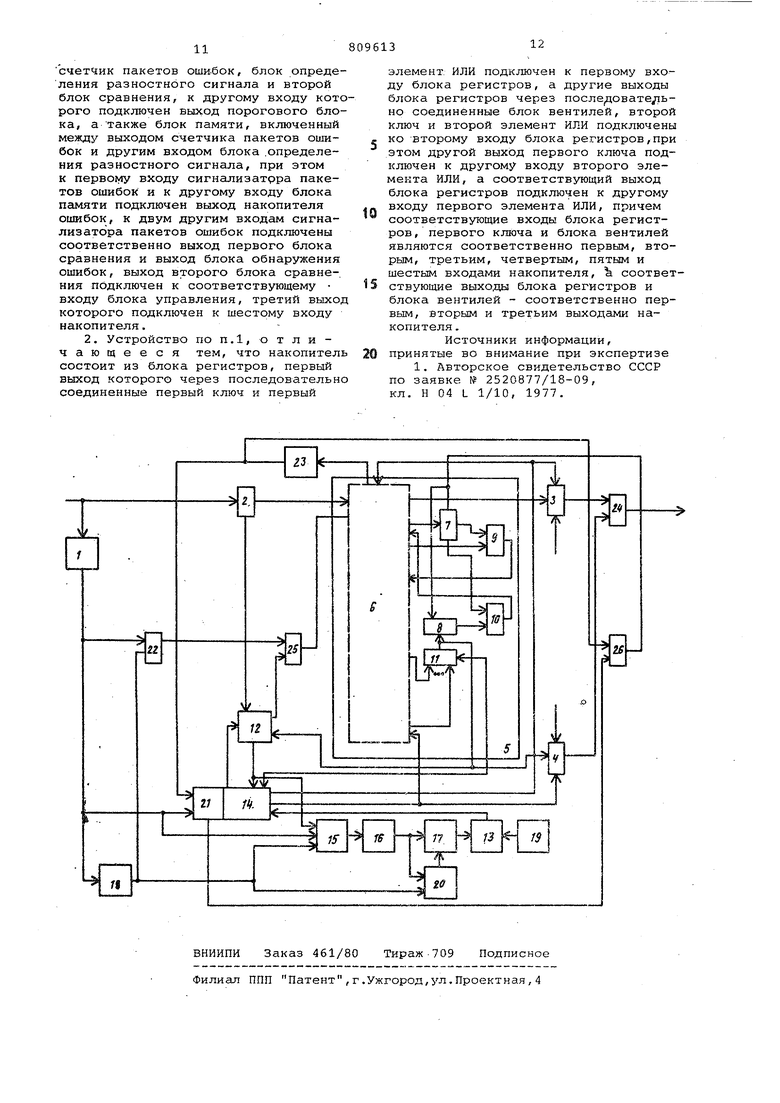

На чертеже представлена структурная электрическая схема предлагаемого адаптивного устройства.

Адаптивное устройство для анализа кодовых комбинаций в системах передачи дискретных сообщений с решающей обратной связью содержит блок. 1 обнаружения ошибок, первый, второй и третий ключи 2,3 и 4 соответственно накопитель 5, состоящий из блока б регистров, первого и второго ключей 7 и 8 соответств.енно, первого и второго элементов 9 и 10 ИЛИ, блока 11 вентилей, первый и второй блоки 12 и 13 сравнения соответственно, блок 14 управления, сигнализатор 15 пакетов ошибок, счетчик 16 пакетов ошибок, блок 17 определения разностного сигнала, накопитель 18 ошибок, пороговый блок 19, блок 20 памяти, счетчик 21 .блокировки, элемент 22 Пирса, дешифратор 23, элемент 24 ИЛИ, первый и второй элементы 25 и 26 И соответственно.

Устройство работает следующим образом.

Поступающая на вход V тройства комбинация одновременно анализируется в блоке 1 обнаружения ошибок и через первый ключ 2 записывается в блок 6 регистров накопителя 5. В случае отсутствия ошибок по команде с блока 14 управления комбинация из блока б регистров через открытый второй ключ 3 и элемент 24 ИЛИ выдается на вы5сод устройства. При этом выданная получателю комбинация через ключ 7 и элемент 10 ИЛИ перезаписывается в следующий регистр блока б регистров, а ранее записанная в блок б регистров комбинация через элемент 9 ИЛИ сдвигается в следующий регистр блока регистров. Таким образом, по мере последовательного приема каждой очередной комбинации и выдачи получателю предыдущей в блоке б регистров обеспечивается запоминание h, (где

h 1) комбинаций, принятых ранее. В случае обнаружения ошибки блок

Iвырабатывает на своем выходе сигнал ошибка, который воздействует на счетчик 21 блокировки и блок 14 управления. Блок 14 управления зарывает, второй ключ 3 и стирает искаженную комбинацию, записанную в первом регистре блока регистров. Таким образом, выход устройства блокируется, а в блоке б регистров производится накапливание hi - 1 комбинаций, следуемых за искаженной. Одновременно с этим-в накопителе 18 ошибок происходит регистрация и запоминание порядка следования комбинаций с обнаруженными ошибками./При этом устройство ожидает получение команды запрос на интервале времени поступления h комбинации, считая с начала блокировки. Если в указанный интервал команда запрос не будет получена, то устройство фиксирует выпадение h комбинаций на данной станции и вставку из h комбинаций на противоположной. Комбинации, записанные в накопителе 5, стираются и устройство переходит к очередному режиму работы. Если команда запрос поступила, то она выделяется дешифратором 23, который посылает на счетчик 21 блокировки и блок 14 управления, соответствующий сигнал. Если i после поступления данного сигнала блок 14 управления открывает ключ- 8, переключает информационный вход ключа 7 с одного выхода на другой выход, подключает выход ключа 2 ко входу устройства. В этом случае поступающие после команды запрос комбинации одновременно с записью в блок 6 регистров через ключ 2 поступают на один из выходов первого блока 12 сравнения, на другой вход которого выдаются комбинации с блока б регистров через блок

IIвентилей накопителя 5, принятые и накопленные в промежуток времени еящу моментом обнаружения и окончанием времени блокировки. Таким образбм начинается процедура сравнения.

В том случае, когда h{ h , , т.е. h К, процедура сравненияначинается только после поступления комбинации с момента начала

бЛОКИЕ рВКИ.

В первом блоке 12 сравнения производится сравнение соответствующих комбинаций в соответствии с заданным порогом VI сравнения {где liV Chi-1) соответствующим текущему числу повторяемых комбинаций hj . Если происходит V4 совпадений, то блок 12 сравнения на своем выходе формирует и выдает сигнал считывания накопленных в блоке б регистров комбинаций. По этой команде блок 14 управления открывает третий ключ 4, а на блок б

регистров подает сигнал считывания hj комбинаций. Накопленные в блоке б регистров комбинации через блок li вентилей, ключ 4 и элемент 24 ИЛИ поступают на выход устройства. При этом выдача происходит на повышенной тактовой частоте, которая позволяет осуществлять считывание записанных в блоке б регистров комбинаций за время, не превышающее время записи в первом регистре очередной комби0нации. После окончания выдачи схема возвращается в исходное состояние. При этом ключ 3 открывается, а третий ключ 4 закрывается.

Если совпадений не происходит,

5 то на данной станции фиксируется выпадение 2h , комбинаций, а на противоположной - вставка из hf комбинаций. При этом накопленные комбинации стираются, а устройство перехо0дит в исходное состояние.

В связи с тем, что комбинации, попавшие в зону блокировки в близлежащую зону, подвергаются усиленному воздействию помех, то для повышения помехозащищенности системы в дйнном

5 устройстве ос пцествляется адаптация числа повторяемых комбинаций h к качеству канала связи, что позволяет обеспечить увеличение помехозащищенности без существенного снижения

D текущей относительной скорости передачи информации. Это достигается следующим образом.

Перед началом выполнения процедуры сравнения по команде с блока 14

5 управления открывается ключ 8, а информационный вход ключа 7 переключается с одного выхода на другой. Далее первая повторяемая комбинация записывается в первый регистр блока

0 б, , h4-l-H,h4-2 -я и Т.Д. соответственно сдвигаются в последующие регистры. В этом цикле обработки сопоставления комбинаций не производит+СЯ. Сравнение комбинаций начинается с момента поступления второй комбина5ции после начала процедуры сравнения. Посту;пающая на вход сравнения комбинация через ключ 2 одновременно записывается в первом регистре блока б и подается на вход первого блока 12

0 сравнения. При этом ранее записанная В первом регистре блока б комбинация через выход ключа 7 и элемент 9 ИЛИ вытесняется вследующий регистр блока б и т.д. И наконец, комбинация,

5 хранимая в последнем регистре блока б вытесняется через блок 11 вентилей на второй вход блока сравнения для сравнения с поступающей в данный мо- : мент комбинацией,а через открытый ключ -8 и элемент 10 ИЛИ - в свободный

0 первый регистр блока 6.Таким образом, одновременно с выполнением процедуры сравнения в блоке 12 сравнения сравниваемые комбинации записываются в первые два регистра блока б до момен5

та ожидания принятия решения по результатам анализа в блоке 1 обнаружения ошибок и сравнения в блоке 12 сравнения.

Если ошибок не обнаружено и происходит совпадение обеих комбинаций, то с поступлением очередной комбинации на вход устройства, записью ее в первый регистр блока 6 и осуществлением сравнения с выводимой в данны момент комбинацией с последнего регистра блока б на блок 12. сравнени комбинации, находящиеся в первых, дву регистрах блока 6, объединившись на элементе 9 ИЛИ, записываются в следущем регистре блока б. Причем на мест комбинации, которая была записана-в первом регистре блока 6, поступает очередная, а на место комбинации, которая хранилась во втором регистре блока б через блок 11 вентилей, ключ 8 и элемент 10 ИЛИ поступает комбинация, находившаяся в последнем регистре блока б регистров. .

Если у сравниваемых комбинаций ошибок не обнаруживается и происходит их несовпадение, то сигнализатор 15 на основании сигналов, поступеиощих с блока 12 сравнения блока 1 обнаружения ошибок и накопителя 18 опцибок, производит формирование сигнала признака пакета ошибок V, поступающего на счетчик 16 пакетов ошибок, осуществляющий подсчет данных сигналов в течение интервала времени, оценивая качества канала связи Тдц. . Обе комбинации, находившиеся в первых двух регистрах блока б, .стираются. Стирание этих комбинаций происходит следуюоим образом.

Результат несовпадения разрядов обеих комбинаций, выявленный блоком . 12, воздействует на один вход элемента 25 И, на другой вход которого поступает сигнал с выхода элемента 22 Пирса, являющийся следствием отсутствия ошибок в сравниваемых комбинациях, т.е. в комбинации, принятой в данный момент, и в соответствующей ей комбинации, выдаваемой для сравнения из первого регистра блока б. Сигнал Отсутствия или наличия ошибки в последней запоминается в накопителе 18 ошибок, поэтому появление сигнала на выходе элемента 22 Пирса, воздействующего на другой вход элемента 25 ..является результатом одновременного отсутствия сигналов на выходах накопителя 18 оишбок и блока 1 обнаружения ошибок. Таким образом, на выходе элемента 25 И появляется сигнал, который и стирает из первых двух регистров блока б комбинации.

Если ошибка обнаружена только в одной из сравниваемых комбинаций, то последняя стирается, результат сравнения не учитывается и получателю выдается та, в которой ошибка не обнаружена. Одновременно сигналив

затор 15 анализирует,-в какой из сравниваемых комбинаций зафиксирована ошибка и если ошибка была обнаружена в повторно передаваемой комбинации, то формируется сигнал V признака пакета ошибок, поступающий на счетчик 16. Сигнал V признака пакета ошибок будет сформирюван также и в том случае, когда ошибки обнаружены в обеих сравниваемых комбинациях.

При поступлении команды запрос дешифратор 23 своим сигналом стирает ее из первого регистра блока б. Этим обеспечивается сравнение hf накопленных в блоке б регистров комбинаций до получения команды запрос с h 4 комбинациями, поступающими после команды запрос, а также запись последних в блок б регистров.

Если на блоке 12 сравнения V совпадений происходит, то на выходе последнего формируется сигнал о наличии совпадения (правильной работы) . Этот сигнал воздействует на блок 14 управ.ления, который аналогично случаю с обнаружением ошибки разрешает считывание получателю комбинаций из блока б регистров через ключ 4 и элемент 26 И на повышенной тактовой частоте. Причем при обнаружении несовпадений происходит формирование сигнализатором 15 сигнала признака пакета ошибок V.

Если совпадений не происходит то на данной станции фиксируется трансформация разрешенной комбинации в запрос и ожидается повторная команда запрос.

Ожидание повторной команды запрос связано со следующим. Так как после поступления первой команды запрос на станции обнаружения ошибки формируется и передается на противоположную станцию команда запрос и блок из h4 комбинаций, переданных ранее, то после получения .команды запрос на противоположной станции формируется и передается обратно также команда запрос с h комбинациями, вьщанными до нее.

Если на интервале от , до Ту команда запрос не поступит, то фиксируется выпадение h комбинаций на данной станции и вставка из hi комбинаций на противоположной. По сигналу с блока 14 управления записанные в блоке б регистров накопителя 5 комбинации стираются, а устройство переходит к новому режиму работы. Если же на указанном интервале команда запрос получена, то, выделив ее, дешифратор 23 выдает соответствуюЬшй сигнал на счетчик 21 блокировки и блок 14 управления. Далее начинается второй этап сравнения,который абсолютно идентичен сравнению после поступления команды запрос для случая обнаружения ошибки и еледуемой за ней команды запрос. При несовпадении V из h сравниваемых комбинаций фиксируется выпадение комбинаций на станции обнаружения и вставки - на противоположной. По окончании временного интервал оценивания канала производится считы ва:ние со счетчика 16 накопленного числа М, сформированного сигнализатором 15 сигналов Vf . Значение М. со счетчика 16 выдается на вход блока 20 памяти и на первый вход блока 17, на второй вход которого поступает значение числа М,-, полученное на предшествующем интервале оценив.ания. Модуль разности /г/ /Mj - М, с блока 17 поступает на вход второго блока 13 сравнения на другой вход ко торого поступает значение порога р. В случае, если г 0и|г| р, 3 также h,- h, со второго блока 13 сравнения поступает соответствующий сигнал на вход блока 14 управления. По данному сигналу блок 14 управления формирует на первый блок 12 срав нения сигнал об изменении величины порога сравнения V и организует формирование на противоположную стан цию кодовой комбинации об увеличении числа повторяемых комбинаций с величины и; до величины дЬ Если для i-rq интервала число Н равно К и соответственно после дним в блоке 6 регистров используется последний регистр, выход которого подключен через блок 11 вентилей ко входу ключа 8, то на (i +1)М интервале последним используется предпоследний регистр блока 6. При этом блок 14 управления отключает выход последнего регистра блока 6 от входа ключа 8 и подключает к его входу выход регистра блока 6. Когда г О и , а также блок управления 14 организует формирование на противоположную станцию кодовой комбинации об уменьшении чис ла повторяемых комбинаций с величивы величины hj4 К-1 . Кроме того блок 14 управления Формирует ffa первом блоке 12 сигнал об уменьшении порога сравнения V| и выдает соответствующий сигнал на блок 11 вентилей накопителя 5, подключая ко входу ключа 8 выход соответствующего регистра блока 6 регистров. В трм случае, когда , изменение числа повторяемых комбинаций не производится и блок управления 14 организует передачу на противоположную станцию кодовой комбинации о неизменности числа повторяемых комбинаций h. Если на данной станции не был сформирован сигнал о необходимости изменения h | , ас противоположной станции был принят-такой сигнал, то блок 14 управления по сигналу с дешифратора 23 стирает данную комбинацию из первого регистра блока б, затем формирует необходимый сигнал об изменении порога сравнения на первый блок 12 сравнения и на блок 11 вентилей сигнал подключения необходимого регистра к входу ключа 8, т.е. осуществляет операции по изменению числа повторяемых комбинаций h . Предлагаемое устройство позволяет улучшить помехоустойчивость системы передачи данных за счет подстройки числа повторяемых комбинаций h) к текущему состоянию качества канала связи. Формула изобретения 1.Адаптивное устройство для анализа кодовых комбинацийв системах передачи дискретных сообщений с решающей обратной связью, содержащее блок обнаружения ошибок, сигнальный вход которого объединен со входом первого ключа, выходы которого подключены соответственно к первому входу накопителя и к первому входу первого блока .сравнения, второй вход которого соединен с первым выходом накопителя,, а выход первого блока сравнения подключен к одному из входов блока управления, соединенного со счетчиком блокировки , ко входам которого подключены соответственно выход блока обнаружения ошибок и выход дешифратора, ко йхрду которого подключен второй выход накопителя, третий выход которого подключен ко входу второго ключа, к управляющему входу которого и ко второму входу накопителя подключен первый выход блока управления, а выход второго ключа подключен к одному из входов элемента ИЛИ, другой вход которого соединен с выходом третьего ключа, к информационному входу которого подключен первый выход накопителя, а к управляющему входу - подключен второй выход блока управления и третий вход накопителя, четвертый вход которого соединен с выходом первого элемента И, к одному из входов которого подключен второй выход первого блока сравнения, а к другому входу - выход элемента Пирса, ко входам которого подключен выход блока обнаружения ошибок непосредственно и через накопитель ошибок, выход счетчика блокировки подключен к одному из входов второго элемента И, к другому входу которого подключен выход дешифратора, а выход-второго элемента И подключен к пятому входу накопителя, отличающееся тем, что, с целью повышения помехоустойчивости работы устройства в условиях изменения состояния канала связи/ в него введены последовательно соединенные сигнализатор пакетов ошибок.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты от ошибок | 1982 |

|

SU1070700A1 |

| Устройство обнаружения вставок и выпадений информации в системах передачи данных | 1977 |

|

SU692103A1 |

| Устройство для защиты от ошибок | 1978 |

|

SU766029A1 |

| Устройство защиты от ошибок | 1987 |

|

SU1478362A2 |

| Устройство анализа кодовых комбинаций | 1976 |

|

SU649152A1 |

| Устройство защиты от ошибок | 1984 |

|

SU1197115A1 |

| Устройство обнаружения ошибок в системах передачи дискретной информации с решающей обратной связью | 1980 |

|

SU902284A2 |

| Устройство для приема дискретной информации | 1980 |

|

SU907845A2 |

| Устройство обнаружения и исправления вставок и выпадений информации | 1979 |

|

SU866765A1 |

| Устройство обнаружения вставок и выпадений информации в системах передачи данных с решающей обратной связью | 1971 |

|

SU468381A1 |

Авторы

Даты

1981-02-28—Публикация

1979-04-12—Подача