ТО.М, а не с приоритетом прерываний программы, необходимо переустанавливать содержимое регистра текущего состояния в номер .прерывающей программы. При выходе же из прерывающей подпрограммы необходимо в регистре текущего состояния восстановить номер старой программы.

Эти операции тpieбyют введения специальных команд в прерывающие подпрограммы и дополнительного оборудования для управления входами регистра текущего состояния.

Недостатком микропроцессора является необходимость установки содержимого регистра текущего состояния при входах и выходах в прерывающих программах, что снижает быстродействие микропроцессора и требует дополнительных аппаратурных затрат.

Целью изобретения является повышение быстродействия работы устройства за счет автоматического сохранения и восстановления приоритетов программ при прерываниях.

Поставленная цель достигается тем, что в устройство, содержащее регистр запросов, блок выходных элементов И, схему сравнения приоритетов, триггер прерывания и триггер запрета прерывания и коммутатор, причем информационный вход регистра запросов является входом запросов устройства, а первый выход соединен с первыми входами блока выходных элементов И и схемы сравнения приоритетов, выход которой соединен с первым входом коммутатора, выход которого соединен с первым входом триггера прерывания, выход которого соединен с выходом прерывания устройства, управляющий вход устройства соединен с вторыми входами коммутатора, триггера прерывания и блока выходных элементов И, третий вход которого соединен со вторым выходом регистра запросов, выход триггера прерывания соединен с первым входом триггера запрета прерывания, второй вход которого соединен с управляющ,им входом устройства, а выход - с третьим входом коммутатора и вторым входом регистра запросов, выход блока выходных элементов П является выходом запросов прерывания устройства, введены стек регистров состояний, входной и выходной коммутаторы, дещифратор, счетчик и управляющий коммутатор, причем выход блока выходных элементов И соединен через входной коммутатор с информационным входом стека регистров состояний, выход которого соединен через выходной .коммутатор со вторым входом схемы сравнения приоритетов, управляющие входы входного и выходного коммутаторов соединены с выходом дешифратора, вход которого соединен -с выходом .счетчика, вход которого соединен с иервым выходом управляющего коммутатора, второй выход

которого соединен с управляющими входом стека регистров, первый и второй входы управляющего коммутатора соединены соответственно с управляющим входом устройства и стробирующим входом устройства.

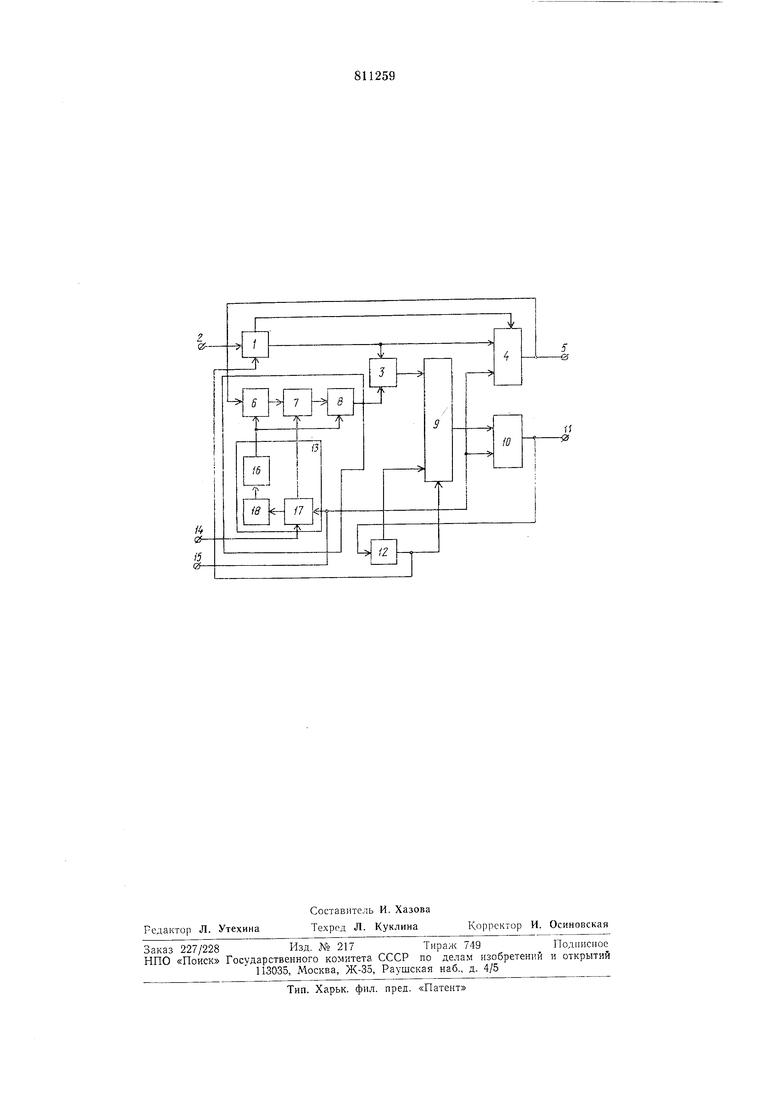

Структурная схема устройства приведена на чертеже.

Устройство для обработки приоритетов запросов прерываний содержит регистр / запросов, первый вход которого связан со входом запросов прерываний 2, схему сравнения приоритетов 3, блок выходных элементов И 4, выход которого связан с выходом запросов прерываний 5, последовательно соединенные входной коммутатор 6, стек регистров состояния 7 и выходной коммутатор 8, выход которого связан с одним из входов схемы сравнения приоритетов 3, коммутатор 9, выход которого связан с одним из .входов триггера црерывания 10, выход которого связан с выходом прерывания /У и первым входом триггера запрета прерывания 12, блок управления стеком 13, первый вход которого связан с стробирующнм входом 14, а второй - с управляющим входом i/5.

Блок 13 содержит дешифратор 16, управляющий коммутатор ./7 и счетчик 18.

Первый выход регистра запросов / связан с первым.и входами схемы сравнения приоритетов 3 и блока 4, второй выход - со вторым входом блока 4, выход которого связан со входом входного коммутатора. Выходы блока управления стеком 13 соединены соответственно со вторым входом коммутатора 6, стека регистров состояния 7 и выходного коммутатора 8.

Выход схемы сравнения приоритетов 3 соединен с первым входом коммутатора 9. Вторые входы коммутатора 9, триггера прерываний 10, триггера запрета прерывания 12 и третий вход блока 4 соединены с управляющим входом 15. Выход триггера запрета прерывания 12 соединен с третьим входом коммутатора 9 и вторым входом регистра запросов прерываний /.

Устройство работает следующим образом.

На вход регистра запросов 1 по входу запросов прерываний 2 приходят запросы на прерывания. На выходе регистра / индицируется код, соответствующий номеру активного в настоящий момент источника запроса с наивысшим приоритетом. Этот код поступает на первый вход схемы сравнения приоритетов 3, на второй вход которой коммутатора 8 поступает код, характеризующий приоритет обрабатываемой в настоящее время программы, записанный специальной командой из ЦВМ в стек регистров состояния .7.

При наличии на входе регистра запросов .1 кода, превосходящего текущий приоритет, на его выходе формируется сигнал, устанавливающий через коммутатор 9 триггер прерывания 10, с выхода которого запрос прерывания .поступает в микро-ЭВМ. Одновременно переустанавливается триггер запрета прерывания 12, который «замораживает состояние регистра запросов 1 на момент перехода к прерывающей программе с целью обеспечения условий корректного перехода. iB качестве указателя места входа в прерывающую программу (или ее идентификации) используются выходы кодированных номеров запросов прерываний, «а которые через блок 4 под управляющим сигналом по управляющему входу 1/5 индицируется номер активного источника, вызывающего прерывание. При переходе на очередную прерывающую подпрограмму в первый свободный регистр стека регистров 7 заносится приоритет прерывающей подпрограммы, соответствующий номеру активного запроса с высшим приоритетом, поступающего с выхода блока 4 через коммутатор 6 под управлением блока управления стеком 13, который одновременно подключает вход коммутатора 8 ко вновь загруженному стеку регистров 7. Таким образом, в блоке стека регистров автоматически при лереходе к прерывающим подпрограммам запоминается их приоритет. Количество регистров в стеке регистров 7 соответствует числу входов запросов прерываний в регистре запросов /. Таким образом, стек может сохранить приоритеты при переходе на максимально возможное число прерывающих подпрограмм. При выходе из прерывающих подпрограмм в блок управления стеком 13 со входа 14 подается сигнал, стробирующий подключение коммутатора 6 и выходного коммутатора 8 на один уровень «ниже в стеке, т. е. на первый занятый регистр, считая от того, который работал. В этом регистре хранится приоритет прерываний программы, который необходимо восстановить. Следовательно, стек работает как классический магазин. Таким образом, введение стека регистров текущего состояния позволяет автоматически сохранять и восстанавливать приоритеты программы при входах и возвратах из прерываний. Формула изобретения Устройство для обработки приоритетов запросов прерываний, содержащее регистр запросов, блок выходных элементов И, схему сравнения приоритетов, триггер прерывания и триггер запрета прерывания и коммутатор, причем 11нформационный вход регистра запросов является входом запросов устройства, а первый выход соединен с первыми входами блока выходных элементов И и схемы сравнения приоритетов, выход которой соединен с первым входом коммутатора, выход которого соединен с первым входом триггера прерывания, выход которого соединен с выходом прерывания устройства, управляющий вход устройства соединен со вторыми входами коммутатора, триггера прерывания и блока выходных элементов И, третий вход которого соединен со вторым выходом регистра запросов, выход триггера прерывания соединен с первым входом триггера запрета прерывания, второй вход которого соединен с управляющим входом устройства, а выход - с третьим входом коммутатора и вторым входом регистра запросов, выход блока выходных элементов И является выходом запросов прерывания устройства, отличающееся тем, что, с целью повышения быст1род€йствия, оно содержит стек регистров состояний, входной и выходной коммутаторы, дещифратор, счетчик и управляющий коммутатор, причем выход блока выходных элементов И соединен через входной коммутатор с информационным входом стека регистров состояний, выход которого соединен через выходной коммутатор со вторым входом схемы сравнения приоритетов, управляющие входы входного и выходного коммутаторов соединены с выходом дешифратора, вход которого соединен с выходом счетчика, вход которого соединен с первым выходом управляющего коммутатора, второй выход которого соединен с управляющим входом стека регистров, первый и второй входы управляющего коммутатора соединены соответственно с управляющим входом устройства и стробирующим входом устройства. Источники информации, принятые во внимание при экспертизе: 1.Белоус А. И. и др. Универсальный однокристальный микропроцессор. «Электронная промыщленность, 1977, № 5. 2.Schottky bipolar LSI microcomputer Set. Э2/4 Interupt control unit 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство многоуровневого прерывания | 1983 |

|

SU1104516A1 |

| Устройство многоуровневого прерывания | 1984 |

|

SU1174926A1 |

| Устройство многоуровневого прерывания | 1985 |

|

SU1287158A1 |

| Устройство для обработки приоритетов запросов прерываний | 1987 |

|

SU1562909A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1798781A1 |

| Устройство для контроля вычислительного процесса ЭВМ | 1988 |

|

SU1596332A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1661779A1 |

Авторы

Даты

1981-03-07—Публикация

1979-01-05—Подача