I

Изобретение относится к области радиоэлектронике, вычислительной и информационно-измерительной технике и может быть использовано в качестве быстродействующего высокочувствительного устройства сравнения постоянных или переменных электрических сигналов.

Известны быстродействующие компараторы, выпускаемые в виде интегральных микросхем 1, практически представляющие собой последовательно соединенные каскады напряжения, согласованные по выходу с типовыми интегральными схемами. Рещение задачи повышения быстродействия и чувствительности в таких компаратоpax ведется схемотехническим методом построения трактов усиления и стабилизации, основанным на введении дополнительной элементной и функциональной избыточности. Такой метод, позволяя получить быстродействие компаратора 10-40 нсек, практически .ведет к усложнению технологии изготовления интегральных микросхем,увеличению расходов материалов, снижению надежности и повыщению стоимости компаратора.

Известен также быстродействующий синхронный компаратор, содержащий дифференциальный каскад напряжения на двух транзисторах, базы подключены к

входным информационным шинам, а эмиттеры объединены и подключены к коллектору транзистора генератора стабильного тока, эмиттер которого через резистор подключен к источнику отрицательного напряжения 2.

Недостатки такого устройства - низкие быстродействие и чувствительность.

Целью изобретения является повышение быстродействия и чувствительности компараторов при одновременном уменьшении потребляемой мощности.

Поставленная цель достигается тем, что в быстродействующий синхронный компаратор, содержащий дифференциальный каскад напряжения на двух транзисторах, базы которых подключены к входным информационным шинам, а эмиттеры объединены и подключены к коллектору транзистор а генератора стабильного тока, эмиттер которого через резистор подключен к источнику отрицательного напряжения, введены дифференциальный каскад согласования и тактируемый элемент, причем база транзистора генератора стабильного тока подключена к объединенным выводам база-коллектор задающего транзистора генератора стабильного тока, эмиттер которого через резистор подключен к источнику отрицательного напряжения, а коллекторы

гранзисторов дифференциального каскада напряжения подключены соответственно к базам дифференциального каскада согласования и через соответствующие резисторы - к источнику положительного напряжения и коллекторам дифференциального каскада согласования, а эмиттеры дифференциального каскада Согласования соответственно подключены к эмиттерам входных транзисторов разбаланса тактируемого элемента с двумя устойчивыми состояниями и через соответствующие резисторы к объединенным выводам база-коллектор задающего транзистора генератора стабильного тока, база и коллектор первого входного транзистора расбаланса тактируемого элемента с двумя устойчивыми состояниями объединены и подключены к базе второго входного транзистора разбаланса, к базе транзистора левого плеча тактируемого элемента с двумя устойчивыми состояниями, к коллектору транзистора правого плеча тактируемого элемента с двумя устойчивыми состояниями, к базе транзистора усиления сигнала правого плеча тактируемого элемента с двумя устойчивыми состояниями и через резистор - к источнику положительного напряжения, коллектор второго входного транзистора разбаланса тактируемого элемента с двумя устойчивыми состояниями подключен к базе транзистора правого плеча тактируемого элемента с двумя устойчивыми состояниями, к коллектору транзистора левого плеча тактируемого элемента с двумя устойчивыми состояниями, к базе транзистора усилителя сигнала левого плеча тактируемого элемента с двумя устойчивыми состояниями и через резистор - к источнику положительного напряжения, причем коллекторы транзисторов усилителей сигналов левого и правого плеч тактируемого элемента с двумя устойчивыми состояниями подключены соответственно к выходным информационным шинам и через соответствующие резисторы-к источнику положительного напряжения, а эмиттеры транзисторов усилителей сигналов левого и правого плеч тактируемого элемента с двумя устойчивыми состояниями объединены с эмиттерами транзисторов левого и правого плеч тактируемого элемента с двумя устойчивыми состояниями и подключены к входной щине тактовых импульсов и через резистор - к источнику положительного напрял ения.

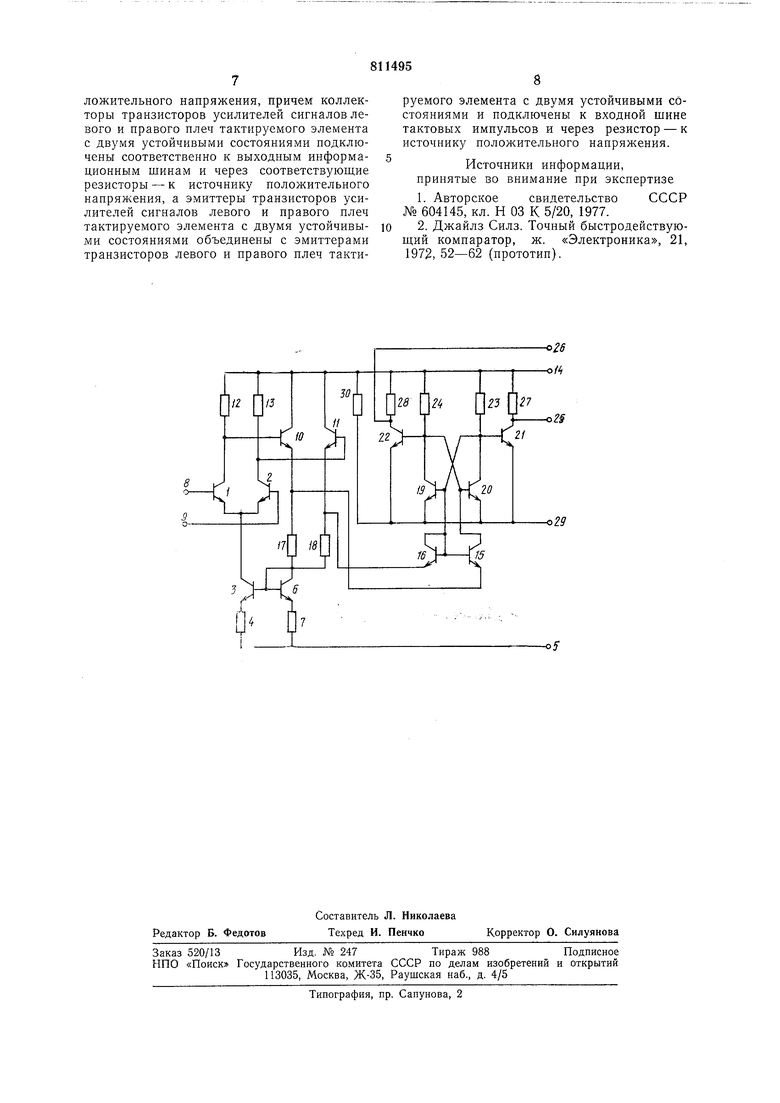

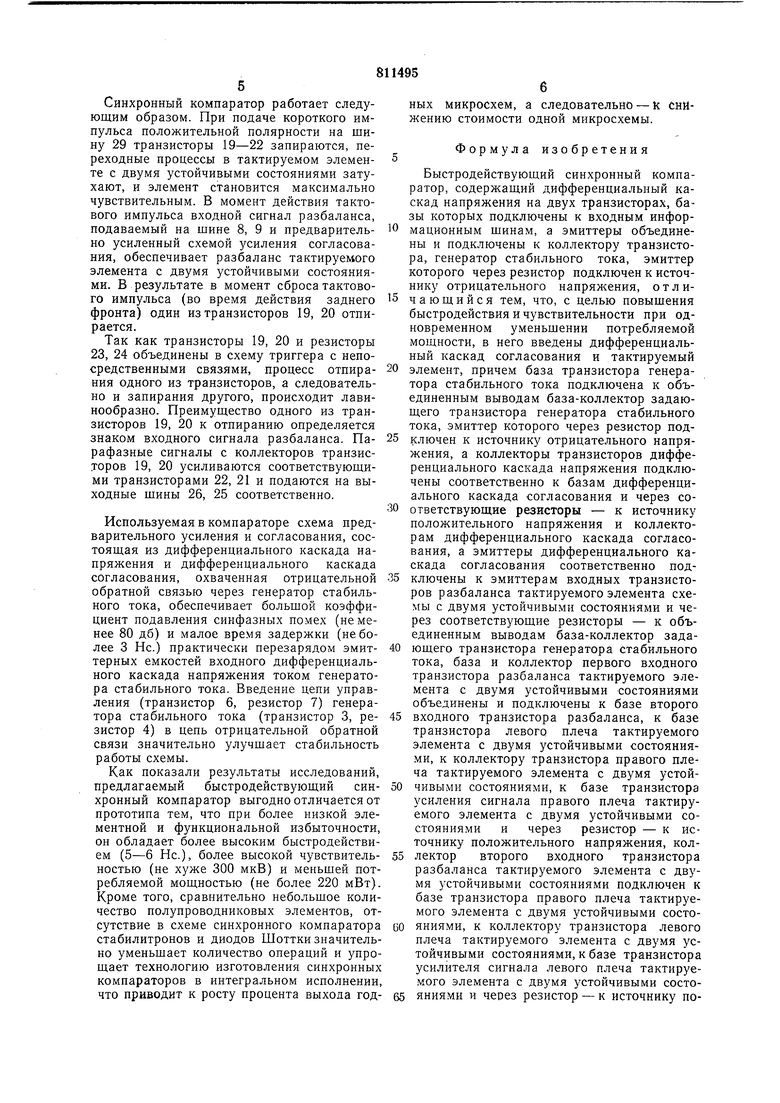

На чертеже приведена принципиальная схема синхронного компаратора в интегральном исполнении.

Эмиттеры транзисторов 1, 2 входного дифференциального каскада напряжения объединены и подключены к коллектору транзистора 3 генератора стабильного тока, эмиттер которого через резистор 4 подключен к шине 5 источника отрицательного напряжения, а база подключена к объединенным выводам база-коллектор транзистора 6, эмиттер которого через резистор 7 также подключен к шине 5 источника отрицательного напряжения. Базы транзисторов 1, 2 подключены к входным информационным шинам 8, 9 соответственно, а коллекторы - соответственно к базам транзисторов 10, 11 дифференциального каскада согласования и через

резисторы 12, 13 -к шине 14 источника положительного напряжения.

Эмиттеры транзисторов 10, 11 подключены к эмиттерам транзисторов 15, 16 соответственно и через резисторы Л 7, 18 - к

объединенным выводам транзистора 6. База транзистора 15 подключена к объединенным выводам база-коллектор транзистора .16 и к базе транзистора 19 левого плеча тактируемого элемента с двумя устойчивыми состояниями (тактируемый элемент с двумя устойчивым состояниями выполнен на транзисторах 19-22 и резисторах 23, 24, 27, 28, 30), которая в свою очередь подключена к коллектору транзистора 20 правого плеча тактируемого элемента с двумя устойчивыми состояниями, к базе транзистора 21 усилителя сигнала правого плеча тактируемого элемента с двумя устойчивыми состояниями и через резистор 23 - к

шине 14 источника положительного напряжения.

Коллектор транзистора 15 подключен к базе транзистора 20 правого плеча тактируемого элемента с двумя устойчивыми состояниями, которая в свою очередь подключина к коллектору тарнзистора 19 левого плеча тактируемого элемента с двумя устойчивыми состояниями, к базе транзистора 22 усилителя сигнала левого плеча тактируемого элемента с двумя устойчивыми состояниями и через резистор 24-к шине 14 источника положительного напряжения. Коллекторы транзисторов 21, 22 подключены к выходным информационным шинам

25, 26 соответственно и через резисторы 27, 28 - к шине 14 источника положительного напряжения. Объединенные эмиттеры транзисторов 19-22 подключены к входной шине 29 ввода тактовых импульсов и через

резистор 30-к шине 14 источника положительного напряжения.

Компаратор назван синхронным в связи с тем,что результат сравнения фиксируется в заданный момент времени (задний фронт

тактового импульса). Особенность данного компаратора заключается в том, что быстродействие измеряется временем, которое необходимо для разбаланса тактируемого элемента с двумя устойчивыми состояниями непосредственно перед фиксацией задним фронтом тактового импульса. Как показали исследования, это время равно 5-6 Не. при разности входных сигналов не более 30 мкВ и уменьшается при увеличеНИИ разбаланса.

Синхронный компаратор работает следующим образом. При подаче короткого импульса положительной полярности на шину 29 транзисторы 19-22 запираются, переходные процессы в тактируемом элементе с двумя устойчивыми состояниями затухают, и элемент становится максимально чувствительным. В момент действия тактового импульса входной сигнал разбаланса, подаваемый на шине 8, 9 и предварительно усиленный схемой усиления согласования, обеспечивает разбаланс тактируемого элемента с двумя устойчивыми состояниями. В результате в момент сброса тактового импульса (во время действия заднего фронта) один из транзисторов 19, 20 отпирается.

Так как транзисторы 19, 20 и резисторы 23, 24 объединены в схему триггера с непосредственными связями, процесс отпирания одного из транзисторов, а следовательно и запирания другого, происходит лавинообразно. Преимущество одного из транзисторов 19, 20 к отпиранию определяется знаком входного сигнала разбаланса. Парафазные сигналы с коллекторов транзисторов 19, 20 усиливаются соответствующими транзисторами 22, 21 и подаются на выходные шины 26, 25 соответственно.

Используемая в компараторе схема предварительного усиления и согласования, состоящая из дифференциального каскада напряжения и дифференциального каскада согласования, охваченная отрицательной обратной связью через генератор стабильного тока, обеспечивает большой коэффициент подавления синфазных помех (не менее 80 дб) и малое время задержки (не более 3 Не.) практически перезарядом эмиттерных емкостей входного дифференциального каскада напряжения током генератора стабильного тока. Введение цепи управления (транзистор 6, резистор 7) генератора стабильного тока (транзистор 3, резистор 4) в цепь отрицательной обратной связи значительно улучшает стабильность работы схемы.

Как показали результаты исследований, предлагаемый быстродействующий синхронный компаратор выгодно отличается от прототипа тем, что при более низкой элементной и функциональной избыточности, он обладает более высоким быстродействием (5-6 Не.), более высокой чувствительностью (не хуже 300 мкВ) и меньшей потребляемой мощностью (не более 220 мВт). Кроме того, сравнительно небольщое количество полупроводниковых элементов, отсутствие в схеме синхронного компаратора стабилитронов и диодов Шоттки значительно уменьщает количество операций и упрощает технологию изготовления синхронных компараторов в интегральном исполнении, что приводит к росту процента выхода годных микросхем, а следовательно - к снижению стоимости одной микросхемы.

Формула изобретения

Быстродействующий синхронный компаратор, содержащий дифференциальный каскад напряжения на двух транзисторах, базы которых подключены к входным информационным щинам, а эмиттеры объединены и подключены к коллектору транзистора, генератор стабильного тока, эмиттер которого через резистор подключен к источнику отрицательного напряжения, отличающийся тем, что, с целью повышения быстродействия и чувствительности при одновременном уменьшении потребляемой мощности, в него введены дифференциальный каскад согласования и тактируемый элемент, причем база транзистора генератора стабильного тока подключена к объединенным выводам база-коллектор задающего транзистора генератора стабильного тока, эмиттер которого через резистор подключен к источнику отрицательного напряжения, а коллекторы транзисторов дифференциального каскада напряжения подключены соответственно к базам дифференциального каскада согласования и через соответствующие резисторы - к источнику положительного напряжения и коллекторам дифференциального каскада согласования, а эмиттеры дифференциального каскада согласования соответственно подключены к эмиттерам входных транзисторов разбаланса тактируемого элемента схемы с двумя устойчивыми состояниями и через соответствующие резисторы - к объединенным выводам база-коллектор задающего транзистора генератора стабильного тока, база и коллектор первого входного транзистора разбаланса тактируемого элемента с двумя устойчивыми состояниями объединены и подключены к базе второго входного транзистора разбаланса, к базе транзистора левого плеча тактируемого элемента с двумя устойчивыми состояниями, к коллектору транзистора правого плеча тактируемого элемента с двумя устойчивыми состояниями, к базе транзистора усиления сигнала правого плеча тактируемого элемента с двумя устойчивыми состояниями и через резистор - к источнику положительного напряжения, коллектор второго входного транзистора разбаланса тактируемого элемента с двумя устойчивыми состояниями подключен к базе транзистора правого плеча тактируемого элемента с двумя устойчивыми состояниями, к коллектору транзистора левого плеча тактируемого элемента с двумя устойчивыми состояниями, к базе транзистора усилителя сигнала левого плеча тактируемого элемента с двумя устойчивыми состояниями и через резистор - к источнику положительного напряжения, причем коллекторы транзисторов усилителей сигналов левого и правого плеч тактируемого элемента с двумя устойчивыми состояниями подключены соответственно к выходным информационным шинам и через соответствующие резисторы - к источнику положительного напряжения, а эмиттеры транзисторов усилителей сигналов левого и правого плеч тактируемого элемента с двумя устойчивыми состояниями объединены с эмиттерами транзисторов левого и правого плеч тактнруемого элемента с двумя устойчивыми состояниями и подключены к входной шине тактовых импульсов и через резистор - к источнику положительного напряжения.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 604145, кл. Н 03 К 5/20, 1977.

2.Джайлз Силз. Точный быстродействующий компаратор, ж. «Электроника, 21, 1972, 52-62 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоустойчивый компаратор напряжения | 1981 |

|

SU993466A1 |

| Регулятор напряжения для генератора переменного тока | 1980 |

|

SU1005261A1 |

| Следящий многоустойчивый компаратор напряжений | 1974 |

|

SU660226A1 |

| Дифференциальный усилитель | 1983 |

|

SU1146792A1 |

| Таймер | 1981 |

|

SU974581A1 |

| Компаратор | 1987 |

|

SU1448402A1 |

| УСИЛИТЕЛЬ МОЩНОСТИ ЗВУКОВОЙ ЧАСТОТЫ | 1993 |

|

RU2115224C1 |

| Аналого-цифровой преобразователь последовательного приближения | 1981 |

|

SU1018228A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1350831A1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ДИФФЕРЕНЦИАЛЬНОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С НЕЛИНЕЙНОЙ КОРРЕКЦИЕЙ ПЕРЕХОДНОГО ПРОЦЕССА | 2023 |

|

RU2797043C1 |

Авторы

Даты

1981-03-07—Публикация

1979-01-11—Подача