(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КОРРЕЛЯЦИОННЫХ

ФУНКЦИЙ

ходом масштабного блока, четвертую линию задержки, вход которой соединен со вторым выходом масштабного блока, пятую линию задержки, вход которой соединен через первое и второе положение второго переключателя и третий переключатель соответственно с выходами четвертой и первой линии задержки .и вторым выходом маслгтабного блока а выходы подключены в обратном порядке через аналоговые ключи третьего блока ключей к соответствующим входам третьего сумматора, подключенного своим выходом ко второму входу блока умножения, выход которого дополнительнч через третий аналоговый ключ, второй интегратор со схемой сброса и четвертый аналоговый ключ соединен со вторым входом второго сумматора, соединенные последовательно первый блок управления, у которого дополнительный выход соединен с дополнительным входом масштабного блока, а третий выход - с управляющим входом первого блока ключей, генератор тактовых импульсов и распределитель импульсов выходы которого подключены к соответствующим попарно соединенным управляющим входам второго и третьего блока ключей,, генератор импульсов, вход которого соединен со вторым выходом первого блока управления, дополнительный вход - с дополнительным выходом генератора тактовых импульсов, первые выходы подключены к управляющим входам каждой ячейки памяти первой, второй и третьей линии задержки, а вторые выходы - к управляющим входам каждой ячейки памяти четвертой и пятой линии задержки, и второй блок управления, у которого вход соединен с п-ыми управляющими входами второго и третьего блоков ключей и подключен к п-ому выходу распределителя импульсов, а соответствующие выходы подсоединены к управляющим входам первого, второго, третьего и четвертого аналоговых ключей и первого и второго интеграторов со схемами сброса {2},

Недостатки этого устройства- не - высокая точность вычисления и сложность , обусловленные необходимостью кокв.«утации с повышенной скоростью большого числа ключевых элементов, нал|ичием интеграторов со схемами сбрюса, появлением динамических погрейностей при вычислении корреляционных функций как узкополосных так и широкополосных сигнгшов за счет коммутации ключевых элементов и необходимостью использования линии задержки с большим числом звеньев или ячеек памяти.

Цель изобретения - повышение точности вычисления корреляционных функций..

Поставленная цель достигается тем, что в устройство для вычисления корреляционных функций, содержащее масштабный блок, первый и второй входы которого являются соответственно первым и вторым входами устройства, первую линию задержки, выходы которой соединены с К входами первой группы блока ключей в обратном порядке, /С выходов первой группы которого подключены к соответствующим входам второй линии задержки, третью линию задержки,вход которой соединён с выходом второй линии задержки с к+1-м выходом блока ключей и через первый переключатель - с первым выходом масштабного блока, блок умножения, сумматор,выход которого является первым выходом устройства и соединен с первым входом блока преобразования частоты, выход которого является вторым выходом устройства, а второй вход соединен со вторым выходом масштабного блока, четвертую линию задержки, вход которой соединен с третьим выходом масштабного блока, пятую лилинию задержки, вход которой соединен с выходом второго и третьего переключателей, первый выход второго переключателя соединен с выходом четвертой линии задержки, а выход третьего переключателя подключен к третьему выходу масштабного блока, третий вход которого подключен к первому выходу блока управления, второй вход которого соединен с управляющим входом блока ключей, введены шестая и седьмая линии задержки, первый выход масштабного блока соединен со входом шестой линии задержки, С выходов которой соединены с /С входами второй группы блока ключей в обратном порядке, К. выходов второй группы которого соединены с соответствующими входами третьей линии задержки, а к+1-ый выход шестой линии задержки соединен со входом первой, линии задержки, со вторым входом второго переключателя и с К+1-М входом блока ключей, первая группа входов блока умножения соединена соответственно, с выходом второй, линии задержки и с выходами третьей и седьмой линий задержки, вторая группа входов блока умножения соединена в обратном порядке с соответствующими выходами пятой линии задержки, выходы блока ум- . ножения подключены к соответствующим входам сукматора.

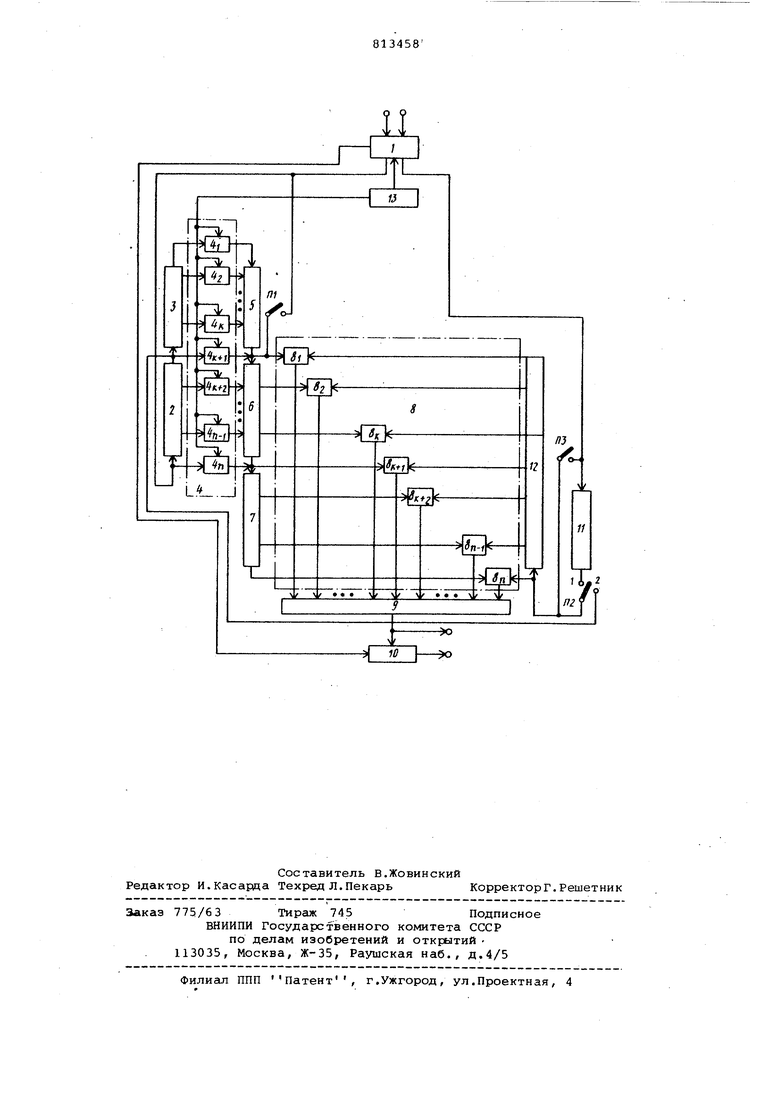

На чертеже приведена структурная схема устройства.

Устройство для вычисления корреляционных функций содержит масштабный блок 1, входы которого являются входами устройства, соединенные последовательно шестую линию 2 задержки, вход которой соединен с

первым выходом масштабного блока 1, и первую линию 3 задержки, блок 4 ключей, состоящий из n(((+ ) аналоговых ключей, у которых сигнальные входы являются Входами блока ключей и подсоединены в обратном порядке к соответствующим выходам линий 3 и 2 задержки, упрабляющие входы соединены вместе и подключены вместе к управляющему входу блока ключей и выходы являются выходами блока ключей, соединенные последовательно линию задержки 5, К, входов которой подключены в прямом порядке к соответствующим К, первым выходам блока 4 ключей, линию 6 задержки, у которой первый вход через первый переключатель П1 соединен с первым выходом масштабного блока 1, а остальные /С входов подсоединены в прямом порядке к остальным /С выходам блока 4 ключей, линию 7 задержки, блок 8 умножения, состоящий из п элементов перемножения колебаний, у которых первые входы являются первой группой входов блока умножения и подключены в прямом порядке к соответствующим выходам линий 6 и 7 задержки , вторые входы являются второй группо входов блока умножения и выходы являются выходами блока,умножения, соединенные последовательно сукв4атор 9, у которого входа соединены с выходами блока 8 умножения, .а выход соединен с первым выходом устройства, и блок 10 преобразования частоты, у которого выход является вторым выходом устройства, а дополнительный вход соединен с дополнительным выходом масштабйого блока 1, линию 11 задержки, вход которой соединен со вторым выходом масиггабного блока 1, линию 12 задержки, вход которой соединен через первое и второе положение переключателя П2 и через переключатель ПЗ соответственно с выходами линий 11 и 2 задержки и вторым выходом масштабного блока 1, а выходы в обратном порядке соединены с соответствукиаим входами второй группы входов блока 8 умножения, и блок 13 управления, первый выход которого соединен с дополнительным входом масштабного блока 1 , а второй шяход соединен с управляющим BXOjgtOM блока 4 ключей.

Масштабный блок 1 состоит из дву каналов (при вычислении взаимокорреляционных функций и взаимной свертк двух функций) или из одного канала (при вычислении автокорреляционных функций и автосвертки) и содержит, в частности, перестраиваемые по частоте входные цепи со ступенчатыми делителями напряжения, смеситель, перестраиваемый по частоте гетероди (или гетеродины) и усилители с регулируемыми коэффициентами усиления (при необходимости каналы дополнительно могут содерл ать автоматические cxeNu перестройки или подстройки) частот гетеродинов (или гетеродина) и входных цепей и автоматические схемы регулировки амплитуд выходных напряжений.

В качестве линий 2,3,5,6,7,11 и. 12 задержки могут быть использованы элементы задержки аналогового, дискретно-аналогового и цифрового типов. В последних двух случаях управление работой линий 2,3,5,6,7, 11 и 12 задержки может быть общим, т.е. осуществляться от одного блока управления. Время-задержки линии 12 задержки меньше максимальной длительности обрабатываемых сигналов на величину, равную времени задержки между двумя соседними отводс1ми. Время задержки линий 2,3,5,6 и 7 задержки равно половине времени задержки линии 12 задержки. Время згшержки ли|нии 11 задержки больше времени задержки линии 2,3,5,6 или 7 задержки на величину, равную половине времени задержки между двумя соседними отводами. Время задержки между двумя соседними отводами у всех линий 2,3,5,6,7 т 12 задержки одинаково.

Блок 10 преобразования частоти состоит, например из смесителя, к которому дополнительно подводится колебание гетеродина масштабного блока 1, и выходного усилительного тракта.

Блок 13 управления предназначен

для ввода в режим работы масштабного блока 1 и отпирания через кажддай интервал времени Т -At(n-l) на длительность At аналоговых ключей блока 4 (Т - длительность обрабатываемого сигнала, которая равна максимально возможной длительности обрабатываемлс сигналов), At - время задержки между двумя соседними отводами линий задержки; в частности,At равно интервалу отсчетов по

Котельникову и состоит, например из функционально связанных между собой задахицего генератора и схемы управления на элшкентах дискретной техники.

Устройство для вычисления корреляционных функций работает следующим образом.

В мсмент времени блок 13 управления вводит в режим работы

масштабньй блок 1 и сигналы fj, (tj и fi(t) через первый и второй входы устройства поступают в масштабный блок 1, где происходит преобразование до необходимых значений средних частот их спектров и усиление по

амплитуде до заданных преобразованных по частоте сигналов f(t) и fi(t).

С первого и второго выходов масштабного блока 1 сигналы fj(t) и

f(t) поступают на входы соответственно линий 2 и 11 задержки, распространяясь далее вдоль этих линий. При этом по мере продвижения сигнала f(t) вдоль шестой линии 2 задержки он непрерывно поступает через ее отводы на входы, закрытых аналоговых ключей 4п..Ни-1 , блока 4 ключей.

Через интервалы времени и t(k+) At сигналы fj(t) и ) поступают на входы соответственно линий 3 и 12 задержки, распространяясь далее вдоль этих линий. При этом по мере продвижения этих сигналов вдоль линий 3 и 12 задержки они непрерывно поступают через их отводы соответственно на входы закрытых соответствующих аналоговых ключей блока 4 и на вторую группу входов блока 8 умножения. Так как в этом случае на первой группе блока 8 умножения отсутствуют значения сигналов, то результаты умножения на выходах блока 8 равны нулю.

В момент времени под воздействием импульса длительностью At блока 13 управления открываются аналоговые ключи блока 4 и значения соответственно выборок f (t) , (k-1)AtJ, с выходов (отводов) линий 3 и 2 задержки в течение интервала А t поступают через аналоговые ключи блока 4 на соответствующие входы пиний 5-7 задержки, распространяясь далее вдоль этих линий задержки в таком порядке

fjlt-Cn-Dut, fjCt)

В этот же момент-времени значения выборок fjlt-Cn-DAt, fjtt-{n2)AtJ,..., (k+1)4t начинают поступать на интервал at на первую группу входов блока 8 умножения.

В момент времени на втору группу входов блока 8 умножения начинают поступать на интервал At с соответствующих выходов пятой линии 12 задержки значения выборок соотвественно f4(t-Mj At). В этот же момент времени на выходе элемента перемножения колебаний блока 8 умножения образуется значение

f3tt-(n-1)ut f4() длительностью At, которое в течени интервала д t через сумматор 9 поступает на первый выход устройства и вход блока 10 преобразователя часTOTId.

Так как выбЬрочные значения f,Lt-( l-1)ut , ....1 и выборочные значения f (t- д t) , i 1 . . распространяясь вдоль линии 6,7 и 1 задержки на встречных направлениях, поступают последовательно во времени каждый раз на интервал;at соответственно на обе группы входов блока 8 умножения, то в момент времени на выходах схем 8|l и вх,перемножения колебаний блока 8 умножения образуются значения It-(n-l) ь t f;, (t-| д t) ; B f3lt- n-2)atl f () длительностью At , которые в течение интервала А t через сумматор 9 поступают на первый выход устройства и вход блока 10 преобразования частоты в виде суммы: А+В, обновляясь через интервал 4 А t, на первом выходе устройства и входе блока 10 преобразования частоты с течением времени формируется следующий результат:

уП) f3(t-T+OAt) f4 lt-(m-)+j4t) ; (, ), который с точностью до постоянного множителя является

5 приближенным значением корреляционного интеграла с уменьшенным в два раза масштабом времени.

После восстановления прежнего (или заднего ) значения средней частоты спектра сигнала в блоке 10 преобразования частоты на втором выходе устройства образуется следующее окончательное значение результата:

5 ,l1(t-тt)лt)fгlt-(m-л))йtli (),

который с точностью до постоянного множителя является приближенным вычислением корреляционного интеграла

0 V(t) |fi(t-T-rt)f7(t4r-t- ftl)dt ()

если только в нем уменьшить в два раза масштаб изменения Y(t) по оси t. Приведенное описание работы предe лагаемого устройства будет справедливо и тогда, когда f (t) fa (t) f (t), . и f(t) и fi(t) являются четными и нечетнь1ми функциями.

При выполнении условия fii(t) f(t)f(t) можно соединить между

0 собой входы масштабного блока 1, а также его первый и второй выходы, и переключатель П2 поставить в положение 2.

При вычислении интеграла свертки

5 y(t)I fi () f7(t-r)drнеобходимо разомкнуть переключатель П2 и замкнуть переключатели П1 и ПЗ.

Таким образом, введение новых блоков: двух линий задержки и установление новых связей выгодно отли- . чает предлагаемое устройство от указанного прототипа, так как позволило обеспечить высокое быстродействие, увеличить точность вычисления коррес ляционных функций как узкополосных, так и широкополо сных сигналов,также упростить устройство за счет использования линий задержки с меньшим числом звеньев/или ячеек памяти/ и уменьшения номенклатуры функциональных элементов. В результате этого

существенно расширится область применения устройства и отпадет необходимость в разработке ряда устройств с близко расположенными диапазонами рабочих частот, улучшатся тактикотехнические и технико-экономические показатели при изготовлении и эксплуатации . Формула изобретения Устройство для вычисления коррел ционных функций, содержащее масштаб ный блок, первый и второй входы которого являются соответственно первым и вторым входами устройства,пер вук) линию задержки, выходы которой соединены с входами первой группы блока ключей в обратном порядке. К, выходов первой группы которого подключены к соответствукадим входам второй линии задержки, третью линию задержки, вход которой соединен с выходом второй линии задержки с к+1 выходом блока ключей, и через первый переключатель - с первым выходом масштабного .блока, блок умножения, сумматор, выход которого является первым выходом устройства и соединен с первым входом блока преобразования частоты, выход которого является вторым выходом устройства, а второй вход соединен со вторым выходом масштабного блока, четверту линию задержки, вход которой соединен с третьим выходом масштабного блока, пятую линию задержки, вход которой соединен с выходом второго и третьего переключателей, первый выход второго переключателя соедине с выходом четвертой .линии задержки. а выход третьего переключателя подключен к третьему выходу масштабного блока, третий вход которого подключен к первому выходу блока управления, второй вход которого соединен с управляющим входом блока ключей, отличающееся тем, что, с целью повЕлиения точности, в устройство введены шестая и седьмая линии задержки, первый выход масштабного блока соединен со входом Шестой линии задержки, АС выходов которой соединены с С входами второй группы блока ключей в обратном порядке, К, выходов второй группы которого соединены с соответствующими входами третьей линии задержки, а к+1-ый выход шестой линии задержки соединен со входом первой линии задержки, со вторым входом второго переключателя и с к+1-м входом блока ключей, первая группа входов блока умножения соединена соответственно с выходом второй линии задержки и с выходами третьей и седьмой линии задержки, вторая группа входов блока умножения соединена в обратном порядке с соответствующими выходами пятой линии задержки, выходы блока умножения подключены к соответствующим входам сумматора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 306471, кл. G 06 G 7/19, 1971. 2.Авторское свидетельство СССР по заявке 2616085/18-24, 1978.

ID I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления свертки функций | 1978 |

|

SU742969A1 |

| Аналого-цифровое устройство дляВычиСлЕНия СВЕРТКи фуНКций | 1979 |

|

SU817724A1 |

| Устройство для вычисления свертки функций | 1977 |

|

SU686038A1 |

| Время-импульсный анализаторСигНАлА | 1979 |

|

SU817725A1 |

| Взаимокоррелятор | 1984 |

|

SU1201846A1 |

| УСТРОЙСТВО для КУСОЧНО-КВАДРАТИЧНОЙ АППРОКСИМАЦИИ ФУНКЦИЙ | 1973 |

|

SU374622A1 |

| Устройство для определения взаимной корреляционной функции | 1983 |

|

SU1108463A1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Анализатор импульсных моментовлиНЕйНыХ СиСТЕМ АВТОМАТичЕСКОгОРЕгулиРОВАНия | 1979 |

|

SU847283A1 |

| Дискретно-аналоговое устройство задержки | 1979 |

|

SU879758A1 |

Авторы

Даты

1981-03-15—Публикация

1978-10-23—Подача