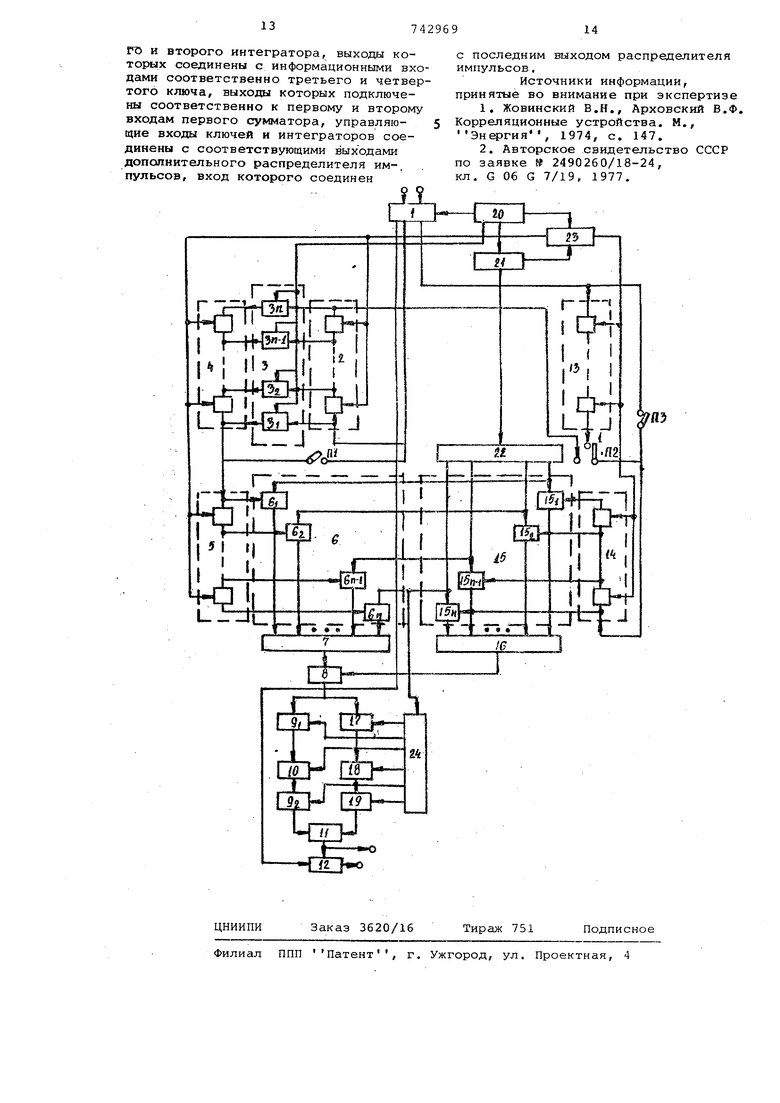

Изобретение относится к специали |эированной вычислительной технике и может быть использовано в радиотехнике, связи, радиоавтоматике, из мерительной технике,радионавигации, радиолокации, гидролокации, радиоуправлении, диагностической аппаратуре, авторегулировании, автоконтро ле и других областях для вычисления свертки функций и корреляционного анализа принимаемых известных и неизвестных сигналов и измерения их параметров и характеристик , а также для обнаружения и опознавания сигна лов и источников их излучения, Известно устройство для корреляционного ансшиза, содержащее аналог цифровой преобразователь, линии задержки, блоки умножения и блоки усреднения Ul. Недостатком устройства является сложность аналого-цифровых блоков умножения и необходимость многоканальной линии задержки. Известно также устройство для вычисления свертки функций, содержа щее функционально связанные между собой масштабный блок, блок управления, генератор импульсов, блок преобразования частоты, линии задержки, блоки умножения, распределитель импульсов, блоки памяти по числу блоков умножения, рециркуляторы и интегратор 2. Недостатком известного устройства является неинвариантность к времени прихода сигналов, а также невозможность вычисления корреляционных функций общего вида. Цель изобретения - расширение функциональных возможностей путем вычисления корреляционных функций. Для достижения указанной цели в устройство для вычисления свертки функций, содержащее масштабный блок, первый и второй входы которого являются соответствующими входами устройства, а первый выход соединен со входом первой линии задержки с последовательно соединенными ячейками памяти, блок управления, первый выход которого соединен со входом генератора импульсов, первый выход которого подключен к управляющим входам ячеек памяти первой линии задержки, распределитель импульсов, блок умножения, первый сумматор, выход которого соединен с первым входом бло-ка преобразования частоты, введены генератор тактовых импульсов, четыре линии задержки с последовательно соединенными ячейками памяти, три блока ключей, два сумматора, два интегратора, четыре ключа, дополнительный распределитель импульсов и три переключателя, при этом информационные входы первого блока ключей соединены с выходами соответствующих ячеек первой линии задержки, а управляющие взводы - со вторым выходом блока упра лёния, третий и четвертый выходы KciTOporo подключены соответственно KCS входу генератора тактовых импульсов и к третьему входу масштабного , второй выход которого соединён с первым входом блока преобразовз|ния частоты, первый и третий вых0ды Масштабного блока подключены соответственно к неподвижным контакт4м соответственно первого и второго пфеключателей, подвижные контакты которых подключены соответственно к вйходу второй и ко входу третьей линии задержки, ко входу четвертой линии задерлски и к подвижному контак ту третьего переключателя, первый и второй неподвижные контакты которого соединены соответственно с вы-, хойом первой и пятой линий задержки, последней подключен к третьему вМходу масштабного блока; выходы Генератора тактовых импульсов соедин ны соответственно со входом распре делителя импульсов и со вторым входо генератора импульсов, второй выхо которого подключен к управляющим вхо дам ячеек четвертой и пятой линий за держки, выходы первого, второго и третьего блока ключей соединены с соответствующими входами ячеек второй линии задержки, второго сумматора и с соответствующими входами третьего сумматора, выходы распределителя импульсов подключены к соо ветствующим управляющим входам втор и третьего блоков ключей, информационные входы которых соединены с выходами соответствующих ячеек третьей и четвертой линий задержки, выходы второго и третьего сумматора подключены к соответствующим входам умножения, выход которого сое динен с информационными входами пер вого и второго ключей, выходы котор х подключены соответственно ко входам первого и второго интёгратоР0В, выходы которых соединены с инфОрмационными входами соответственн третьего и четвертого ключей, выход которых подключены соответственно к первому, и второму входам первого сумматора:, управляющие входы ключей и интеграторов соединены с соответствующими выходами дополнительного распределителя импульсов, вход кото рого соединен с последним выходом р пределителя импульсов. На чертеже приведена структурная схема предлагаемого устройства. Устройство содержит соединенные оследовательно масштабный блок 1, входы которого являются входами устройства, линию 2 задержки, состоящую из последовательно соединенных ячеек памяти, выход каждой из которых является выходом линии задержки и соединен со входом последующей ячейк-и памяти, блок 3 аналоговых ключей, у которых сигнальные входы являются сигнальными входами блока и подключены в прямом порядке к соответствующим выходам линии 2 задержки, выходы ЯВ.ПЯЮТСЯ выходами блока, а управляющие входы соединены вместе и образуют управляющий вход блока, линию 4 задержки, состоящую из последоват.ельно соединенных ячеек памяти, выход каждой из которых является входом линии задержки и соединен со входом последующей ячейки памяти, и подключенную своими входами в обратном порядке к выходам третьего блока 3 ангшоговых ключей, линию 5 задержки, состоящую из последовательно соединенных ячеек памяти, выход каждой из которых является выходом линии задержки и соединен со входом последующей ячейки памяти, первый блок 6 аналоговых ключей, у которых сигнальные входы являются входами блока и соединены в прямом порядке с выходами первой линии .5 задержки, управляющие входы являются управляющими входами блока, а выходы - выходами блока, сумматор 7, блок 8 умножения, аналоговый ключ 9,, интегратор 10 со схемой сброса, аналоговый ключ 92,, сумматор 11, выход кото.рого является первым выходом устройства, и блок 12 преобразования частоты, у которого выход является вторым выходом устройства, а дополнительный вход соединен с дополнительным выходом масштабного блока 1, соеди- ненные последовательно линию .13 задержки, подключенную входом к второму выходу масштабного блока 1 и состоящую из -последовательно соединенных ячеек памяти, выход каждой из которых соединен со входом последующей ячейки па.мяти, второй переключатель П 2, линию 14 задержки, состоящую из последовательно соединенных ячеек памяти, выход каждой из которых является выходом линии ззд..ержки и соединен со входом последующей ячейки памяти, блок 15 аналоговых ключей, у которых сигнальные входы являются сигнальными входами блока и подключены в обратном порядке к выходам второй линии 14 з адержки,Управляющие.входы являются управляющими входами,а выходы - выходами блока,и сумматор) 16,выход которого соединен со вторым входом блока 8 умножения,последовательно соединенные третий аналоговый ключ 17,си нальный вход которого соединен с сигнальным входом первого аналогово го ключа 9 и подключен к выходу блока 8 умножения, интегратор 18 со схемой сброса и аналоговый ключ 19, выход которого соединен со вторы входом сумматора 11, последовательно соединенный блок 20 управления, у которого дополнительный выход сое динен с дополнительным входом масшт ного блока 1, а третий выход - с управляющим входом 6inoKa 3 аналоговы ключей, генератор 21 тактовых импул сов и распределитель 22 импульсов последовательного действия, выходы которого подключены к соответствующим попарно соединенным управляющим входам первого и второго блоков б и 15 аналоговых ключей, генератор 23 импульсов, у которого вход соеди нен со вторым выходом блока 20 упра ления, дополнительный вход - с дополнительным выходом генератора 21 тактовых импульсов, первые выходы подключены к управляющим входам каждой ячейки памяти линии 5, 2 и 4 задержки, а вторые выходы - к управ ляющим входам каждой ячейки памяти линий 13 и 14 задержки, дополнитель ный распределитель 24 импульсов управления, у которого вход соединен с последними управляющими входа ми блоков б и 15 аналоговых ключей и подключен к последнему выходу распределителя 22 импульсов, а соответствующие выходы подсоединены к управляющим входам аналоговых ключей 9 , 9JJ, 17 и 19 и интеграторов 10 и 18 со схемами сброса, первый переключатель П 1, соединяющий вход линии 5 задержки с первым выходом масштабного блока 1, переключатель П 2, соединяющий вход линии 14 задер ки через первое положение с выходом пятой линии 13 задержки и через второе положение - с выходом третьей линии 2 задержки, и третий переключатель П 3, соединяющий вход второй линии 14 задержки со вторым выходом масштабного блока 1. Масштабный блок 1 состоит из двух (при вычислении взаимной свертки дву функций и взаимокорреляционной функции между двумя сигналами) или из одного канала {при вычислении автосвертки и автокорреляционной функции сигнала) и содержит, в частности, перестраиваемые по частоте входные цепи со ступенчатыми делителями напряжения, смесители, перестраиваемый по частоте гетеродин (или гетеродины и усилители с регулируемыми коэффициентами усиления. При необходимости каналы дополнительно могут содержать автоматические схемы перестройки (или подстройки) частот гетеродинов и автоматические схемы регулировки амплитуд выходных напряжений. Каждая ячейка памяти дискретноаналоговых линий 2, 4, 5, 13 и 14 задержки состоит из дйух аналоговых запоминающих схем, работающих по двухтактному принципу, и ылходного согласующего усилителя. Блок 12 преобразования частоты состоит, например,ИЗ смесителя, к которому дополнительно подводится колебание гетеродина масштабного блока 1 и выходного усилительного тракта. Блок 20 управления предназначен для ввода в режим работы масштабного блока 1, отпирания через каждый интервал времени Т- At (п-1) ut на длительность д t аналоговых ключей блока 3, ввода в режим работы геиератора 21 тактовых импульсов и генератора 23 импульсов и автоматического изменения частоты повторения вырабатываемых этими генераторами импульсов. Блок 20 состоит, например, из функционально связанных между собой задающего генератора и схем управления на элементах дискретной техники. Генератор 23 импульсов предназначен для выработки двух серий импульсов, сдвинутых относительно друг друга на интервал времени -.t (где At - интервал отсчета по Котельникову) кбторые управляют работой дискретноаналоговых линий 2, 4., 5, 13 и 14 задержки, ;И состоит,, например, из генератора тактовых импульсов с перестраиваемой частотой, работа которого непрерывно синхронизируется импульсами, поступанмцими с дополнительного выхода генератора 21 тактовых импульсов на дополнительный вход генератора 23 импульсов, и четырехканального распределителя импульсов последовательного действия, длительность импульсов на выходах которого равна At и выходы которого подсоединены к первым илходам непосредственно и со сдвигом Ha-jAt ко вторым выходам генератора 23 импульсов (на чертеже подводка управляющих импульсов к ячейкам памяти линий 2, 4, 5 и 13, 14 задержки символически показана одной линией). Блок 24 предназначен для поочередного отпирания аналоговых ключей 9, 19 и 9, 17 и управления сбросом интеграторов 18 и 10, Устройство работает следующим образом, В момент времени t О первый блок 20 управления вводит в режим работы масштабный блок 1, генератор 21 тактовых импульсов, который начинает вырабатывать запускающие импульсы с периодом повторения , и генератор 23 импульсов. В результате этого на выходах оас(пределителя 22 импульсов появляются канальные импульсы с периодом повторения -я-At пдГ и длительностью Atr которые последовательно во времени отпирают на интервал А С с периодом повторения t аналоговые ключи бло кОв б и 15, а на первых и вторых выходах генератора 23 импульсов со сдвигом на интервал появляются импульсы с периодом повторения 2 л t и длительностью .t, крторые начинают управлять работой ячеек пс1мяти линий б, 2, 4 и 14, 13 зфцержки со сдвигом по времени на интервал j-u.t. Если при этом в первого интервала длительност iiAt, например, аналоговые ключи 9 и ;19 открыты под воздействием имп4 льсов блока 24 управления, то при поступлении на вход этого блока канального импульса с последнего выхода распределителя 22 имП1 льсов последней вырабатывает новые импуль си управления, под действием которых происходитмгнйвенHfcte сброс интегратора 18 rta нуль и открывгиотся на. интервал времени At аналоговые ключи Э. и 17. интервал времени при поступлении на вход блока 24 управлеН1|я канального импульса с п-го вых4да распределителя 22 импульсов последний снова вырабатывает имп5 льсы управления, под действием кбторых происходит мгновенный сброс иЕ тегратора 10 на нуль и открываются, на интервал времени д1 аналог вые ключи 9, и 19. : В момент времени сигналы f, ( и :f 2; (t) через входы устройства, поступают в маоатабный блок 1, гДе происходит преобразование до необхддимых значений средних частот их сйектров и усиление по амплитуде заданных значений преобразованны по частоте сигналов f (t) и f(t}. G первого и второго выходов маештабного блока 1 сигналы f(t) и .(t) поступгиот на входы соответст В0ННО линий 2 и 13 задержки, распространяясь далее вдоль этих линий При этом через интервалы времени At HAt-b на шлходах первых ячеек памяти, через интервалы време ни 2 А t и ut на выходах вторых ячеек памяти, через интервалы време ни (n-l) A,t и 2i At на выходах (п -1)-ых ячеек памяти соответствен go линий 2 к 1.3 задержки появляются последовательно во времего на интер вал At . значения соответствующих выборок ),5/Ш,.., ( (.tl...,()V в момент времени t Т - t под воздействием управляющего импульса длительностью At блока 20 открывают ся аналоговые ключи 3, 3,2,, .... 3 , Зу блока 3, и выборки А с выходов линии 2 згщержки в течение интервгша поступают на соотвегствующие входы линии 4 Зсщержки, продвигаясь Дсшее вдоль этой линии в порядке C4i3Uh- t3,...,(,,(o7,, которые, начиная с момента t Т- лt поступают на вход линии 5 задержки. В этот же момент времени последовательность выборок В через первое положение переключателя П 2 поступает на вход линии 14 задержки. Так как при этом значения выборок f fdi-lJAtl fj tt) , f-j (0) и значения выборок В появляются последовательно во времени на выходах соответственно линий 5 и 14 задержки на встречных направлениях, то до момента времени t t + , где t Т+ 3zl дt через аналогоыле ключи 6, Gj ,...., п-1 И блока б и сумматор 7 и через аналоговые ключи 15, 15,, .,., 15.., 15 блока 15 и сумматор 16 соответственно на первый и второй входы блока 8 умножения поступают последовательно во времени сначала выборки сигнала f-iCf-t} и нули, а затем нули и выборки сигнала f (t). В момент времени на выходах к+1, к, ..., 2, 1-м линии 14 задержки появляются на интервал времени А t соответственно выборки В, f() сигнала f (t) , которне в прямом порядке за интервсш времени -j-At через аналоговые ключи ISj, .,.., 15t,, I5n блока 15 и сумматор 16 подводятся последовательно во времени на интервал йС ко второму входу блока 8 умножения, к первому входу которого в течение зтого же интервала 1/2 At через аналоговые ключи 6, 62,...; 6jt, к-и блока б и сумматор 7 подводятся последовательно во времени на интервал соответственно выборки f(n-k-l) At, f3(n-k) u.t ,..., fl(n-2)At, f(n-1) u.t сигнсша f-5(T-t) с выходов 1, 2, .,.,. к, (к-И)-го линии 5. задержки При этом на выходе .блока 8 умножения образуется результат fg (n-l)u.t f( 5-u.t ) длительностью л который через открытый аналоговый ключ, например 17, поступает на вход интегратора 18, в результате чего на его выходе образуется значение u-tfo Hn-l) At)-f( t) В момент времени t t- + u.t под воздействием канального импульса с п-го выхода распределителя 22 импульсов блок 24 управления вырабатываеимпульсы, которые мгновенно сбрасялв ют на нуль интегратор 10 и открываю аналоговые ключи 9 и 19. в результате этого значение Aff(n-l) Atl- u.t) с выхода интегратора18 через анало говый ключ 19 и сумматор 11 в течение интервала действует на первом выходе устройства и на входе бло ка 12 преобразования частоты. В этот же момент t t + At на выходах к+2, к+1, ...,, 2, 1-ом линии 5 згщержки появляются на интервал времени At соответственно, выборки fat (п-1) д. t , f (n-2)a.tl,... f(n-k-l) u.t, f(n-k-2) л.Ъ сигн ла f(T-t), которые в обратном порядке за интервал времени 4- u.t чере аналоговые ключи 6, бд, ,..., б), 6(. блока 6 и сумматор 7 подводятся последовательно во времени на интервал -j к первому входу блок 8 умножения, ко второму входу которого в течение этого же интервала At через аналоговые ключи 15к+1, п блока 15 и сумматор 16 подводятся последовательно во времени на интервал &.tr соответственно выборки В.,,фсигнала f (t) с выходов к+1, к,..., 2, 1-г линии 14 задержки. При этом на выходе блока 8 умножения образуются последовательно во времени результа ты ) At ), f,(n-l) u. t} f(At) длительностями AtT, которые через открытый аналоговый ключ 9-1 поступают на вход интегратора 10, в результате чего на его выходе обраэуется значение Аг jf )) в момент времени t t. под воздействием канального импульса с п-го выхода распределителя 22 импул сов блок 24 управления вырабатывает импульсы, которые мгновенно сбрасывают на нуль интегратор 1В и открывают аналоговые ключи 9 и 17, в ре зультате чего значение ,Ch-2 At iAtV4n-,)At fjgAt с выхода интегратора 10 через аналоговый ключ 9а и сумматор 11 в течение интервала воздействует на первом выходе устройства и на входе блока 12 преобразования частоты.В этот же момент времени t на выходах к+2, к+1,...2, 1-ом лини 14 задержки появляются интервал вре мени At соответственно выборки BjKti/a сигнала f (t) , которые в прямом порядке за интервал времени At через аналоговые ключи блока 15 и сумматор 16 подводятся , последовательно во времени на интервал At: ко второму входу блока 8 умножения, к первому входу которого в течение этогоже интервала t через аналоговые ключи блока 6 и сумматор 7 подводятся последовательно во времени на интервал AT соответственно выборки f J (п-k-2)AtJ , f3(n-k-l) At,...., з(п-2) At, f3(n-l)At сигнала f(T-t) с выходов 1, 2, ...,, к+1, (к+2)-го линии 5 задержки. При этом на выходе блока 8 умножения образуются последовательно во времени результаты |n-3: At(iAt) ,сп-2)), ) длительностями AtT, которие через открытый аналоговый ключ 17 поступают на вход интегратора 18, в результате чего на его выходе образуется зна 1ение ) f,() в момент времени t t 2 At по описание вьше методике значение r|t,,Ur,)+(n-2lAt(|At)+ (n-i)At( С выхода интегратора 18 через аналоговый ключ 19 и сумматор 11 в тече- ние интервала 1/2 At действует на первом выходе устройства и на входе блока 12 преобразования частоты. Из приведенного описания работы устройства видно, что, начиная с . момента времени t д. t, через каждалй интервал 1/2 на первом выходе устройства и на входе блока 12 преобразования частоты появляется и существует в течение длительности времени 1/2 At значение вычисленного результата взаимокорреляционной функции между сигналами ) и f (t) , которое описывается выражением4,Et3--A-r S f )л1, lUJ S-1- J где t t 2т - |-At 0: -y-i2n-2 ; 0 m Sn -1; наибольшая длительность сигналов fo,(t) и f4(t) , совпадающим с точностью до постоянного множителя с результатом, полученным после вычисления корреляционного интеграла ) -|f )dr (051tsT-, О ts 2T-) по формуле прямоугольников или трапе ций, если только в последнем в два раза уменьшить масштаб по оси t, а следовательно,., и по оси t . После восстановления прежнего (ил заданного) значения средней частоты cnieKTpa сигнала у t в блоке 12 пре образования частоты на втором выходе устройства образуется следующее окончательное значение результата у t AS f (П-Т) f-Z.- f T).t (A 0) г ко;торый является приближенным вычислфием дсорреляционного интеграла y(fc) 1 f (T-izr). t--r)-d-r , если T(5ibKO в последнем в два раза уменьшить масштаб по осям t и t. Приведенное описание работы устрсэйства справедливо и тогда, когда f(t)f2.(t) f(t); f (t) f,, (-t)-, f (t) -f (-t), f2(t) f,(-t) , fa(t) -f2(-t). При выполнении условия f (t) f2(t) f(t) можно соединить межд собой входы масштабного блока 1, а также его первый и второй выходы и переключатель П 2 поставить в пол жение два. При вычислении ингеграла свертки у( t) l f (C)f(t--C) . dr необходимо разомкнуть переключатель П 2 и замкнуть переключатели П 1 и ИЗ. Таким образом, введение новых элементов и блоков, установление новых связей выгодно отличает предлагаемое устройство от известных, т как дает возможность наряду с вычис лением интеграла свертки обеспечить вычисление корреляционных функций,и следовательно, расширить функциоиал нще возможности устройства и.класс решаемых с его помощью задач. В результате существенно расширяется область применения и отпадает необходимость в разработке целого ряд одноканальных и многоканальных устройств, с помощью которых могут быт решены только частные задачи, что улучшает технико-экономические пока затели при изготовлении -и эксплуатйции устройства. Формула изобретения Устройство для вычисления свертк о ункций, содержащее масштабный блок первый и второй входы которого являются соответствующими входами уст ройства, а первый выход соединен со входом первой линии задержки, выпол ненной в виде последовательно соеди ненных йчеек памяти, блок управлени первый выход которого соединен со в дом генератора импульсов, первый выход которого подключен к управляю шим входам ячеек памяти первой линии Ьадержки, распределитель импульсов, блок умножения, первый сумматор, выход которого соединен с первым входом блока преобразования частоты, отй и чающе ее я тем, что, с целью расширения функциональных возможностей за счет вычисления корреляционных функций, в устройство введены генератор тактовых импульсов, четыре линии задержки, выполненные в виде последовательно соединенных ячеек памяти, три блока ключей, два сумматора, два интегратора, четыре ключа, дополнительный распределитель импульсов и три переключателя, при этом информационные входы первого блока ключей соединены с выходами соответствующих ячеек первой линии задержки, а управляющие входы первого блока ключей соединены со вторым выходом: блока управления, третий и четвертый выходы которого подключены соответственно ко входу генератора тактовых импульсов и к. третьему входу масштабного блока, второй выход которого соединен с первым входом блока преобразования частоты, первый и третий выходы масштабного блока подключены соответственно к неподвижным контактам соот тственно первого и второго переключателей, подвижные контакты которых подключены соответственно к выходу второй и ко входу третьей линии задержки, ко входу четвертой линии задержки и к подвижному контакту третьего переключателя, первый и второй неподвижные контакты которого соединены соответственно с выходом первой и пятой линий задержки, вход последней подключен к третьему выходу масштабного блока, выходы генератора тактовых импульсов соединены соответственно со входом распределителя импульсов и со вторым входом генератора импульсов, второй выход которого подключен к управляющим входам ячеек четвертой и пятой линий задержки, выходы первого, второго и третьего блока ключей соединены соответственно с соответствующими входами ячеек второй линии задержки с соответствующими входами второго сумматора и соответствующими входами третьего сумматора,выходы распределителя импульсов подключены к соответствующим управляющим входам второго и третьего блоков ключей,информационные входы которых соединены с выходами соответствующих ячеек третьей и четвертой линии задержки, выходы второго и третьего сумматора подключены к соответствующим входам блойов умножения, выход которого соединен с информационными входами первого и второго ключа, выходы которых подключены соответственно ко входам перво

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления корре-ляциОННыХ фуНКций | 1978 |

|

SU813458A1 |

| Устройство для вычисления свертки функций | 1977 |

|

SU686038A1 |

| Аналого-цифровой коррелятор | 1981 |

|

SU1019462A1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Устройство для передачи информации со сжатием | 1983 |

|

SU1091206A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Множительное устройство | 1986 |

|

SU1439628A1 |

| Цифровой автокоррелятор | 1982 |

|

SU1020835A1 |

| Аналого-цифровое устройство дляВычиСлЕНия СВЕРТКи фуНКций | 1979 |

|

SU817724A1 |

| Устройство контроля | 1985 |

|

SU1291931A1 |

Авторы

Даты

1980-06-25—Публикация

1978-03-06—Подача