1

Изобретение относится к импульсной технике и предназначено для построения различных логических устройств

Известно устройство, содержащее переключающие п-р-м-транзисторы с инжекционным питанием, база каждого из них соединена с соответствуквдим входом cxeMd и генератором тока, . эмиттера всех п-р-п-транзисторов соединены с шиной нулевого потенциала, а коллекторы соединены вместе 1 .

Известно также устройство, содержащее выходной и переключающие «-р-г -транзисторы с инжекционньм питанием, эмитте{ял которых подключены к шине нулевого потенциала, базы подключены к генераторам тока, база выходного транзистора подключена к первым коллекторам переключающих транзисторов, базы которых соединены с соответствующими входами устройства 2 .

Недостатком известных устройств является невозможность выполнения пороговых функций и вследствие этого невысокие функциональные возможности.

Цель изобретения - расширение функциональных возможностей.

Для достижения поставленной цели в устройство, содержащее выходной и переключающиеН -р-п-транзисторы с инжекционным питанием, эмиттеры которых подключены к шине нулевого потенциала, базы подключены к генераторам тока, база выходного п-Р-«-транзистора подключена к первым коллекторам переключающих W-Р-п-транзисторов, базы которых соединены с соответствующими входами устройства,введены МДП-транзисторы, стоки и истоки каждого из которых соединены соответственно с первым и вторым коллекторами соответствукадего переклю4aKKueroV -Р-п-транзистора, а затворы всех МДП-транзисторов соединены с дополнительными входами устройства.

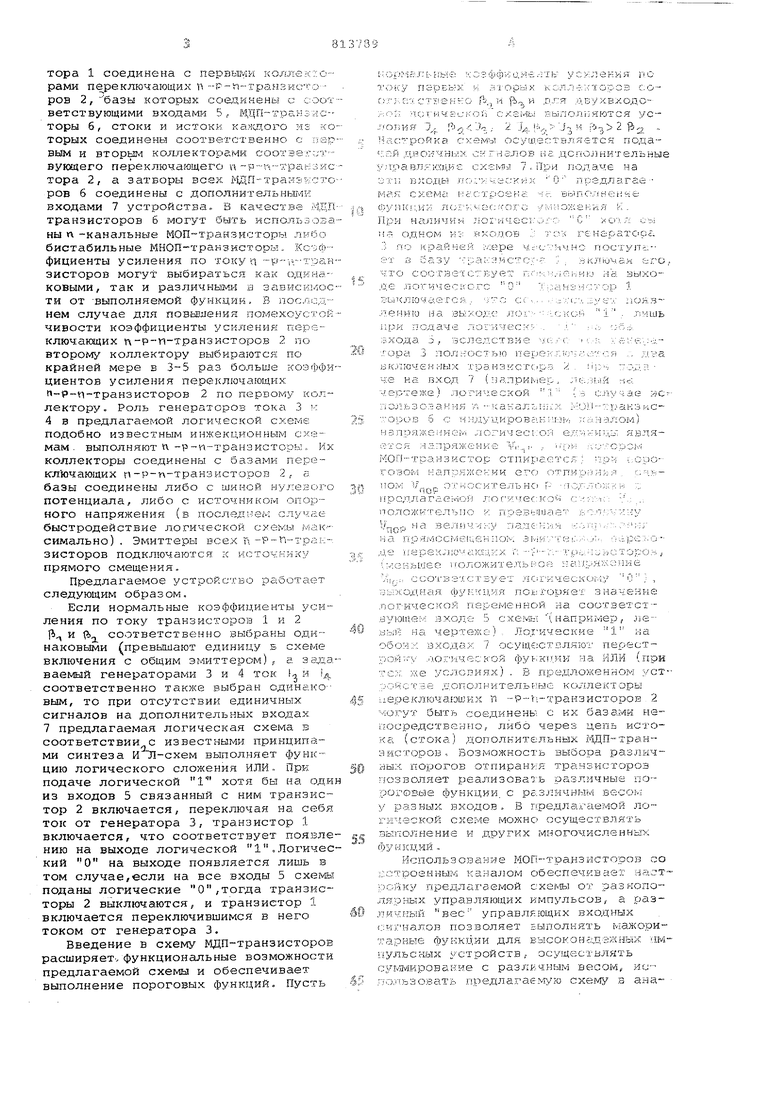

На чертеже представлена принципиальная электрическая схема предложенного устройства.

Схема содержит выходной 1 и переключающие 2 п-р-п-транзисторы с инжекционным питанием, эмиттеры которых подключены к шине нулевого потенциала, база выходного п-Р-«-транзистора 1 подключена к генератору 3 тока, базы переключанвдих т -Р-«-транзисторов 2 подключены к генераторам

0 4 тока, база выходногоп -Р-п-транзистора 1 соединена с первыручи коллег;лорами переключающих ii --Р-п-гранзисгх-о ров 2, базы которых соедуп-гень с с:оот ветствукзщими входами 5 , МДП-тракз йс-торы 6, стоки и истоки ка сдого MS которых соединены соответственно с ijspВЫМ и BTOpialM коллекторами СООТЭе .с:;)вуквдего переключающего vt-р-п-траьзистора 2, а затворы всех ЩП-транэксторов 6 соединены с дополнительнш-П: входами 7 устройства. В качестве МДПтранзисторов 6 могут быть исполгззоБаны п -канальные МОП-транзисторы, либо бистабильные МЕЮП-тракзисторы. Ko-idyфициенты усиления по току п -p-vrТранзисторов могут выбираться как одинаковыми, так и различнь5ми а зависимости от -выполняемой функций. В послед-нем случае для повышения помехоустойчивости коэффициенты усиления переключающих п-р-И-транзисторов 2 по второму коллектору выбираются по крайней мере в 3-5 раз больше коэффициентов усиления переключающих п-Р-П-транзисторов 2 по первому кол-лектору. Роль генератсрОЕ: тока 3 -: 4 в предлагаемой логической схеме подобно известным инжекционньм схемам, выполняют л -р-п-транзксторы.. Их коллекторы соединены с базами пе,секл$очаю дих п-Р-п-транзисторов 2, з базы соединены либо с шиной нулевого потенциала, либо с источником опорного напряжения (в последнем случае быстродействие логической, схемы мак-симально) . Эмиттеры всех п -Р-п--тра -;-зисторов подключаются к источнику прямого смещения.

Предлагаемое устройство ргюотает следующим образом.

.Если нормальные коэффициенты усиления по току транзисто-ров 1 и 2 fi и соответственно выбраны одинаковыми (превышают единицу Е схеме включения с общим эмиттером), а Зсудаваемый генераторами 3 и 4 ток ( и д соответственно также выбран одине коВЫМ, то при отсутствии единичных сигналов на дополнительных входах 7 предлагаемая логическая схема в соответствии с известными принципк-ми синтеза И Л-схем выполняет функ-цию логического сложения ИЛИ. .При подаче логической хотя бы на оди из входов 5 связанный с ним транзистор 2 включается, переключая на себя ток от генератора 3, транзистор 1 включается, что соответствует появлению на выходе логической I Лох-ический О на выходе появляется лишь в том случае,если на все входы 5 схег/ы поданы логические О,тогда транзисторы 2 выключаются, и транзистор 1 включается переключившимся в него током от ген.ератора 3.

Введение в схему МДП-транзисторов расширяет-, функциональные возможности предлагаемой схемы и обеспечивает выполнение пороговых функций. Пусть

о.;.;-): с т Si е к г: о ., и р1„ и .п.гя .О,БУ хвходо (::. ---(:;; г 1-1Ч г; с i-О И c/;Ei ibi Еылолпяются ус - .rioisKST Ъ 2 J,s. ..-, и ., ,. Нас: ройка скемы осушествлявтся пода::г;й дйоичпых скгнблов Не дспо:1кительные y;ipaBn;- -i«.ii,Pi cxEMtsi 7. При полаче на ЭА-1 в5;одь-1 rK;,;:,: :i;CK;-;.K О- предлагаемая схема - cCTpcsne -;-. выпо.-(неийе

(,:,K;-v Tiiy:.r(ii:f:fOr с -/М ЮХСеКлЯ к.

при наличи:-1 лохичас;.--..:-с. С :о-л;; оы одном и;: вхо.пов . ;-о ; гвнаратс сг. .J по крайней ;v,:epe ч;с-.;-1чно noc-ryni.-ЭТ Д оаЗу С PCU-v М СТС/- - . /:jK7iHj4ci i b/iQ

-что сос-гвет ciTEy ет гу--:-;, :.-;f-;i-ii-ir;j Ни аыхоэиключае.гсй. . сх i. -::.-.-1.--..;.ye-. .;1еииш на выхох,; .по.у --- -.ской i - .лишь при подаче ло -зческ--- . у : ,; . Злода .3, аслелствие /(;...-(-. ; ;:. :.-;;;,--е-:-.-..ора 3 полностью 17е1:.)е:и.;:; -;-чучу оя .. ,yva 8К.)лЮчен ных транзкс-горв : : ;;:-1 ЗД;-;че на вход 7 (иаприь ер, ..:::,Й ни -ч;еоге)ке) логической 1 j с..е :яс::-iOJ b3G;-;ания У, -ка.кал;л:кх О; --:ракзкс- -;.-opo.B 6 с ijy.iyuHpoBciK:-гjr/i ууналом) нзпряжегЛтег.-. .логичесго:- eK---iHirij,b-; яв.ляятся лгпряжение vr.,.- , :;;j-.4;DOki МОП-транзистор отпкреетсй ; прч v oijoroBOM капряжекии его отпи-оуил я ,уь1|рсдлаг емон т:огичес::т( гу.-:-;-- :: -.-.: по.ложигелы о к поевьчиае -- ь--у--|,У:--- ну Vripo -i вел,иччг:у :ja.at :.ч i :у .. . :-:у ;у

.и,е иерек;по-кю цух. г; ---у--г.- .-;.J, ;у;)сторо , ;у:еньшее коложите.пы-ое ;;а11ияк;упие ,-1,,:: ссо1вэ.(стзует лс гкческоку О--,- , ;1у;:к;одная функция лоьгоряет зиа-чение .погической переменной на соответстйуюшеУ: входе 5 cxeNH например, пеиый на чер-тежЕ;) Ло.гические 1 на обоих входах 7 осущ€;ствля;о1 перестpoMiv аогичег;кой фуь;кции на ИЛИ (при тс::: ухе услсгэиях) . В предложенном уст-;;ойстйе дополнительные коллекторы иереключаюших ii -р-ту-транзисторов 2 /югут быть соединены с их базами непосредственно, либо через цепь истока (стока) дополнительных г-ЩП-транэисгторов , Возможность -выбора различных порогов отпирания транзисторов позволяет реализовать различные по-роговые функции, с рг зличным весок у разных входов. В предлагаемой логической схеме можно осуществлять зыполнение и других многочисленных функций.

Использование МОП-транзисторов со ::строенным каналом обеспечиваег наст-:)ойку предлагаемой схег-ы от разкополярных управляющих импульсов,- а различный вес управляющих входных г:ч1:налов позволяет выполнять ыэлюртлхарные функции для ЕЫСОКОНЙД-ЗННЫХ чмпульсных устройств, осуществлять оуммировакие с различным весом, иипользовать предлагаемую схему в аналого-цифровых и цифроаналоговых преобразователях. При этом общее число компонентов в предлагаемой логическо схеме при выполнении многочисленных логических функций существенно умень шается по сравнению с известными логическими схемами, а применение МНОП-транэисторов позволяет сохранит в течение длительного времени осуществленную настройку схемы на ту или иную ыпсхлняемую функцию при отключении управляющих импульсов.Наиболее эффективной областью применения предлагаемой логической схемы яв ляются многоуровневые логические и запоминающие схемы с перестраиваемой структурой, ассоциативные микропроцессоры и однородные вычислительные среды. Формула изобретения . Логическая схема, содержащая выходной и переключающие п-р-п-транзис торы с инжекционным питанием, эмитте ры которых подключены к шине нулевого потенциала, базы подключены к генераторс1м тока, база выходного П-р-п-транзистора подключена к первым коллекторампереключающих П -р-п-транзисторов, базы которых соединены с соответствующими входами устройства, отличающаяся тем, что, с целью расширения функциональных возможностей, в устройство введены МДП-транзисторы стоки и истоки каждого из которых соединены соответственно с первым и вторым коллекторами соответствующего переключающего п-р-п-транзистора, а затворы всех МДП-транзисторов соединены с дополнительными входами устройства. Источники информации, принятые во внимание при экспертизе 1.Заявка Франции 2316804, кл. Н 03 К 19/08, 1977. 2.Аваев Н.А.,Дулин В.Н.1аумов Ю.Е. Большие интегральные схемы с инжекционным питанием. М., Советское радио, 1977, с. 121, рис. 4 и 3 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| Преобразователь уровней | 1983 |

|

SU1094150A1 |

| Преобразователь логических уровней | 1985 |

|

SU1252936A1 |

| Логический элемент на биполярных и МОП-транзисторах | 1988 |

|

SU1615877A1 |

| Моп-ттл транслятор | 1979 |

|

SU836797A1 |

| ЛОГИЧЕСКИЙ ВЕНТИЛЬ | 2014 |

|

RU2546302C1 |

| Логический элемент на биполярных и МОП-транзисторах | 1988 |

|

SU1598156A1 |

| ОПТОЭЛЕКТРОННОЕ РЕЛЕ | 2013 |

|

RU2522861C1 |

| Инвертор | 1991 |

|

SU1817240A1 |

| ИНТЕГРАЛЬНАЯ СХЕМА СИЛОВОГО БИПОЛЯРНО-ПОЛЕВОГО ТРАНЗИСТОРА | 2015 |

|

RU2585880C1 |

Авторы

Даты

1981-03-15—Публикация

1979-04-27—Подача