1

Изобретение относится к технике передачи дискретной информации и может быть использовано в мног6кана.1ьных системах с ожиданием.

Известно устройство восстановления дискретной информации, которое содержит входной блок, состоящий из N + 1 дискретного согласованного фильтра, N каналов, N выходных триггеров, а также последовательно соединенные блок тактовой синхронизации, формирователь цикловых импульсов и делитель 1 .

Однако такое устройство характеризуется наличием краевых искажений и небольшой достоверностью информации.

Цель изобретения - устранение краевыхискажений и повышение достоверности информации.

Для достижения этой цели в устройство восстановления дискретной информации, содержащее входной блок, состоящий из N + 1 дискретного согласования фильтра, N каналов, N выходных триггеров, а также последовательно соединенные блок тактовой синхронизации, формирователь цикловых импульсов и делитель, введены компаратор синхросигнала и линия задержки, а также в

каждый из N каналов - две параллельные цепи, каждая из которых состоит из последовательно соединенных компаратора, ключевого блока, триггера предварительной памяти и элемента И, и третья цепь, состоящая из последовательно соединенных элемента ИЛИ, ключевого блока, счетчика цикловых импульсов и дешифратора, при этом выход дешифратора каждого канала подключен к нулевым входам триггеров предварительной памяти и вторым входам элементов И, выходы которых подключены к единичному и нулевому входу соответствующего выходного триггера, а единичные выходы триггеров предварительной памяти каждого канала подключены ко входам элемента ИЛИ третьей цепи каждого , причем единичный и нулевой выходы соответствующих- дискретных согласованных фильтров подключены ко входам компараторов первой и второй цепи каждого канала, а выход N + 1 дискретного согласованного

фильтра подключен ко входу компаратора синхросигнала,, выход которого подключен ко входу блока тактовой частоты и через линию задержки - к управляющим входам ключевых блоков третьей цепи

всех каналов, а первый выход делителя подключен к вторым входам дешифраторов и ключевых блоков первой и второй цепи всех каналов, второй выход делителя подключен к счетным входам счетчика цикловых импульсов каждого канала.

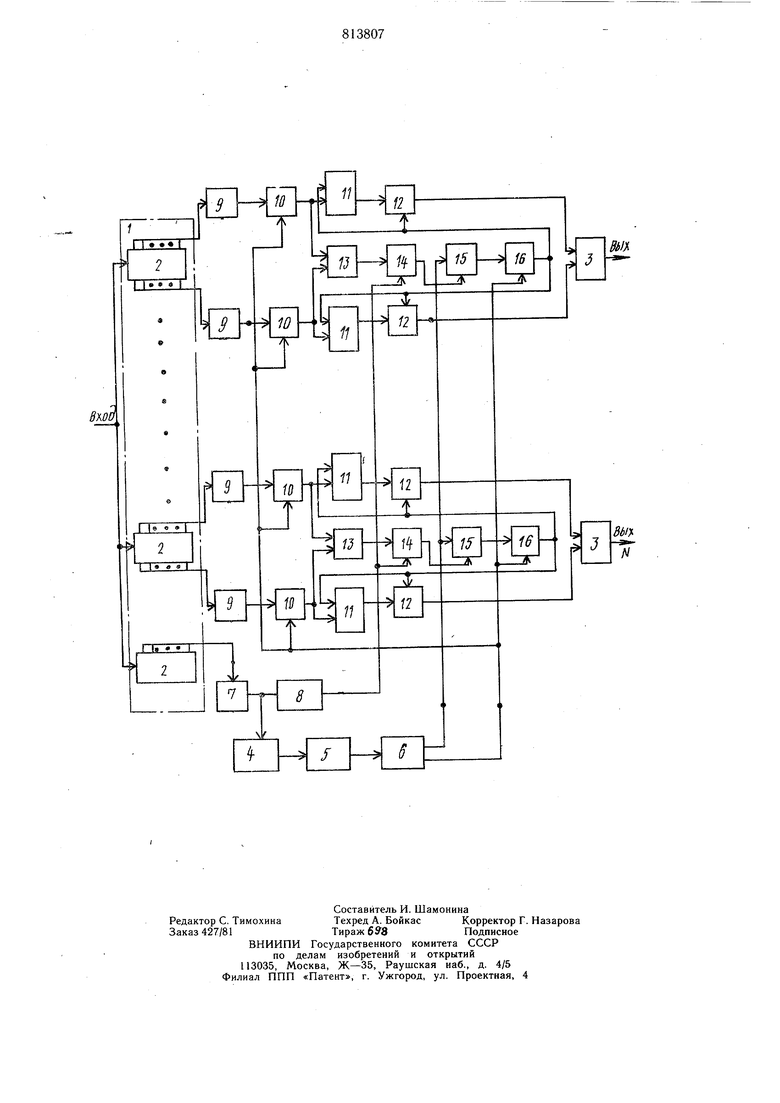

На чертеже изображена структурная электрическая схема предложенного устройства.

Устройство содержит входной блок 1, состоящий из N + 1 дискретных согласованных фильтров 2, N выходных триггеров 3, а также блок 4 тактовой синхронизации, формирователь 5 цикловых импульсов, делитель 6, компаратор 7 синхросигнала, линию 8 задержки N параллельных цепей, каждая из которых состоит из компаратора 9, ключевого блока 10, триггера 11 предварительной памяти и элемента И 12. Устройство содержит также N цепей, каждая из которых состоит из элемента ИЛИ 13, ключевого блока 14, счетчика 15 цикловых импульсов и дешифратора 16.

Принцип работы предложенного устройства заключается в следующем.

При синхронном способе передачи, реализованном на передающей стороне, на вход блока 1 на каждом цикле поступает либо один из двух N канальных сигналов, либо синхросигнал в виде циклической сдвижки М-последовательности, не принадлежащей ни одному из каналов. На выходе N -го дискретного согласованного фильтра 2 отклик появляется в случайные моменты вре мени, кратные длительности цикла Т . Два N канальных сигнала необходимо для раЗ личения возможных смен состояний источников сообщений. В данном случае могут использоваться прямая и инверсная циклические сдвижки М-последовательности длиной L + 1,. где N число каналов в системе.

Работа устройства начинается с момента прихода сияхросигнала, т. е. после появления на дискретном согласованном фильтре N + 1 канала отклика, который нормализуется компаратором 7. Нормализованный синхроимпульс, пройдя через линию 8 задержки на цикл, поступает параллельно на управляющие входы ключевых блоков 14 всех N каналов и одновременно - в блок 4 тактовой синхронизации для подстройки местного тактового генератора. При поступлении на очередном цикле по групповому тракту сигнала о смене состояния источника, например первого канала, на выходе соответствующего фильтра 2, появляется отклик. Если передавался сигнал о смене состояния источника из «О в «1, то отклик фильтра 2 появляется на первом выходе, а если из «1 в «О - на втором. С соответствующего выхода фильтра 2 отклик поступает на один из двух соответствующих компараторов 9, в которых принимается решение, по какому из выходов согласованного фильтра 2 поступила информация. Нормализованный импульс поступает через соответствующий ключевой блок 10, который управляется тактовой последовательностью,

поступающей с первого выхода делителя 6, на единичный вход одного из триггеров 11, который запоминает переданное состояние, и через логический элемент ИЛИ 13 на ключевой блок 14, который управляется задержанными на цикл синхроимпульсами, поступающими с линии 8 задержки: При совпадении задержанного на цикл синхроимпульса и пришедшего на очередном цикле канального импульса происходит установка на ноль счетчика 15, который со следующего

такта начинает считать тактовые импульсы. С этого момента начинает работать схема восстановления первого канала. При полном заполнении счетчика 15, которое определяется дешифратором 16, происходит формирование импульса истинного момента регенерации (ИМР), который поступает с выхода дешифратора 16, управляемого тактовой последовательностью импульсов, поступающих с первого выхода делителя 6 на элемент И 12 и вторые входы триггеров 11.

5 В зависимости от того, на какой из элементов И 12 был подан управляющий потенциал с выхода триггера 11, импульс истинного момента регенерации проходит на триггер 3 для установки его в «1 или «0 состояние. Состояние триггера 3 опреде° ляется тем, по какому выходу фильтра 2 поступила информация. Импульс ИМР, поступая на вторые входы триггеров 11, устанавливает его в исходное нулевое состояние. С поступлением канального импульса по

5 другому выходу согласованного фильтра 2 аналогичным образом происходит запоминание переданного состояния другим триггером 11, и следующий импульс ИМР поступает уже через другой элемент И 12 на другой вход выходного триггера 3 и ну0 левые входы триггеров 11. Если источник информации не изменяет своего состояния длительное время, т. е. на вход блока уплотнения на передающей стороне поступает подряд несколько «1 или «О, то по данному каналу ничего не передается. Очередные импульсы ИМР, поступая на входы элементов И 12 и нулевые входы триггеров 11, не проходят на соответствующие входы триггера 3. Вследствие этого триггер 3 устойчиво остается в первоначальном состоянии.

50 При полном заполнении счетчика 15 импульсом ИМР производится сброс счетчика в «О.

Если произошла задержка в передаче момента смены состояния в каком-либо ка-нале, пришедший импульс, характеризую щий переход из «О в «1 запоминается, и только в момент прихода ИМР происходит переключение триггера 3 в единичное состояние. Таким образом, происходит «подтягивание каждого канального импульса, характеризующего смену состояния источника сообщений к истинным моментам регенерации данного канала. Восстановление информации каждого последующего канала начинается с момента, когда после прихода синхроимпульса, поступающего с линии В задержки на канальные ключевые блоки 14, на очередном цикле приходит канальный импульс соответствующего i-ro канала и устанавливает счетчик 15 данного канала в «О. «Подтягивание импульсов позволяет устранить явление качания фронтов принимаемых посылок, т. е. восстановить искаженные посылки и повысить достоверность информации. Формула изобретения Устройство восстановления дискретной информации, содержащее входной блок, состоящий из N + 1 дискретного согласованного фильтра, N каналов, N выходных триггеров, а также последовательно соединенные блок тактовой синхронизации, формирователь цикловых импульсов и делитель, отличающееся тем, что, с целью устранения краевых искажений и повыщения достоверности информации, введены компаратор синхросигнала и линия задержки, а также в каждый из N каналов - две параллельные цепи, каждая из которых состоит из последовательно соединенных компаратора, ключевого блока, триггера предварительной памяти и элемента И, и третья цепь, состоящая из последовательно соединенных элемента ИЛИ, ключевого блока, счетчика цикловых импульсов и дещифратора, при этом выход дещифратора каждого канала подключен к нулевым входам триггеров предварительной памяти и вторым входам элементов И, выходы которых подключены к единичному и нулевому входу соответствующего выходного триггера, а единичные выходы триггеров предварительной памяти каждого канала подключены ко входам элемента ИЛИ третьей цепи каждого канала, причем единичный и нулевой выходы соответствующих дискретных согласованных фильтров подключены ко входам компараторов первой и второй цепи каждого канала, а выход N + 1 дискретного согласованного фильтра подключен ко входу компаратора синхросигнала, выход которого подключен ко входу блока тактовой частоты и через линию задержки - к управляющим входам ключевых блоков третьей цепи всех каналов, а первый выход делителя подключен к вторым входам дещифраторов и ключевых блоков первой и второйцепи всех каналов, второй выход делителя подключен к счетным входам счетчика цикловых импульсов каждого канала. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 582573, кл. Н 04 L 3/02, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема дискретной информации | 1984 |

|

SU1238259A1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство синхронизации многоканальной системы радиосвязи | 1990 |

|

SU1739502A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1995 |

|

RU2096801C1 |

| Устройство синхронизации приемника многочастотных сигналов | 1984 |

|

SU1185627A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| ВЕДОМСТВЕННАЯ СИСТЕМА ДВУХСТОРОННЕЙ ВЫСОКОСКОРОСТНОЙ РАДИОСВЯЗИ С ЭФФЕКТИВНЫМ ИСПОЛЬЗОВАНИЕМ РАДИОЧАСТОТНОГО СПЕКТРА | 2016 |

|

RU2650191C1 |

| Устройство для синхронизации многоканальных равнодоступных систем связи | 1977 |

|

SU681566A2 |

| СИСТЕМА ДУПЛЕКСНОЙ ВЫСОКОСКОРОСТНОЙ КОРОТКОВОЛНОВОЙ РАДИОСВЯЗИ | 2013 |

|

RU2553091C2 |

Авторы

Даты

1981-03-15—Публикация

1979-03-12—Подача