1

Изобретение относится к вычислительной и информационно-измерительной технике, а также к системам автоматического управления и может найти применение в системах числового программного управления, а также в измерительных и вычислительных устройствах.

Известен цифровой интегратор параллельного переноса, содержащий регистр управляющего кода и накопительный сумматор 1.

Недостатком этого устройства является сложность конструкции.

Наиболее близким к предлагаемому по технической сущности является цифровой интегратор, содержащий М-разрядный регистр, выходы N младщих рязрядов которого подключены к первым N входам логического блока умножителя, N-разрядный счетчик, вход которого соединен с входной щиной, а выходы - с вторыми N входами логического блока умножителя 2.

Недостатком его является большая погрешность, вызываемая неравномерностью следования импульсов на выходе.

Цель изобретения - повышение точности.

Для достижения указанной цели в циф ровой интегратор, содержащий /Vl-разрядный регистр, выходы N младших разрядов которого подключены к первым входам логического блока умножителя, N-разрядный J счетчик, вход которого соединен с входной шиной, а выходы - с вторыми входами логического блока умножителя, введен накопительный сумматор, тактовый вход которого подключен к входной шине, вход переноса -к выходу логического блока умножителя, кодовые входы - к выходам M-N старших разрядов М-разрядного регистра, а выход - к выходной шине.

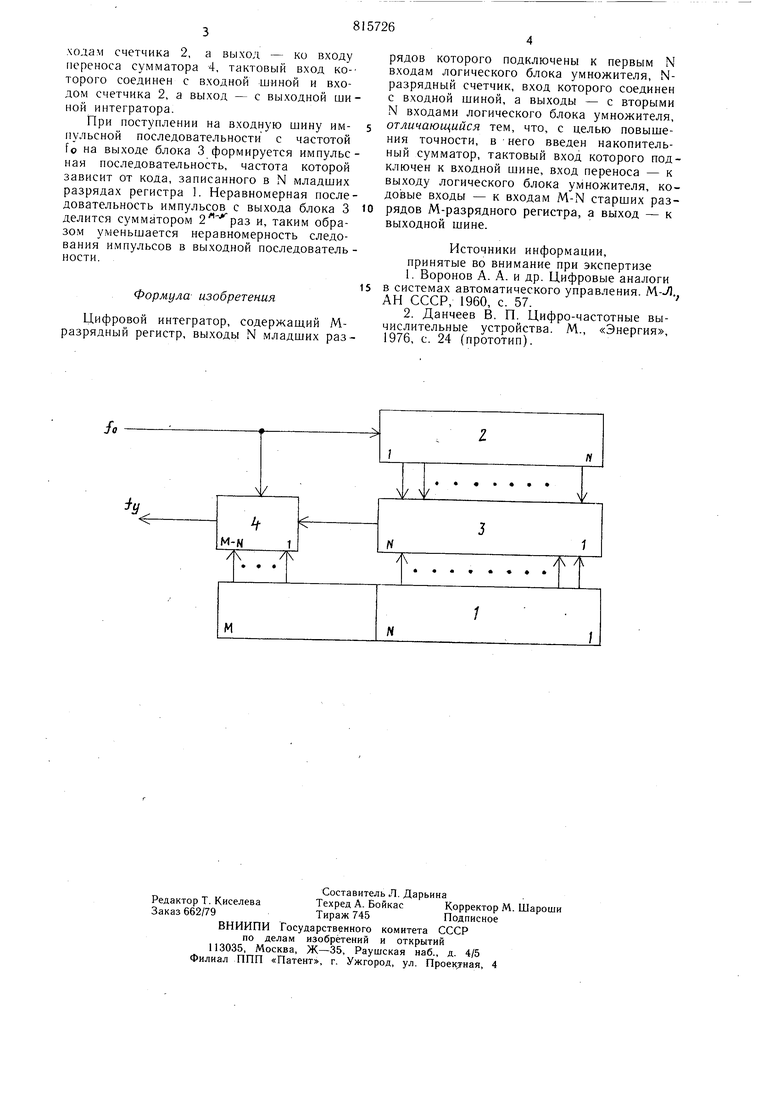

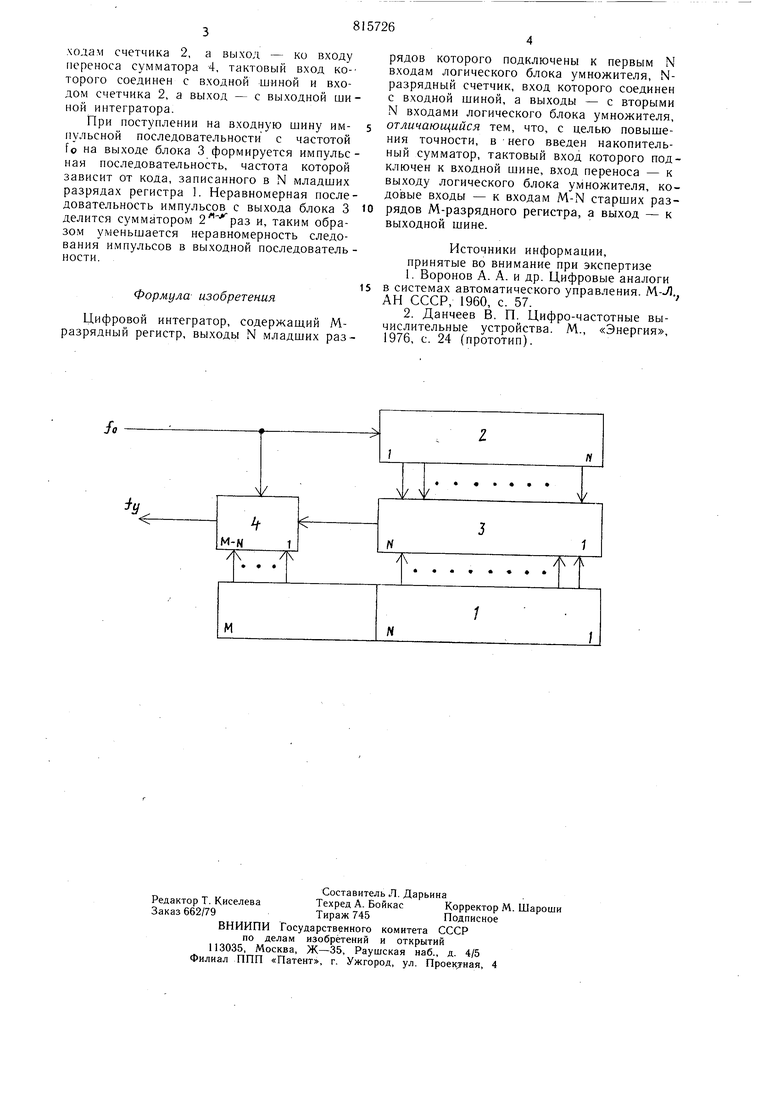

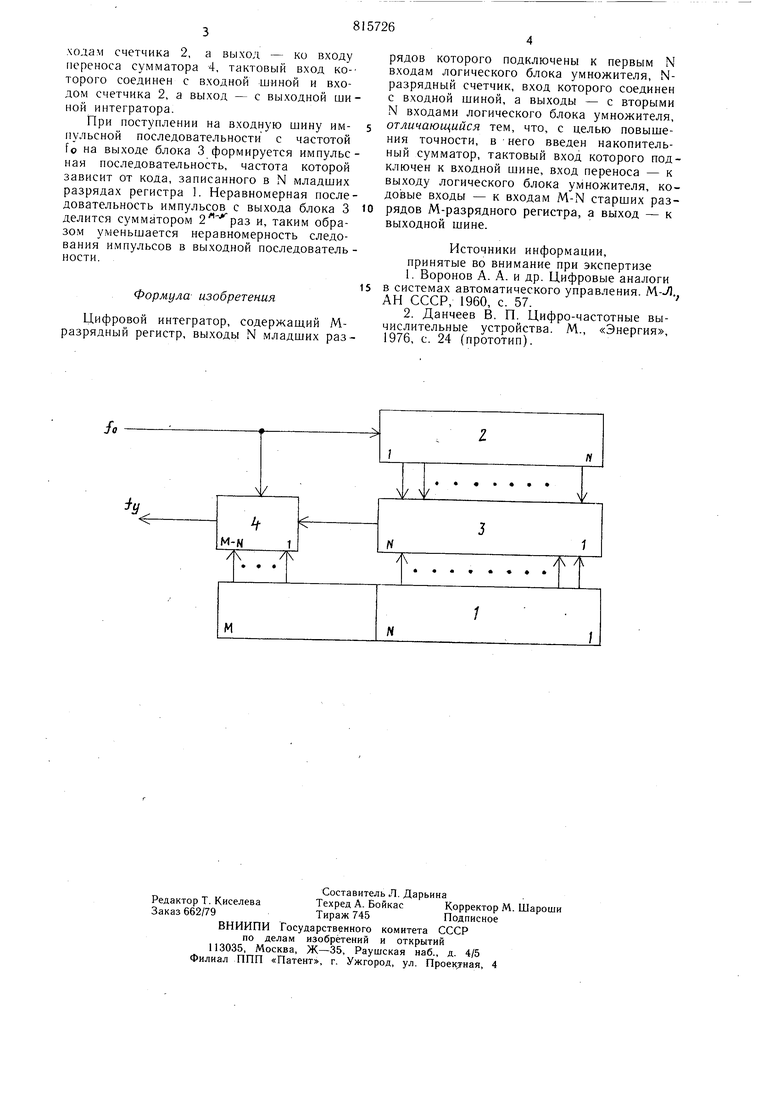

На чертеже представлена функциональная схема цифрового интегратора.

Цифровой интегратор содержит М-раз5 рядный регистр 1 управляющего кода, Nразрядный счетчик 2, логический блок 3 умножителя и накопительный сумматор 4. Выход сумматора подключен к выходной щине.

Выходы M-N старщих разрядов регистра 1 подключены к кодовым в.ходам накопительного сумматора 4, а N младших разрядов - к N первым входам блока 3, N других в.ходов которогоподключены к выходам счетчика 2, а выход - ко входу переноса сумматора 4, тактовый вход которого соединен с входной гииной и входом счетчика 2, а выход - с выходной шиной интегратора. При поступлении на входную шину импульсной последовательности с частотой fo на выходе блока 3 формируется импульс ная последовательность, частота которой зависит от кода, записанного в N младших разрядах регистра 1. Неравномерная последовательность импульсов с выхода блока 3 делится сумматором и, таким образом уменьшается неравномерность следования импульсов в выходной последователь ности. Формула изобретения Цифровой интегратор, содержащий Мразрядный регистр, выходы N младших разрядов которого подключены к первым N входам логического блока умножителя, Nразрядный счетчик, вход которого соединен с входной шиной, а выходы - с вторыми N входами логического блока умножителя, отличающийся тем, что, с целью повышения точности, в него введен накопительный сумматор, тактовый вход которого подключен к входной шине, вход переноса - к выходу логического блока умножителя, кодовые входы - к входам M-N старших разрядов М-разрядного регистра, а выход - к выходной шине, Источники информации, принятые во внимание при экспертизе 1.Воронов А. А. и др. Цифровые аналоги в системах автоматического управления. M--/J.. АН СССР, 1960, с. 57. 2.Данчеев В. П. Цифро-частотные вычислительные устройства. М., «Энергия, 1976, с. 24 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты периодических импульсов | 1980 |

|

SU935956A1 |

| Цифровой умножитель частоты периодических сигналов | 1984 |

|

SU1231595A1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| Устройство для выделения признаков при распознавании случайных сигналов | 1990 |

|

SU1797134A1 |

| Цифровой фазометр | 1986 |

|

SU1348744A1 |

| Устройство для формирования случайных процессов с заданным спектром | 1981 |

|

SU1027723A1 |

| Преобразователь активной мощности в цифровой код | 1989 |

|

SU1780033A1 |

| Цифровой прогнозирующий фильтр | 1986 |

|

SU1374409A1 |

| ЦИФРОВОЙ СЧЕТЧИК ЭЛЕКТРОЭНЕРГИИ КСР-ТИПА | 1991 |

|

RU2061243C1 |

| Цифровой интегратор последовательного переноса | 1986 |

|

SU1357956A1 |

Л

Авторы

Даты

1981-03-23—Публикация

1978-12-15—Подача