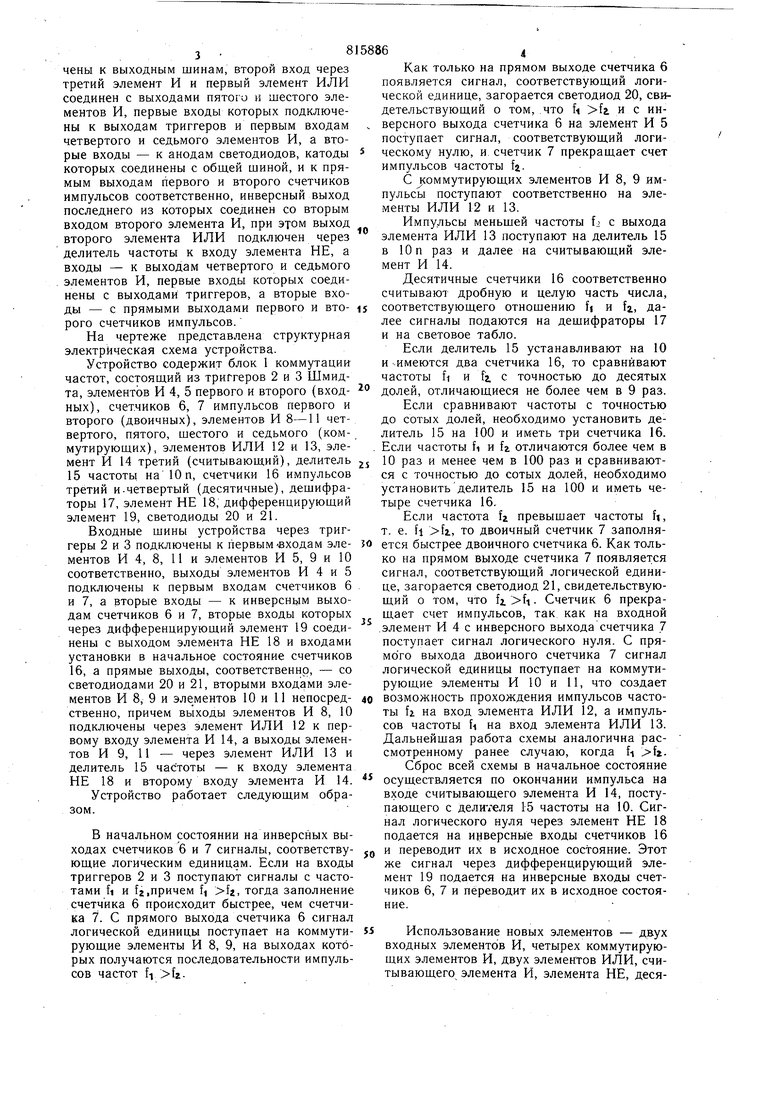

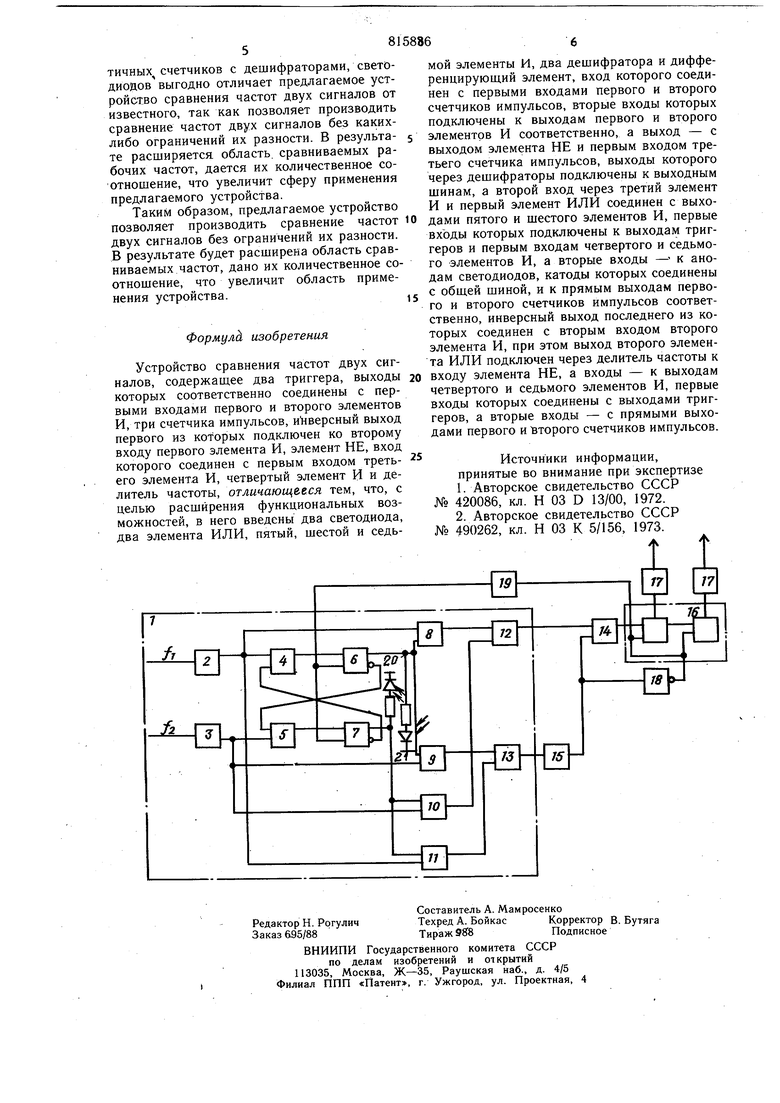

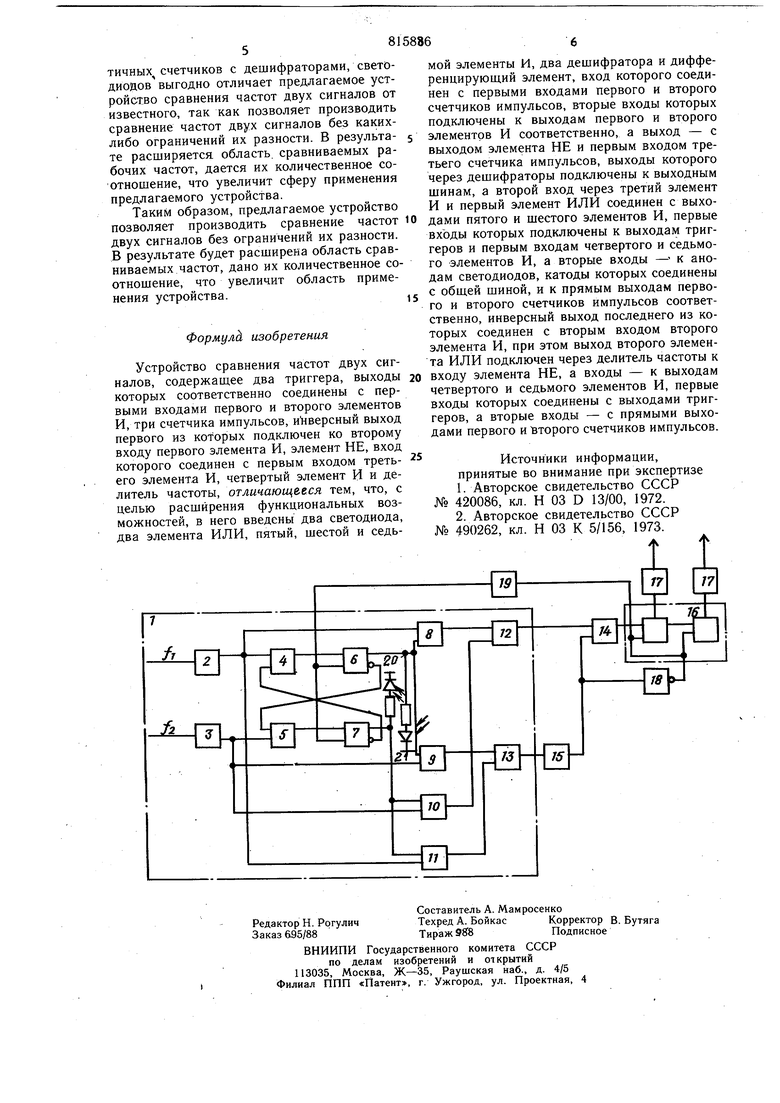

(54) УСТРОЙСТВО СРАВНЕНИЯ ЧАСТОТ ДВУХ ,СИГНАЛОВ чены к выходным шинам, второй вход через третий элемент И и первый элемент ИЛИ соединен с выходами пятого и шестого элементов И, первые входы которых подключены к выходам триггеров и первым входам четвертого и седьмого элементов И, а вторые входы - к анодам светодиодов, катоды которых соединены с общей шиной, и к прямым выходам первого и второго счетчиков импульсов соответственно, инверсный выход последнего из которых соединен со вторым входом второго элемента И, при этом выход второго элемента ИЛИ подключен через делитель частоты к входу элемента НЕ, а входы - к выходам четвертого и седьмого элементов И, первые входы которых соединены с выходами триггеров, а вторые входы - с прямыми выходами первого и второго счетчиков импульсов. На чертеже представлена структурная электрическая схема устройства. Устройство содержит блок 1 коммутации частот, состоящий из триггеров 2 и 3 Шмидта, элементов И 4, 5 первого и второго (входных), счетчиков 6, 7 импульсов первого и второго (двоичных), элементов И 8-11 четвертого, пятого, шестого и седьмого (коммутируюших), элементов ИЛИ 12 и 13, элемент И 14 третий (считывающий), делитель 15 частоть на 10 п, счетчики 16 импульсов третий и.четвертый (десятичные), дешифраторы 17, элемент НЕ 18, дифференцирующий элемент 19, светодиоды 20 и 21. Входные щины устройства через триггеры 2 и 3 подключены к первым-входам элементов И 4, 8, 11 и элементов И 5, 9 и 10 соответственно, выходы элементов И 4 и 5 подключены к первым входам счетчиков 6 и 7, а вторые входы - к инверсным выходам счетчиков 6 и 7, вторые входы которых через дифференцирующий элемент 19 соединены с выходом элемента НЕ 18 и входами установки в начальное состояние счетчиков 16, а прямые выходы, соответственно, - со светодиодами 20 и 21, вторыми входами элементов И 8, 9 и эле ментов 10 и И непосредственно, причем выходы элементов И 8, 10 подключены через элемент ИЛИ 12 к первому входу элемента И 14, а выходы элементов И 9, 11 - через элемент ИЛИ 13 и делитель 15 частоты - к входу элемента НЕ 18 и второму входу элемента И 14. Устройство работает следующим образом. В начальном состоянии на инверсных выходах счетчиков 6 и 7 сигналы, соответствующие логическим единицам. Если на входы триггеров 2 и 3 поступают сигналы с частотами fi и fj,причем fi f2, тогда заполнение счетчика 6 происходит быстрее, чем счетчика 7. С прямого выхода счетчика 6 сигнал логической единицы поступает на коммутирующие элементы И 8, 9, на выходах которых получаются последовательности импульсов частот f-| fz. 8 64 Как только на прямом выходе счетчика 6 появляется сигнал, соответствующий логической единице, загорается светодиод 20, свидетельствующий о том, что fi li и с инверсного выхода счетчика б на элемент И 5 поступает сигнал, соответствующий логическому нулю, и счетчик 7 прекращает счет импульсов частоты fj. С j OMмутирующих элементов И 8, 9 импульсы поступают соответственно на элементы ИЛИ 12 и 13. Импульсы меньщей частоты 1 с выхода элемента ИЛИ 13 поступают на делитель 15 в 10 п раз и далее на считывающий элемент И 14. Десятичные счетчики 16 соответственно считывают дробную и целую часть числа. соответствующего отношению f| и fj, далее сигналы подаются на дешифраторы 17 и на световое табло, Если делитель 15 устанавливают на 10 и химеются два счетчика 16, то сравнивают частоты fi и fit с точностью до десятых долей, отличающиеся не более чем в 9 раз. Если сравнивают частоты с точностью до сотых долей, необходимо установить делитель 15 на 100 и иметь три счетчика 16. Если частоты fi и г отличаются более чем в 10 раз и менее чем в 100 раз и сравниваются с точностью до сотых долей, необходимо установить делитель 15 на 100 и иметь четыре счетчика 16. Если частота fa превышает частоты fi, т. е. fi fi, то двоичный счетчик 7 заполняется быстрее двоичного счетчика 6. Как только на прямом выходе счетчика 7 появляется сигнал, соответствующий логической единице, загорается светодиод 21, свидетельствующий о том, что . Счетчик 6 прекращает счет импульсов, так как на входной элемент И 4 с инверсного выхода счетчика 7 поступает сигнал логического нуля. С прямого выхода двоичного счетчика 7 сигнал логической единицы поступает на коммутирующие элементы И 10 и 11, что создает возможность прохождения импульсов частоты fi на вход элемента ИЛИ 12, а импульсов частоты fi на вход элемента ИЛИ 13. Дальнейшая работа схемы аналогична рассмотренному ранее случаю, когда fi гСброс всей схемы в начальное состояние осуществляется по окончании импульса на входе считывающего элемента И 14, поступающего с делителя 15 частоты на 10. Сигнал логического нуля через элемент НЕ 18 подается на инверсные входы счетчиков 16 и переводит их в исходное состояние. Этот же сигнал через дифференцирующий элемент 19 подается на инверсные входы счетчиков 6, 7 и переводит их в исходное состояние. Использование новых элементов - двух входных элементов И, четырех коммутирующих элементов И, двух элементов ИЛИ, считывающего элемента И, элемента НЕ, деся

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования импульсных последовательностей | 1987 |

|

SU1788573A1 |

| Устройство для динамической балансировки лучом лазера роторов | 1983 |

|

SU1130753A2 |

| Устройство компенсации сдвига частот | 1985 |

|

SU1316097A2 |

| Устройство генерации импульсов управления шаговым двигателем с электронной коррекцией | 1991 |

|

SU1829022A1 |

| Устройство для геоэлектроразведки | 1985 |

|

SU1343378A1 |

| Устройство для считывания графической информации | 1989 |

|

SU1683046A1 |

| ПРОТИВОУГОННАЯ СИСТЕМА | 1995 |

|

RU2086437C1 |

| Устройство для измерения средней частоты серии импульсов | 1990 |

|

SU1737356A1 |

| Устройство для передачи и приема дискретной информации | 1980 |

|

SU886295A1 |

| Устройство для сравнения частот сигналов | 1985 |

|

SU1323973A1 |

Авторы

Даты

1981-03-23—Публикация

1979-06-05—Подача