(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСЛЕДОВАТЕЛЬНОСТИ

ИМПУЛЬСОВ

рых и первый вход установки в единицу второго соединены с- шиной тактовых импульсов, инверсный выход первого TpKiiepa соединен с вторым входом установки в единицу второго триггера и первым входом установки в едини-цу третьего триггера, вход установки в нуль которого подключен к прямому выходу второго триггера, второй вход установки в нуль первого триггера соединен с прямым выходом третьего триггера, вход установки в единицу первого триггера подключен к инверсному выходу второго триггера, второй вход установки в единицу третьего триггера, соединен с шиной импульсов начальной установки, а вход установки в нуль второго триггера подключен к шине контролируемых импульсов .

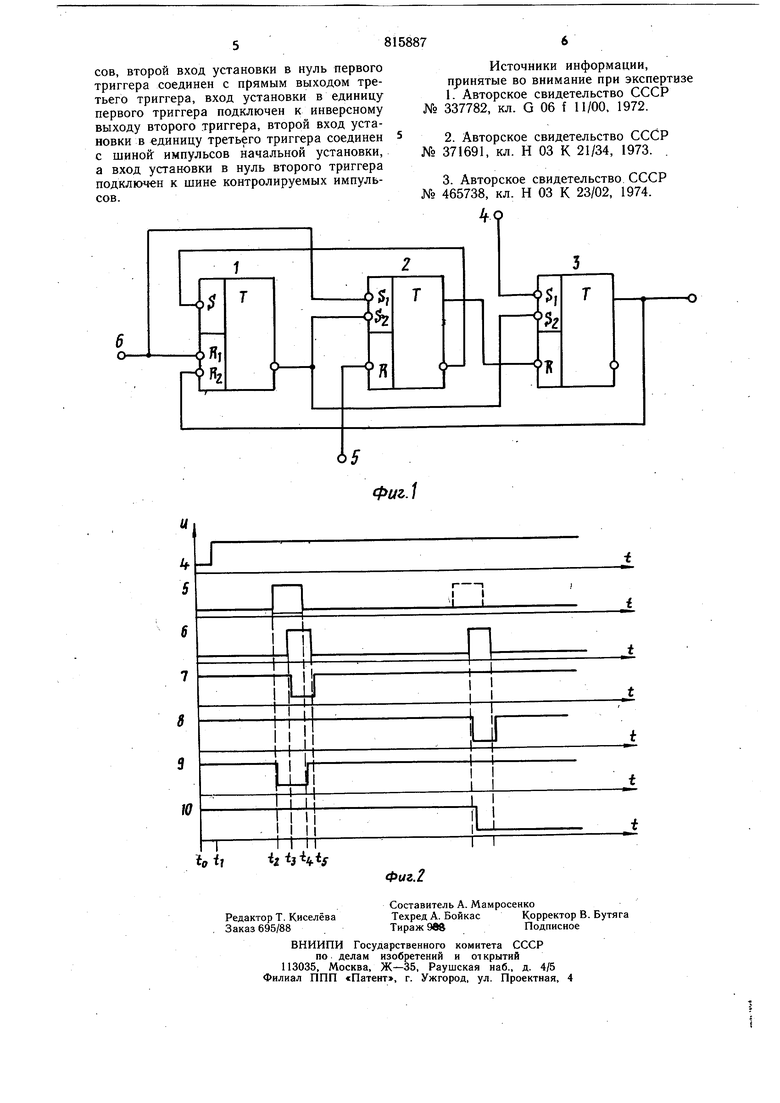

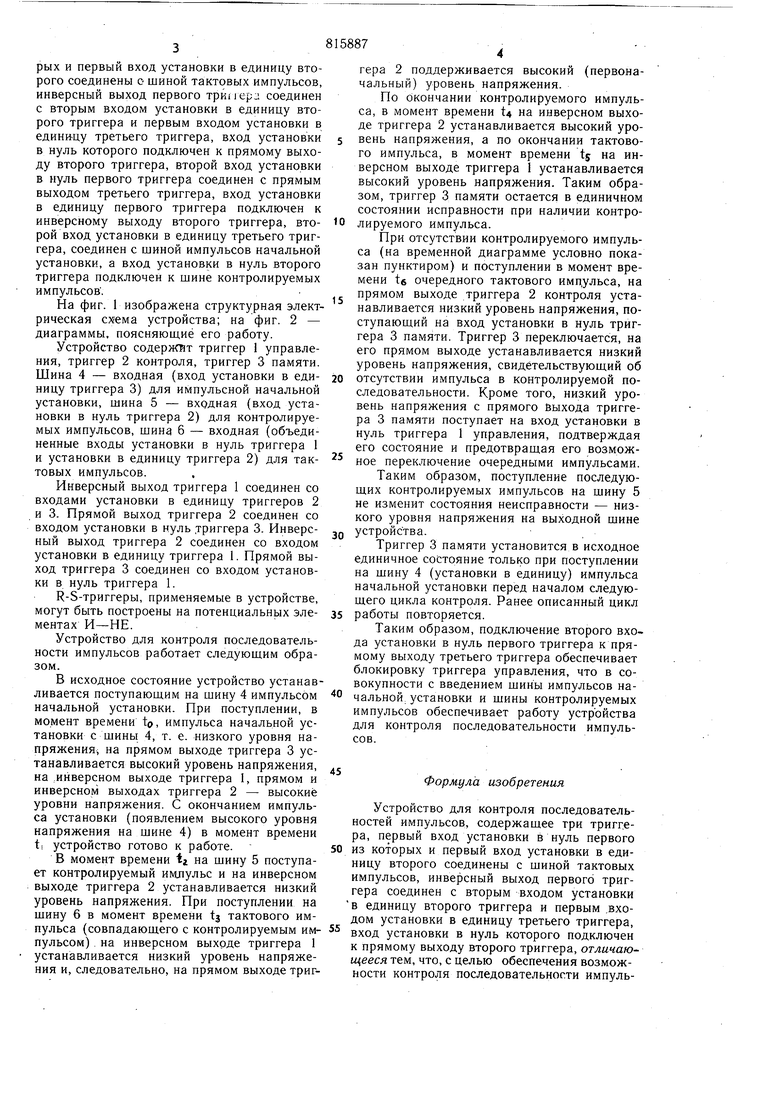

На фиг. 1 изображена структурная электрическая схема устройства; на фиг. 2 - диаграммы, поясняюш,иё его работу.

Устройство содержит триггер 1 управления, триггер 2 контроля, триггер 3 памяти. Шина 4 - входная (вход установки в единицу триггера 3) для импульсной начальной установки, шина 5 - вхрдная (вход установки в нуль триггера 2) для контролируемых импульсов, шина 6 - входная (объединенные входы установки в нуль триггера 1 и установки в единицу триггера 2) для тактовых импульсов.

Инверсный выход триггера 1 соединен со входами установки в единицу триггеров 2 и 3. Прямой выход триггера 2 соединен со входом установки в нуль .триггера 3. Инверсный выход триггера 2 соединен со входом установки в единицу триггера 1. Прямой выход триггера 3 соединен со входом установки в нуль триггера 1.

R-S-триггеры, применяемые в устройстве, могут быть построены на потенциальнь1х элементах И-НЕ.

Устройство для контроля последовательности импульсов работает следуюшим образом.

В исходное состояние устройство устанавливается поступаюшим на шину 4 импульсом начальной установки. При поступлении, в момент времени to, импульса начальной установки с шины 4, т. е. низкого уровня напряжения, на прямом выходе триггера 3 устанавливается высокий уровень напряжения, на инверсном выходе триггера 1, прямом и инверсном выходах триггера 2 - высокие уровни напряжения. С окончанием импульса установки (появлением высокого уровня напряжения на шине 4) в момент времени t. устройство готово к работе.

В момент времени t на шину 5 поступает контролируемый импульс и на инверсном выходе триггера 2 устанавливается низкий уровень напряжения. При поступлении на шину 6 в момент времени tj тактового импульса (совпадаюшего с контролируемым импульсом) на инверсном выходе триггера 1 устанавливается низкий уровень напряжения и, следовательно, на прямом выходе триггера 2 поддерживается высокий (первоначальный) уровень напряжения.

По окончании контролируемого импульса, в момент времени t4 на инверсном выходе триггера 2 устанавливается высокий уровень напряжения, а по окончании тактового импульса, в момент времени tg на инверсном выходе триггера 1 устанавливается высокий уровень напряжения. Таким образом, триггер 3 памяти остается в единичном состоянии исправности при наличии контролируемого импульса.

При отсутствии контролируемого импульса (на временной диаграмме условно показан пунктиром) и поступлении в момент времени te очередного тактового имцульса, на прямом выходе триггера 2 контроля устанавливается низкий уровень напряжения, поступающий на вход установки в нуль триггера 3 памяти. Триггер 3 переключается, на его прямом выходе устанавливается низкий уровень напряжения, свидетельствующий об отсутствии импульса в контролируемой последовательности. Кроме того, низкий уровень напряжения с прямого Выхода триггера 3 памяти поступает на вход установки в нуль триггера 1 управления, подтверждая его состояние и предотвращая его возможное переключение очередными импульсами.

Таким образом, поступление последующих контролируемых импульсов на шину 5 не изменит состояния неисправности - низкого уровня напряжения на выходной шине устройства.

Триггер 3 памяти установится в исходное единичное состояние только при поступлении на шину 4 (установки в единицу) импульса начальной установки перед началом следующего цикла контроля. Ранее описанный цикл работы повторяется.

Таким образом, подключение второго входа установки в нуль первого триггера к прямому выходу третьего триггера обеспечивает блокировку триггера управления, что в совокупности с введением шины импульсов начальной установки и шины контролируемых импульсов обеспечивает работу устройства для контроля последовательности импульсов.

Формула изобретения

Устройство для контроля последовательностей импульсов, содержащее три триггера, первый вход установки в нуль первого из которых и первый вход установки в единицу второго соединены с шиной тактовых импульсов, инверсный выход первого триггера соединен с вторым входом установки в единицу второго триггера и первым .входом установки в единицу третьего триггера, вход установки в нуль которого подключен к прямому выходу второго триггера, отличающееся тем, что, с целью обеспечения возможности контроля последовательности импульсов, второй вход установки в нуль первого триггера соединен с прямым выходом третьего триггера, вход установки в единицу первого триггера подключен к инверсному выходу второго триггера, второй вход установки в единицу третьего триггера соединен с шиной; импульсов начальной установки, а вход установки в нуль второго триггера подключен к шине контролируемых импульсов.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 337782, кл. G 06 f 11/00. 1972.

2.Авторское свидетельство СССР 371691, кл. Н 03 К 21/34, 1973.

3.Авторское свидетельство СССР 465738, кл. Н 03 К 23/02, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Расширитель импульсов | 1981 |

|

SU1014133A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Дешифратор время-импульсного кода | 1980 |

|

SU900434A1 |

| Устройство для формирования импульсных последовательностей | 1986 |

|

SU1339876A1 |

| Анализатор периодической последовательности сигналов | 1979 |

|

SU855984A1 |

| Устройство для контроля параметров объекта | 1983 |

|

SU1164670A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Устройство для допускового контроля длительности последовательности временных интервалов | 1988 |

|

SU1647508A1 |

| Устройство для обнаружения потери импульса | 1989 |

|

SU1709509A1 |

| Устройство для контроля последовательности прохождения сигналов | 1990 |

|

SU1734095A1 |

Фиг.1

Авторы

Даты

1981-03-23—Публикация

1978-07-04—Подача