Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах управления для контроля команд и сигналов.

Цель изобретения - расширение функциональных возможностей устройства в процессе контроля циклических последовательностей потенциальных сигналов за счет контроля временных интервалов между ними.

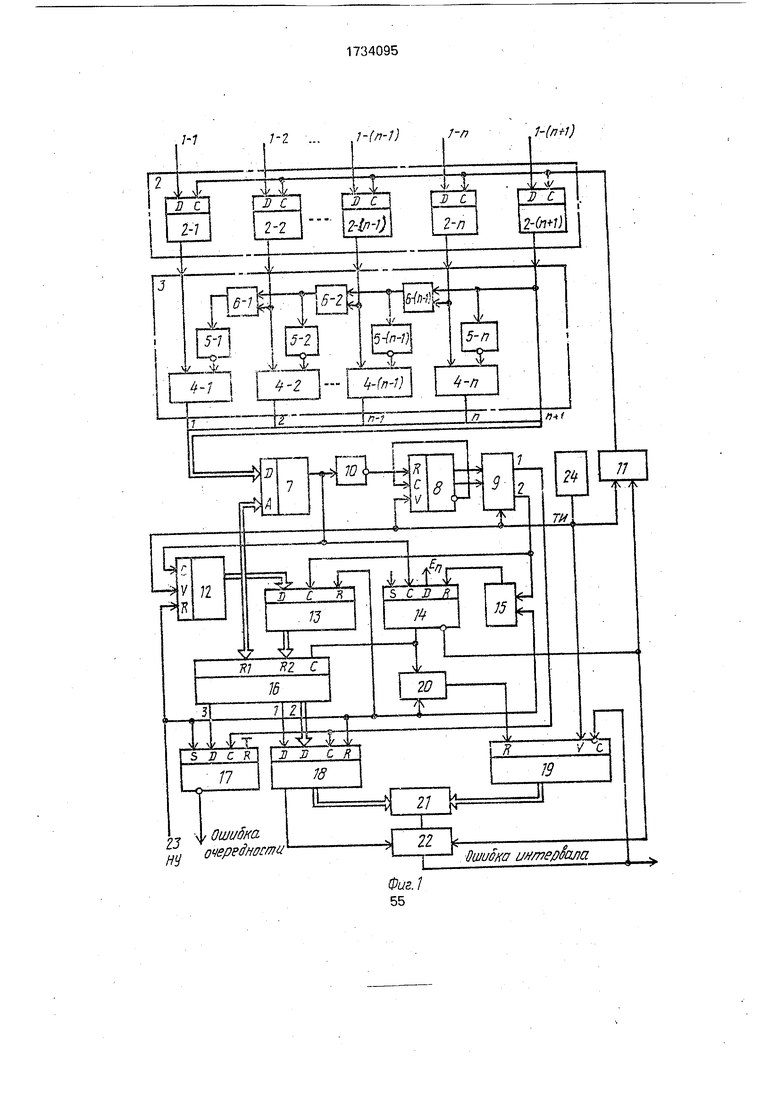

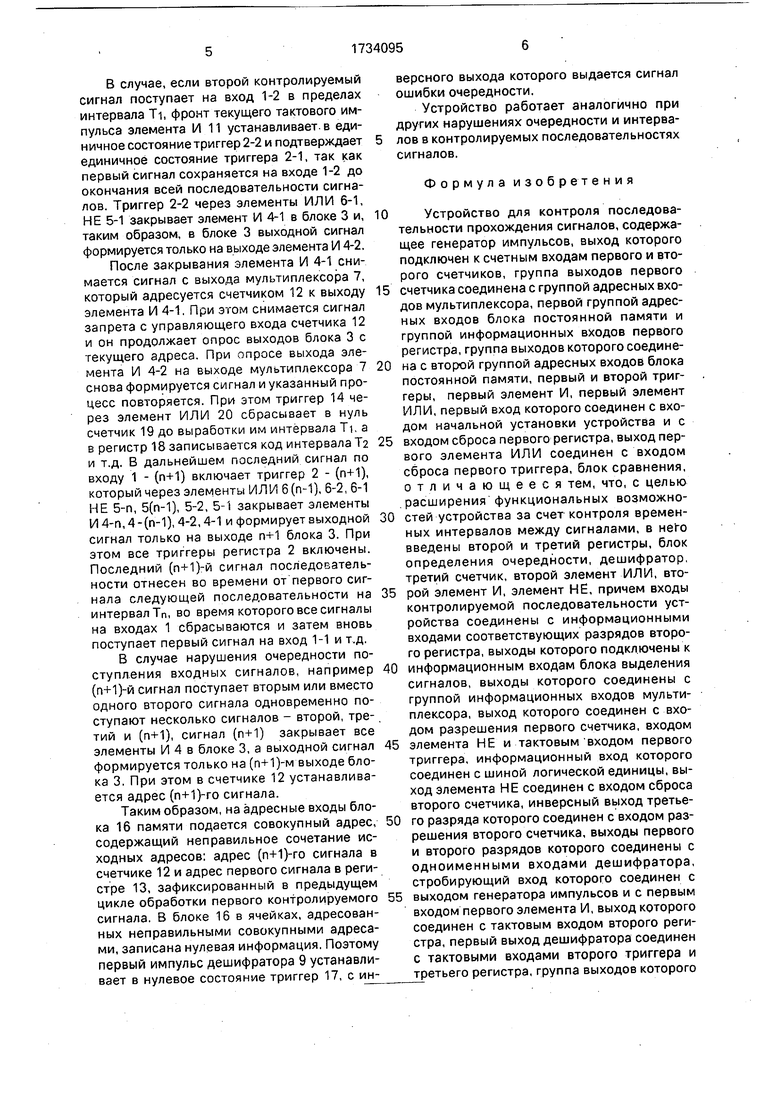

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - временная диаграмма работы устройства для двух входных сигналов.

Устройство содержит входы 1 контролируемых сигналов последовательности, регистр 2 сО-триггерами, блок 3 определения очередности сигналов, включающий элементы И 4, НЕ 5, ИЛИ 6, мультиплексор 7, с.четчик 8, дешифратор 9, элемент НЕ 10, элемент И 11, счетчик 12, регистр 13, триггер 14, элемент ИЛИ 15, блок 16 постоянной памяти, триггер 17, регистр 18, счетчик 19, элемент ИЛИ 20, блок 21 сравнения, элемент И 22, вход 23 начальной установки, генератор 24 импульсов.

Устройство работает следующим образом.

В исходном положении сигнал начальной установки, подаваемый по входу 23, устанавливает в нулевое состояние счетчик 12, регистры 13 и 18, через элемент ИЛИ 15

4 GO

4

8

СЛ

- триггер 14, через элемент ИЛИ 20 - счет- ч /;к 13 /, в единичное состояние триггер 17, который сбрасывает сигнал ошибки со сво- sro инверсного выхода. Триггер 14 сигна- /-,Oiv, со своего инверсного выхода открывает -элемент 1/1 11. Тактовые импульсы генератора 1й, поступают на тактовые входы счетчи- ,оа 12 и 19 и через элемент И 11 - на тактовые входы триггеров регистра 2.

Счегчики 12 и 19 включаются в режим непрерывного счета по срезу тактовых импульсов. Счетчик 12 через мультиплексор 7 циклически и последовательно опрашивает выходы блока 3. При отсутствии входных сигналов на входах 1 триггеры 2 фронтом текущего тактового импульса устанавливаются в нулевое состояние. Поэтому на вхо- о,ах и выходах блока 3, а также на выходе мультиплексора 7 устанавливаются нуле- зые сигналы. Нулевой сигнал мультиплексо- ра 7 через элемент НЕ 10 удерживает счетчик 8 з нулевом положении.

Контролируемые потенциальные сигналы циклически поступают на входы 1 следующим образом: сигнал, поступающий первым, подается на вход 1-1; сигнал, поступающий вторым,- на вход 1-2, и т,д., сигнал, поступающий (п+1)-м, на вход 1 - (п+1). При этом предельное значение временного интервала между первым и вторым сигналами равно TI, между вторым и третьим сигналами - Т2 и т.д., между (п-1)-м и n-м сигналами Тп-1. При поступлении первого сигнала последовательности по входу 1-1 триггер 2-1 регистра 2 фронтом текущего тактового им- пульса с выхода элемента И 11 устанавливаемся в единичное состояние. Первый сигнал на входе 1-1 удерживается до конца последовательности сигналов. Триггер 2-1 открывает элемент И 4-1 в блоке 3, в котором подготовлены к открыванию все элементы И 4-1, 4-2..., но на который не поступают сигналы с триггеров 2-2, 2-32 - (п+1).

При опросе выхода элемента И 4-1 на выходе мультиплексора 7 формируется еди- ннчный сигнал, который блокирует работу счетчика 12 и через элемент НЕ 10 включает счетчик 8.

Кроме того, фронтом сигнала мультиплексора 7 триггер 14 устанавливается в единичное состояние, так как на его D-вход постоянно подан сигнал 1. На выходах счетчика 12 формируется адрес (номер) первого контролируемого сигнала. Этот адрес подается на первые адресные входы блока 16 памяти и информационные входы регистра 13. На вторые адресные входы блока 16 поступает нулевой адрес с выходов регистра 13, Последний предназначен для хранения адреса предыдущего контролируемого сигнала последовательности.

Таким образом, совокупный адрес, подаваемый на блок 16 памяти, при правильной последовательности контролируемых сигналов содержит адреса предыдущего и последующего сигналов. По каждому из правильных совокупных адресов в блоке

16памяти предварительно записана следующая информация: признак правильной очередности и признак интервала в виде сигналов уровня 1 (выходы 3 и 1 блока 16 соответствен но) и код временного интерзала (Т-|, Т2...ТП, выходы 2 блока 16).

Триггер 14 управляет выборкой указанных сигналов из блока 16 памяти и закрывает элементы И 11 и 22. Тактовые импульсы перестают поступать на тактовый вход регистра 2. Кроме того, триггер 14 через элемент ИЛИ 20 удерживает в нулевом состоянии счетчик 19 интервала. Счетчик 8 после включения считает до фронта четвертого тактового импульса. При этом формируется сигнал на его третьем выходе, который блокирует дальнейший счет в счетчике 8. Два состояния счетчика 8 (01,10) декодируются дешифратором 9, элементы И 9-1, 9-2, которого стробируются инверсными тактовыми импульсами с выхода элемента НЕ 5.

Импульс с первого выхода дешифратора 9 поступает на тактовые входы триггера

17и регистра 18. Признак правильной очередности с выхода 3 блока 16 подтверждает единичное состояние триггера 17 и сигнал ошибки не формируется. Признак интервала и код интервала (для первого сигнала -Ti) с выходов 1 и 2 блока 16 записывается в регистр 18. Причем код интервала с группы выходов регистра 18 подается на первые входы блока 21 сравнения, а признак интервала с выхода соответствующего разряда регистра 18 подготавливает к открыванию элемент И 22. Второй импульс дешифратора 9 фиксирует в регистре 13 адрес текущего первого контролируемого сигнала с выхо- довсчетчика 12,через элемент ИЛИ 15сбра- сываетв нуль триггер 14, который открывает элементы И 11 и 22 и через элемент ИЛИ 20 снимает сигнал с входа сброса счетчика 19.

Счетчик 19 включается в режим счетчика интервала TL В случае, если за время Ti второй контролируемый сигнал не поступает на вход 1-2 устройства, счетчик 19 заполняется тактовыми импульсами до состояния, идентичного коду в регистре 18, и блок 21 сравнения формирует сигнал ошибки интервала, который через элемент И 22 блокирует счетчик 19 и выдается во внешнее устройство.

В случае, если второй контролируемый сигнал поступает на вход 1-2 в пределах интервала Т-|, фронт текущего тактового импульса элемента 1/111 устанавливает в единичное состояние триггер 2-2 и подтверждает единичное состояние триггера 2-1, так как первый сигнал сохраняется на входе 1-2 до окончания всей последовательности сигналов. Триггер 2-2 через элементы ИЛИ 6-1, НЕ 5-1 закрывает элемент И 4-1 в блоке 3 и, таким образом, в блоке 3 выходной сигнал формируется только на выходе элемента И 4-2,

После закрывания элемента И 4-1 снимается сигнал с выхода мультиплексора 7, который адресуется счетчиком 12 к выходу элемента И 4-1. При этом снимается сигнал запрета с управляющего входа счетчика 12 и он продолжает опрос выходов блока 3 с текущего адреса. При опросе выхода элемента И 4-2 на выходе мультиплексора 7 снова формируется сигнал и указанный процесс повторяется. При этом триггер 14 через элемент ИЛИ 20 сбрасывает в нуль счетчик 19 до выработки им интервала Ть а в регистр 18 записывается код интервала Т2 и т.д. В дальнейшем последний сигнал по входу 1 - (п+1) включает триггер 2 - (п+1), который через элементы ИЛИ 6(п-1), 6-2, 6-1 НЕ 5-п, 5(п-1), 5-2, 5-1 закрывает элементы И 4-п,4-(п-1), 4-2,4-1 и формирует выходной сигнал только на выходе п+1 блока 3. При этом все триггеры регистра 2 включены. Последний (п+1)-й сигнал последовательности отнесен во времени от первого сигнала следующей последовательности на интервал Тп, во время которого все сигналы на входах 1 сбрасываются и затем вновь поступает первый сигнал на вход 1-1 и т.д.

В случае нарушения очередности поступления входных сигналов, например (п+1)-й сигнал поступает вторым или вместо одного второго сигнала одновременно поступают несколько сигналов - второй, третий и (п+1), сигнал (п+1) закрывает все элементы И 4 в блоке 3, а выходной сигнал формируется только на (п+1)-м выходе блока 3. При этом в счетчике 12 устанавливается адрес (п+1)-го сигнала.

Таким образом, на адресные входы блока 16 памяти подается совокупный адрес, содержащий неправильное сочетание исходных адресов: адрес (п+1)-го сигнала в счетчике 12 и адрес первого сигнала в регистре 13, зафиксированный в предыдущем цикле обработки первого контролируемого сигнала. В блоке 16 в ячейках, адресованных неправильными совокупными адресами, записана нулевая информация. Поэтому первый импульс дешифратора 9 устанавливает в нулевое состояние триггер 17, с инверсного выхода которого выдается сигнал ошибки очередности.

Устройство работает аналогично при других нарушениях очередности и интерва- лов в контролируемых последовательностях сигналов.

Формула изобретения

Устройство для контроля последовательности прохождения сигналов, содержащее генератор импульсов, выход которого подключен к счетным входам первого и второго счетчиков, группа выходов первого

счетчика соединена с группой адресных входов мультиплексора, первой группой адресных входов блока постоянной памяти и группой информационных входов первого регистра, группа выходов которогосоединена с второй группой адресных входов блока постоянной памяти, первый и второй триггеры, первый элемент И, первый элемент ИЛИ, первый вход которого соединен с входом начальной установки устройства и с

входом сброса первого регистра, выход первого элемента ИЛИ соединен с входом сброса первого триггера, блок сравнения, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет контроля временных интервалов между сигналами, в него введены второй и третий регистры, блок определения очередности, дешифратор, третий счетчик, второй элемент ИЛИ, второй элемент И, элемент НЕ, причем входы контролируемой последовательности устройства соединены с информационными входами соответствующих разрядов второго регистра, выходы которого подключены к

информационным входам блока выделения сигналов, выходы которого соединены с группой информационных входов мультиплексора, выход которого соединен с входом разрешения первого счетчика, входом

элемента НЕ и тактовым входом первого триггера, информационный вход которого соединен с шиной логической единицы, выход элемента НЕ соединен с входом сброса второго счетчика, инверсный выход третьего разряда которого соединен с входом разрешения второго счетчика, выходы первого и второго разрядов которого соединены с одноименными входами дешифратора, стробирующий вход которого соединен с

выходом генератора импульсов и с первым входом первого элемента И, выход которого соединен с тактовым входом второго регистра, первый выход дешифратора соединен с тактовыми входами второго триггера и третьего регистра, группа выходов которого

соединена с первой группой входов блока сравнения, вторая группа входов которого соединена с группой выходов третьего счетчика, счетный вход которого подключен к выходу генератора импульсов, а вход разрешения - к выходу ошибки интервала устройства и выходу второго элемента И, первый вход которого соединен с выходом третьего регистра, второй вход второго элемента И соединен с выходом блока сравнения, третий вход второго элемента И соединен с вторым входом первого элемента И и с инверсным выходом первого триггера, прямой выход которого соединен с первым входом второго элемента ИЛИ и с входом выборки блока постоянной памяти, выход признака интервала и группа выходов интервала которого соединены с соответствующими информационными входами третьего регистра, выход признака правильной очередности блока постоянной памяти соединен с информационным входом второго триггера, инверсный выход которого является выходом ошибки очередности устройства, единичный вход второго триггера соединен с входами сброса третьего регистра, первого счетчика, входом начальной установки устройства и с вторым входом второго элемента ИЛИ, выход которого соединен с входом сброса третьего счетчика, второй выход дешифратора соединен с тактовым входом первого регистра и вторым входом первого элемента ИЛИ, причем блок определения очередности сигналов содержит группу из п элементов И, группу из (п-1) элементов ИЛИ, группу из п элементов

НЕ, где (п+1)-число входов блока определения очередности сигналов, с первого по п-й входы блока определения очередности сигналов соединены с первыми входами соответствующих элементов И группы, причем

входы блока определения очередности сигналов, с второго по n-й, соединены с первыми входами соответствующих элементов ИЛИ группы, выход первого элемента ИЛИ группы соединен через первый элемент

НЕ группы с вторым входом первого элемента И группы, выход каждого последующего элемента ИЛИ группы, с второго по (п-1)-й, соединен с вторым входом предыдущего элемента ИЛИ группы и через

соответствующий элемент НЕ группы - с вторыми входами второго и последующих элементов И группы до (п-1)-го элемента соответственно, (п+1)-й вход блока определения очередности сигналов соединен с

одноименным выходом блока определения очередности сигналов, с вторым входом (п-1)-го элемента ИЛИ группы и через n-й элемент НЕ группы - с вторым входом n-го элемента И группы, выходы элементов

И группы являются выходами блока определения очередности сигналов.

и s

х

i

«NJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1700557A1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Устройство для программного управления | 1989 |

|

SU1698875A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Устройство для программного управления | 1990 |

|

SU1784939A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Модульное устройство программного управления и контроля | 1990 |

|

SU1803905A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах управления для контроля команд и сигналов. Цель изобретения - расширение функциональных возможностей за счет контроля интервалов между сигналами. Устройство содержит регистр, блок определения очередности выделения сигналов с элементами, мультиплексор, счетчик, дешифратор, элементы НЕ, И, счетчик, регистр, триггер, элемент ИЛИ, блок постоянной памяти, триггер, регистр, счетчик, элемент ИЛИ, блок сравнения, элемент И, генератор импульсов. В предложенном устройстве за счет введения двух регистров, блока выделения сигналов, дешифратора, счетчика, элементов И, ИЛИ, НЕ обеспечивается наряду с контролем очередности контроль интервалов поступления сигналов, что расширяет функциональные возможности устройства, повышает качество, глубину и достоверность контроля функционирования систем с циклическими последовательностями команд и сигналов. 2 ил. ел С

| Устройство для контроля последовательности прохождения сигналов | 1988 |

|

SU1543407A1 |

| Устройство для контроля срабатывания клавиш наборного поля | 1985 |

|

SU1297050A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-05-15—Публикация

1990-08-22—Подача