(54) УСТРОЙСТВО КОНТРОЛЯ КОДА СЧЕТЧИКА

| название | год | авторы | номер документа |

|---|---|---|---|

| Система полунатурного моделирования динамических систем | 1982 |

|

SU1121681A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1985 |

|

SU1298762A2 |

| Устройство поиска неисправных блоков и элементов | 1989 |

|

SU1709351A1 |

| Счетное устройство, сохраняющее информацию при отключении питания | 1987 |

|

SU1492476A1 |

| Устройство для выделения импульсов синхронизации | 1978 |

|

SU785977A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля блоков оперативной памяти | 1981 |

|

SU957278A1 |

| Программируемый генератор импульсов | 1985 |

|

SU1361708A1 |

Изобретение относится к импульсной технике и может быть использовано, например в приборах для диагностики запоминающих устройств (ЗУ). ,

Известно устройство, содержащее счетчик, два элемента совпадения для определения границ работы счетчика, два триггера, элемент совпадения на три входа, элемент задержки, элемент ИЛИ, формирователь сигнала переполнения. Устройство регистрирует на счетчике код остатка от деления на число, равное коду правой границы зоны работы счетчика 1.

Недостаток устройства состоит в том, что при работе в режиме генератора адресных кодов для испытуемого ЗУ, оно не регистрирует точный адрес сбоя ЗУ из-за задержки сигнала контроля в блоке свертки по модулю два.

Известно устройство контроля, содержащее клавишный переключатель частоты, блок управления, щину сброса, счетчик адреса, испытуемое постоянное ЗУ, приемный регистр, блок свертки по модулю два, триггер, блок индикации и два клавишных регистра, первые входы блока индикации соединены со входами блока свертки по

модулю два, и с выходами приемного регистра, входы которого соединены с выходами испытуемого постоянного ЗУ, адресные входы которого соединены с выходами счетчика адреса, тактовый вход которого соединен с первым выходом блока управления, первый вход которого соединен с выходом клавишного переключателя частоты, выход блока свертки по модулю два соединен со входом первого триггера, выход которого соединен со вторым входом блока управления, третий вход которого соединен с шиной сброса, второй, третий и четвертый выходы блока управления соединены соответственно с тактовым входом приемного регистра, с управляющим входом блока свертки по модулю два и с тактовым входом триггера.

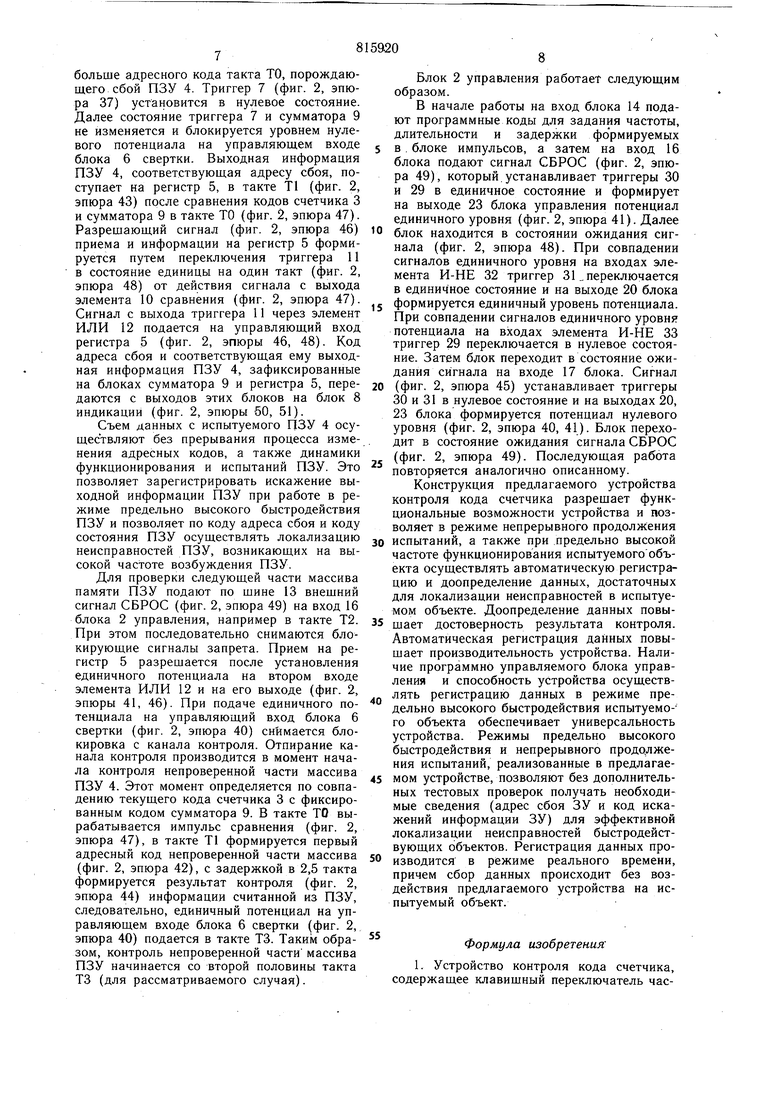

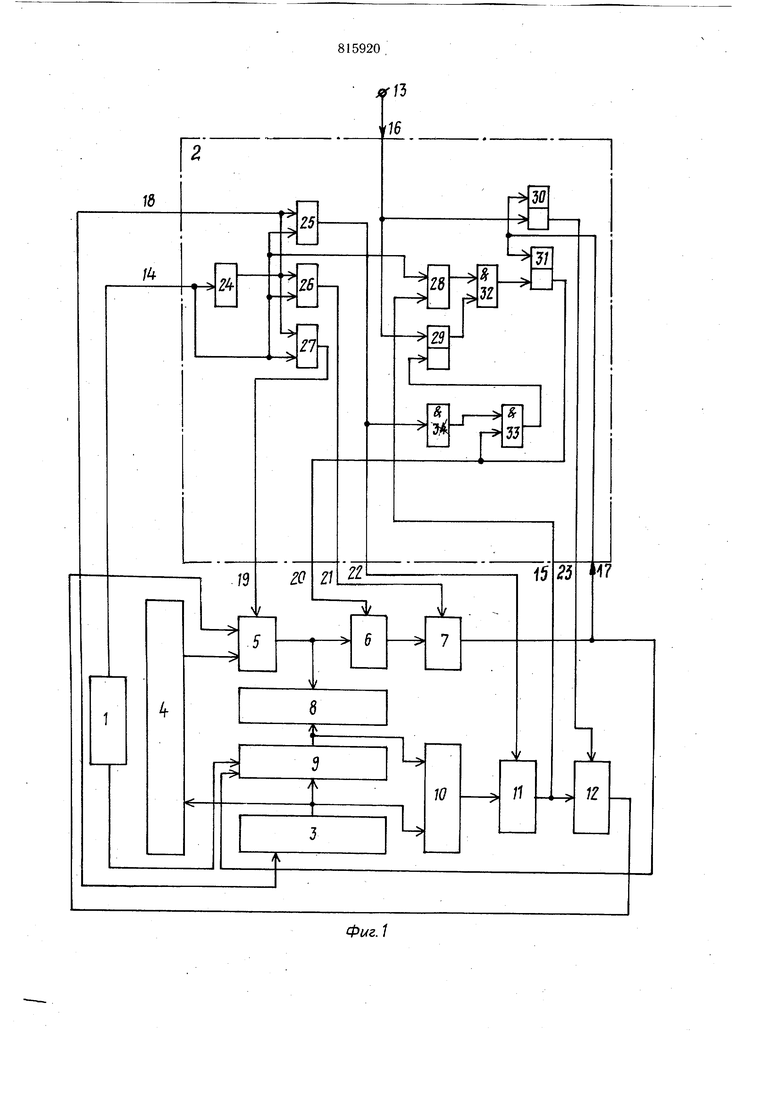

5 Известное устройство имитирует рабочие условия для испытуемого постоянного запоминаюихего устройства (ПЗУ) и контролирует его выходную .информацию, при ошибках в информации работа счетчика прерывается. Проверка ПЗУ производится на дискретных частотах, в том числе на предельных рабочих частотах. При проверке быстродействующих ПЗУ на высокой частоте происходит наложение циклов канала конт роля и канала генерации адресов, при этом остановка счетчика выполняется с запаздыванием на I-2 такта из-за задержки в канале контроля (на приемном регистре, в блоке свертки и на триггере). Точный адрес сбоя ЗУ восстанавливают вручную с помощью клавишного регистра. По коду восстановленного адреса считывают информацию ячейки памяти ПЗУ для анализа и поиска неисправностей 2. Недостаток известного устройства проявляется при испытаниях ПЗУ на высоких частотах функционирования и заключается в том, что для отыскания причин сбоя изменяют режим работы ПЗУ - взамен динамического изменения адресных кодов переходят к режиму выборки ячейки памяти одного фиксированного адреса, при этом сбои и ошибки динамического режима исчезают, что создает дополнительные трудности и приводит к непроизводительным потерям рабочего времени при настройке и локализации неисправностей ПЗУ. Цель изобретения. - расширение функциональных возможностей устройства контроля кода счетчика, путем автоматического формирования кода адреса сбоя испытуемого ЗУ и регистрации искаженной при сбое информации ЗУ в режимах непрерывного продолжения испытаний и перебора адресных кодов и в режиме предельно высокой частоты функционирования испытуемого ЗУ. Поставленная цель достигается тем, что в устройство контроля кода счетчика, содержащее клавишный переключатель частоты, блок управления, шину сброса, счетчик адреса, испытуемое ПЗУ, приемный регистр, блок .свертки по модулю два, первый триггер и блок индикации, первые входы которого соединены со входами блока свертки по модулю два и с выходами приемного регистра, входы которого соединены с выходами испытуемого ПЗУ, адресные входы которого соединены с выходами счетчика адреса, тактовый вход которого соединен с первым выходом .блока управления, первый вход которого соединен с первым выходом клавишного переключателя частоты, выход блока свертки по модулю два соединен со входом первого триггера, выход которого соединен с шиной сброса, второй, третий и четвертый выхо.ды блока управления соединены соответственно с тактовым входом приемного регистра, с управляюшим входом блока свертки по модулю два и с тактовым входом первого триггера, в него вве.дены сумматор, элемент сравнения, второй триггер, элемент ИЛИ, выход и первый вход которого соединены соответственно с управляющим входом приемного регистра и с выходом второго триггера, тактовый вход которого соединен с пятым выходом блока управления, шестой выход и четвертый вход которого соединены соответственно со вторым входом элемента ИЛИ и с выходом второго триггера, вход которого соединен с выходом элемента сравнения, первые входы которого соединены с выходами счетчика адреса и с первыми входами сумматора, выходы которого соединены со вторыми входами блока индикации и вторыми входами элемента сравнения, вторые выходы клавишного переключателя частоты соединены со вторыми входами сумматора, управляюиций вход которого соединен с выходом первого триггера. В устройстве контроля кода счетчика блок управления содержит программируемый генератор тактовых импульсов, три формирователя с блоками программируемых задержек, три установочных триггера, два элемента И-НЕ, элемент НЕ и программируемый .элемент задержки, первый вход блока управления соединен с первыми входами формирователей с блоками программируемых задержек, первы.м входом программиpyeMoio элемента задержки и со входом программируемого генератора тактовых импульсов, выход которого соедкнеп с первь м выходом блока управления и со вторыми входами формирователей с блоками программируемых задержек, выходы которых соответственно соединены со вторым, четвертым и пятым выходами блока управления второй вход которого соединен с первыми входами первого и- второго установочных триггеров, второй вход первого из которых соединен с первым входом третьего установечного триггера и с третьим входом блока управления, шестой выход которого соединен с выходо.м первого установочного триггера, четвертый вход .блока управления соединен со вторым входом программируемого элемента задержки, выход, .которого соединен с первым входом первого элемента И-НЕ, второй вход которого соединен с выходом третьего установочного триггера, выход первого элемента И-НЕ - соединен со вторым входом второго установочного триггера, выход которого соединен с третьим выходом блока управления и с первым входом второго элемента И-НЕ, выход которого соединен со .вторым входом третьего установочного триггера, пятый выход блока управления соединен через элемент НЕ со вторым входом второго элемента И-НЕ. На фиг. 1 приведена блок-схема устройства контроля счетчика; на фиг. 2 - эпюры напряжений, поясняющие принцип работы устройства. Устройство содержит клавишный переключатель 1 частоты, блок 2 управления, счетчик 3 адреса, испытуемое ПЗУ 4, приемный регистр 5, блок 6 свертки по модулю два, триггер 7, блок 8 индикации, сумматбр 9 элемент 10 сравнения, триггер 11, элемент ИЛИ 12, шина 13 сброса, входы 14, 15, 16 и 17 блока управления, выходы 18 - 23 блока 2 управления. Блок 2 управления содержит программируемый генератор 24 тактовых импульсов, формирователи 25 - 27 с блоками программируемых задержек, программируемый элемент 28 задержки, установочные триггеры 29 - 31, элементы И-НЕ 32, 33 и элемент НЕ 34. На фиг. 1 первые входы блока 8 индикации соединены со входами блока 6 свертки по модулю два и с выходами приемного регистра 5, входы которого соединены с выходами испытуемого ЗУ 4, адресные входы которого соединены с выходами счетчика адреса 3, с первыми входами элемента 10 сравнения и с первыми входами сумматора 9, вторые входы которого соединены со вторыми выходами клавишного переключателя 1 частоты, первый выход которого соединен со входом 14 блока 2 управления, вход 17 которого соединен с выходом триггера 7 и с управляюш,им входом сумматора 9, выходы которого соединены со вторыми входами блока 8 индикации и вторыми входами элемента 10 сравнения, выход которого соединен со входом триггера 11, выход которого соединен со входом 15 блока 2 управления и с первым входом элемента ИЛИ 12, второй вход и выход которого соединены соответственно с выходом 23 блока 2 управления и с управляющим входом приемного регистра 5, выход блока 6 свертки по модулю два соединен со входом триггера 7, шина 13 сброса соединена со входом блока 2 управления, выходы 19, 21, 22 и 20 которого соединены соответственно с тактовыми входами приемного регистра 5, триггеров 7, 11 и с управляющим входом блока 6 свертки по модулю два. В блоке 2 управления вход 14 соединен с первыми входами формирователей 25 - 27 с блоками программируемых задержек и с первым входом программируемого элемента 28 задержки и со входом программируемого генератора 24 тактовых импульсов, выход которого соединен с выходом 18 блока 2 управления и со вторыми входами формирователей 25 - 27 с блоками программируемых задержек, выходы которых соединены соответственно с выходами 22, 21 и 19 блока 2 управления, вход 17 которого соединен с первыми входами установочных триггеров 30 и 31, второй вход установочного триггера 30 соединен с первым входом установочного триггера 29 и со входом 16 блока 2 управления, выход 23 которого соединен с выходом установочного триггера 30, вход 15 блока 2 управления соединен со вторым входом программирующего элемента 28 задержки, выход которого соединен с первым входом элемента И-НЕ 32, второй вход которого соединен с выходом установочного триггера 31, выход которого соединен с первым входом элемента И-НЁ, 33, и с выходом 20 блока 2 управления, выход 22 которого соединен через элемент НЕ 34. со вторым входом элемента И-НЕ 33, выход которого соединен со вторым входом установочного триггера 29. На фиг. 2 представлены эпюры напряжений: 35 - 37 - соответственно выходом 18, 19, 21 блока 2 управления; 38 - входа 14 блока 2 управления; 39 - 41 - соответственно выходам 22, 20, 23 блока 2 управления; 42 - выходом счетчика адреса 3; 43 - выходом ПЗУ 4; 44, 45 - соответственно входа и выхода триггера 7; 46 - выходов сумматора 8; 47 - выхода элемента 10 сравнения; 48- входа 15 блока 2 управления; 49 - входа 16 блока 2 управления; 50 - выхода элемента ИЛИ 12 и 51 - выходов приемного регистра 5. Устройство контроля счетчика работает следующим образом. Блок 2 управления формирует тактовые импульсы (фиг. 2, эпюры 35, 36, 37 и 39) и поддерживает уровни единичного потенциала (фиг. 2 эпюры 40, 41) на выходах 20, 23 блока 2 управления. Адресные коды (фиг. 2, эпюра 42) изменяются.каждый такт и поступают на адресные входы ПЗУ 4, а соответствующая считанная из ПЗУ информация (фиг. 2, эпюра 43) поступает на входы приемного регистра 5. На временной диаграмме устройства (фиг. 2) представлен случай, когда ПЗУ функционирует на предельно высокой частоте, т.е. время считывания информации из ПЗУ примерно равно длительности периода изменения кода адреса, так что адресному коду, сформированному в такте ТО, соответствует информация ПЗУ такта Т1 (фиг. 2, эпюры 42, 43).1Если ошибка ПЗУ содержится в информации, поступающей на вход регистра в такте Т1, а задержка результата контроля на блоках 5, 6 и 7 равна 1,5 такта) После выдачи адреса в такте ТО и приема информации в такте Т1 в такте Т2 формируется импульс нулевого потенциала на выходе блока 6 свертки (фиг. 2, эпюра 44), который передается на вход триггера 7 и переключает его в состояние единицы (фиг. 2 эпюра 45). Под влиянием изменения уровня потенциала на выходе триггера 7 блок 2 управления формирует сигналы запрета, уровня нулевого потенциала, для управляющих входов блока 6 свертки и регистра 5 (фиг. 2, эпюры 40, 41 и 46). Импульс с выхода триггера 7 (фиг. 2, эпюра 45) подается на управляющий вход сумматора 9 и разрешает выполнение операции вычитания кода переключателя 1 из кода счетчика 3. В результате операции вычитания на сумматоре 9 формируется (фиг. 2, эпюра 50) искомый точный адрес бря ПЗУ 4. Для реализации этого требования необходимо задать код переключателя 1 частоты равным двойке, так как текущий код счетчика 3 в такте Т2 на две единицы

больше адресного кода такта ТО, порождающего сбой ПЗУ 4. Триггер 7 (фиг. 2, эпюра 37) установится в нулевое состояние. Далее состояние триггера 7 и сумматора 9 не изменяется и блокируется уровнем нулевого потенциала на управляющем входе блока 6 свертки. Выходная информация ПЗУ 4, соответствующая адресу сбоя, поступает на регистр 5, в такте Т1 (фиг. 2, эпюра 43) после сравнения кодов счетчика 3 и сумматора 9 в такте ТО (фиг. 2, эпюра 47). Разрешающий сигнал (фиг. 2, эпюра 46) приема и информации на регистр 5 формируется путем переключения триггера 11 в состояние единицы на один такт (фиг. 2, эпюра 48) от действия сигнала с выхода элемента 10 сравнения (фиг. 2, эпюра 47). Сигнал с выхода триггера 11 через элемент ИЛИ 12 подается на управляющий вход регистра 5 (фиг. 2, эпюры 46, 48). Код адреса сбоя и соответствующая ему выходная информация ПЗУ 4, зафиксированные на блоках сумматора 9 и регистра 5, передаются с выходов этих блоков на блок 8 индикации (фиг. 2, эпюры 50, 51).

Съем данных с испытуемого ПЗУ 4 осуществляют без прерывания процесса изменения адресных кодов, а также динамики функционирования и испытаний ПЗУ. Это позволяет зарегистрировать искажение выходной информации ПЗУ при работе в режиме предельно высокого быстродействия ПЗУ и позволяет по коду адреса сбоя и коду состояния ПЗУ осуществлять локализацию неисправностей ПЗУ, возникающих на высокой частоте возбуждения ПЗУ.

Для проверки следующей части массива памяти ПЗУ подают по шине 13 внешний сигнал СБРОС (фиг. 2, эпюра 49) на вход 16 блока 2 управления, например в такте Т2. При этом последовательно снимаются блокируюшие сигналы запрета. Прием на регистр 5 разрешается после установления единичного потенциала на втором входе элемента ИЛИ 12 и на его выходе (фиг. 2, эпюры 41, 46). При подаче единичного потенциала на управляющий вход блока 6 свертки (фиг. 2, эпюра 40) снимается блокировка с канала контроля. Отпирание канала контроля производится в момент начала контроля непроверенной части массива ПЗУ 4. Этот момент определяется по совпадению текущего кода счетчика 3 с фиксированным кодом сумматора 9. В такте ТО вырабатывается импульс сравнения (фиг. 2, эпюра 47), в такте Т1 формируется первый адресный код непроверенной части массива (фиг. 2, эпюра 42), с задержкой в 2,5 такта формируется результат контроля (фиг. 2, эпюра 44) информации считанной из ПЗУ, следовательно, единичный потенциал на управляющем входе блока 6 свертки (фиг. 2, эпюра 40) подается в такте ТЗ. Таким образом, контроль непроверенной части массива ПЗУ начинается со второй половины такта ТЗ (для рассматриваемого случая).

Блок 2 управления работает следующим образом.

В начале работы на вход блока 14 подают программные коды для задания частоты, длительности и задержки формируемых в , блоке импульсов, а затем на вход 16 блока подают сигнал СБРОС (фиг. 2, эпюра 49), который.устанавливает триггеры 30 и 29 в единичное состояние и формирует на выходе 23 блока управления потенциал единичного уровня (фиг. 2, эпюра 41). Далее

блок находится в состоянии ожидания сигнала (фиг. 2, эпюра 48). При совпадении сигналов единичного уровня на входах элемента И-НЕ 32 триггер 31 ..переключается в единичное состояние и на выходе 20 блока

5 формируется единичный уровень потенциала. При совпадении сигналов единичного уровня потенциала на входах элемента И-НЕ 33 триггер 29 переключается в нулевое состояние. Затем блок переходит в состояние ожидания сигнала на входе 17 блока. Сигнал

0 (фиг. 2, эпюра 45) устанавливает триггеры ЗО и 31 в нулевое состояние и на выходах 20, 23 блока формируется потенциал нулевого уровня (фиг. 2, эпюра 40, 41). Блок переходит в состояние ожидания сигнала СБРОС (фиг. 2, эпюра 49). Последующая работа повторяется аналогично описанному.

Конструкция предлагаемого устройства контроля кода счетчика разрешает функциональные возможности устройства и позволяет в режиме непрерывного продолжения

0 испытаний, а также при предельно высокой частоте функционирования испытуемого объекта осуществлять автоматическую регистрацию и доопределение данных, достаточных для локализации неисправностей в испытуемом объекте. Доопределение данных повышает достоверность результата контроля. Автоматическая регистрация данных повышает производительность устройства. Наличие программно управляемого блока управления и способность устройства осуществQ лять регистрацию данных в режиме предельно высокого быстродействия испытуемого объекта обеспечивает универсальность устройства. Режимы предельно высокого быстродействия и непрерывного продцлжения испытаний, реализованные в предлагаемом устройстве, позволяют без дополнительных тестовых проверок получать необходимые сведения (адрес сбоя ЗУ и код искажений информации ЗУ) для эффективной локализации неисправностей быстродействующих объектов. Регистрация данных производится в режиме реального времени, причем сбор данных происходит без воздействия предлагаемого устройства на испытуемый объект.

Формула изобретения

Фиг. 1 .. лляг «ГШШ .ши TRJU ITLTL juui тш1л иг

п

rci

то

г

г

м

7 48 49

И

50

57

гз

TZ

7-4 1 Г

П г лг .глппт пг ..яллп/и 1Л тгътпишп шллял

Авторы

Даты

1981-03-23—Публикация

1979-04-23—Подача