установочными входами блока управления системой, выход первой схемы сравнения соединен с первым входом счетчика тдиклов и обнуляющим входом счетчика тактов,, выход которого подключен к первому входу узла формирования адреса, а также к второму входу первой схемы сравнения, выход счетчика циклов соединен с первым информационным входом программного узла и вторым входом второй схемы сравнения, выход которой подключен к входу счетчика порядка ядер, выход которого соединен с вторым информационным входом программного узла и вторым входом третьей схемы сравнения, выход которой подключен к входу останова генератора тактовых импульсов, первый выход программного узла подключен к информационному входу счетчика тактов, второй выход программного узла соединение вторым входом узла формирования адреса и первыми суммирующими входами первого и второго суммирующего счетчико третий выход программного узла соеди нен с третьим входом узла формирования адреса и вторым суммирующим входом второго счетчика, четвертый выход программного узла подключен к входу третьего счетчика, выход которого соединен с вычитающим входо второго счетчика, пятьй выход программного узла подключен к четверто му входу узла формирования адреса и первому входу четвертого счетчика второй вход которого соединен с шестым выходом программного узла, седь мой выход которого соединен с третьи суммирующим входом второго счетчика второй вход первого счетчика и трети вход четвертого счетчика подключены к восьмому выходу программного узла девятый выход которогр соединен с пятым входом узла формирования адреса и третьим входом первого счетчика, четвертый вход которого подключен к десятому выходу програм . много узла, одиннадцатый выход которого соединен с входом запуска генератора пробных воздействий вход останова которого подключен к выходу четвертой схемы сравнения и второму входу счетчика циклов, первый выход узла формирования адреса и выход первого счетчика блока управления системой соединены соответственно с первой группой адрес11 ных входов блока памяти, вторая группа адресных входов которого подключена соответственно к второму вькоду узла формирования адреса и выходу второго счетчика, третий выход узла формирования адреса и выход четвертого счетчика соединены с адресными входами блока оперативной памяти, группа управляющих выходов программного узла соединена соответственно с входами управления сложением, вычитанием и умножением арифметического устройства, а выход первого счетчика соединен с вторым входом четвертой схемы сравнения. 2.Система по п.1, отличающ а я с я , что узел формирования адреса содержит дешифратор, регистр, две г.руппы регистров, два злемёнта И и.зч.тыре элемента ИЛИ, причем вход дешифратора является первым входом |гзла формирования адреса, а вьйсоды подключены соответственно к входам регистров первой группы и первым- входам регистров второй группы, выходы регистров первой группы подключены к соответствующим входам первого элемента ИЛИ, выход которого соединен с первыми входами первого и второго элементов И, выходы, которых подключены соответственно к первым входам третьего и четвертого элементов ИЛИ, вторые входы которых соединены с выходом регистра, выходы регистров второй группы соединены с соответствующими входами второго элемента ИЛИ, вторым входом узла формирования адреса является вход регистра, третьим входом узла формирования адреса является второй вход второго элемента И, четвертым входом узла формирования адреса являются вторые входы регистров второй группы, а пятым входом узла формирования адреса является второй вход первого элемента И, первым и вторым выходами узла формирования адреса являются соответственно вы.ходы третьего и четвертого элементов ИЛИ, а третьим выходом - выход второго элемента ИЛИ. 3.Система по пп.1 и 2, о т л ич .а ю щ а я с я тем, что программный узел содержит первый, второй и третий счетчики, дешифратор, две группы элементов И, три элемента ИЖ, постоянное запоминающее устройство, две схемы сравнения, элемент И и триггер.причем тактовый вход первого счетчика является тактовым входом программного узла, установочньтм входом которого являет ся установочный вход первого счетчика, соединенный с первыми входами первого и второго элементов ИЛИ, первым и вторым информационными вхо дами программного узла являются соответственно первый и второй адресные входы постоянного запоминающ го устройства, первый адресный вход которого соединен также с входом третьего элемента ИЛИ, разрядные вы ходы первого счетчика соединены соответственно с входами дешифратора, первый - одиннадцатьйвыходы которого подключены соответственно к первым входам элементов И первой группы, вторые входы которых объеди нены и соединены с первым вькодом постоянного запоминающего устройств второй и третий выходы которого подключены соответственно к первым входам первой и второй схем сравнения, вторые входы которых соединены соответственно с выходами второго и третьего счетчиков, а управляющие входы первой и второй схем сравнени соединены с двенадцатым и тринадцат выходами дешифратора, одиннадцатый выход дешифратора соединен также с информационным входом второго счетчика, установочный вход которог подключен к выходу второго элемента ИЛИ, второй вход которого соединен с выходом первой Схемы сравнения, первым входом элемента И и информационным входом третьего счетчика, установочный вхоД которого подключен к выходу первого элемента ИЛИ, первому входу триггера и инверсному входу элемента И, выход которого соединен с вторым входом триггера. 81 выход которого подключен к первому инверсному входу первого элемента И второй группы и третьему адресному входу постоянного запоминающего устройства, четвертый адресный вход которого соединен с выходом второго счетчика, выход второй схемы сравнения подключен к второму входу элемента ИЛИ, выход первого элемента И первой группы соединен с первьм прямым входом первого элемента И второй группы и первыми вх одами второго и четвертого элементов И второй группы, выход второго элемента И первой группы соединен с первыми входами третьего и пятого элементов И второй группы, выход второго элемента ИЛИ подключен к второму инверсному входу первого элемента И второй группы и вторым входам второго-пятого элементов И второй группы, первым выходам программного узла является выход шестого элемента И первой группы, вторым, третьим, и четвертым выходами программного узла являются соответственно выходы третьего и четвертого элементов И первой группы и выход второго элемента И .второй группы, пятым и шестым выходами программного узла являются соответственно выходы седьмого элемента И второй группы, седьмым выходом являются объединенные вькоды четвертого и пятого элементов И второй группы, восьмым, девятым и десятым выходами программного узла являются соответственно выходы одиннадцатого, десятого и второго элементов И первой группы, одиннадцатым выходом программного узла является выход .первого элемента И второй группы, а группой управляющих выходов программного узла являются выходы пятого, восьмого и девятого элементов И первой группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обучения операторов автоматизированных систем управления | 1984 |

|

SU1196937A1 |

| Система полунатурного моделирования динамических систем | 1986 |

|

SU1427377A1 |

| Устройство для синхронизации распределенной вычислительной системы | 1988 |

|

SU1508201A1 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

| Резервированная вычислительная система | 1989 |

|

SU1691991A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Программное устройство для фиксации и документирования времени | 1989 |

|

SU1677691A1 |

| СИСТЕМА ВИЗУАЛЬНОГО МОДЕЛИРОВАНИЯ ЭКОНОМИЧЕСКИХ СИСТЕМ | 2010 |

|

RU2444051C1 |

| Устройство для моделирования алгоритма деятельности человека-оператора | 1989 |

|

SU1621042A1 |

| Устройство для моделирования цифровых объектов | 1976 |

|

SU610114A1 |

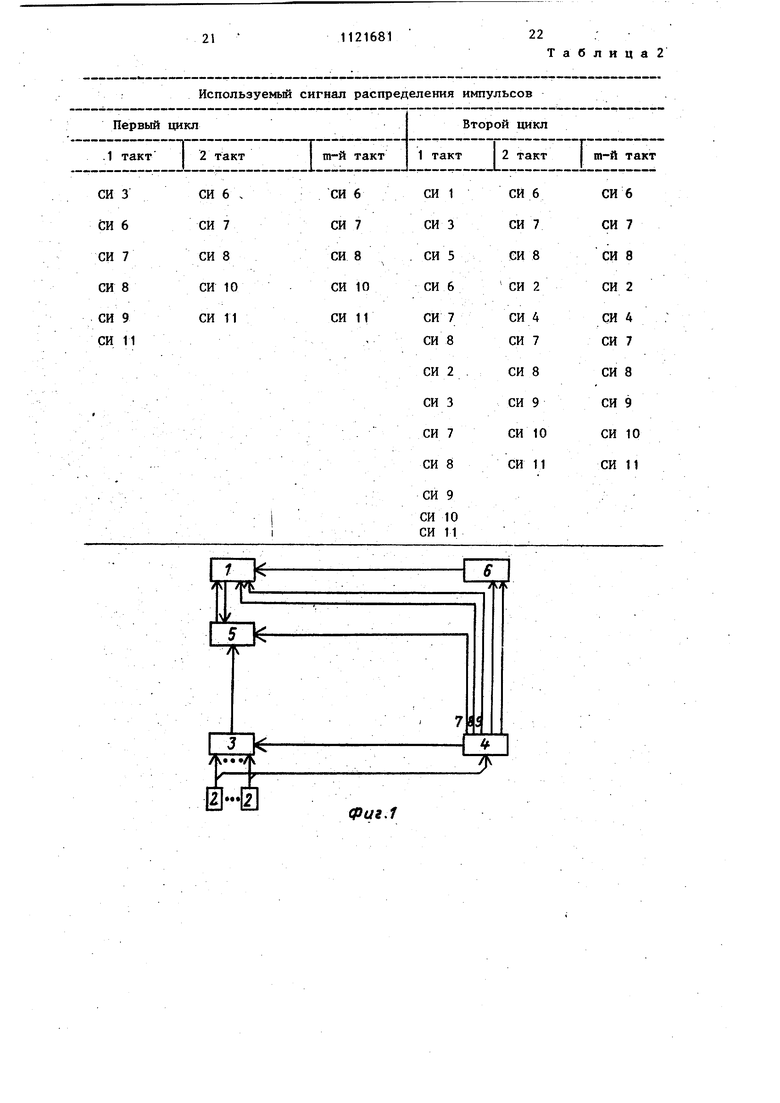

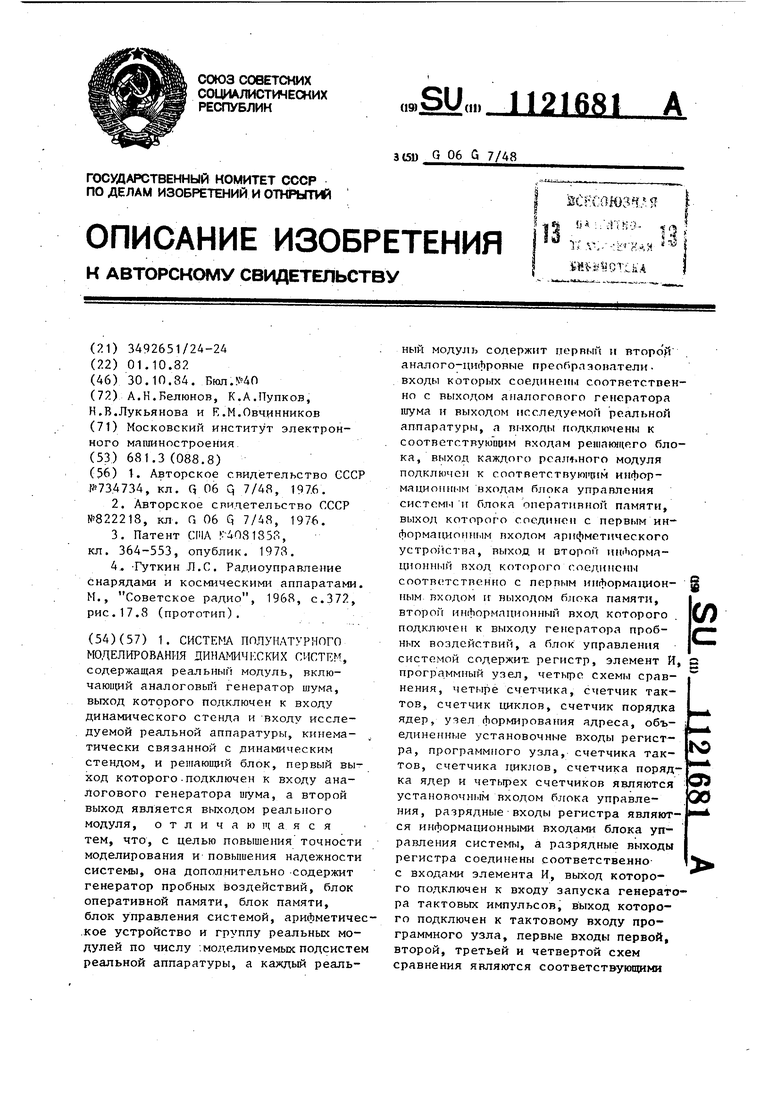

1. СИСТЕМА ППЛУНАТУРНОГО МОДЕЛИРОВАНИЯ ДИИАМИЧ1-;СКИХ СИСТЕМ, содержащая реальный модуль, включающий аналоговьш генератор шума, выход которого подключен к входу динамического стенда и входу исследуемой реальной аппаратуры, кинема- ., тически связанной с динамическим стендом, и реигаюищй блок, первый выход которого-подключен к входу аналогового генератора uiyMa, а второй выход является выходом реального модуля, отличающаяся тем, что, с целью повышения точности моделирования и повышения надежности системы, она дополнительно -содержит генератор пробных воздействий, блок оперативной памяти, блок памяти, блок управления системой, ариЛметичес.кое устройство и группу реальных модулей по числу .моделипуемых подсистем реальной аппаратуры, а каждый реальный модуль содержит первый и второй . аналого-цифровые преобрпаонптели входы которых соединен, соответственно с выходом аналогового генератора шума и выходом исследуемой реальной аппаратуры, а выходы подключены к соответствую 01М входам ре 1а ощего блока, выход каждого pcajTf.Horo модуля подключег к соответствую 11 М И1 форма дипин|-1м входам блока управления систем. г блока опсрат 1Я юй памяти, которого coeди O с перВ1 М информа,.1м ВХОДОМ ар фметического устройства, и второГг ii(iiopMaЦИО1 Н.Й вход КОТОрОГО ( § соответственно с первь м {формацион 1ым входом Г выходом б. памяти, (Я второй - фОрМПЦ 10ННЫЙ ВХОД КОТОРОГО . подключе к генератора пробс воздействий, а блок управления системой содержит, регистр, элемент И, программ 1Ы1Ч узел, сравнения, четыре счетчика, счетчик тактов, счетчик циклов, счетчик порядка ядер, узел формирования адреса, объединен п,1е установочные входы регистра, программ(ого узла, счетчика тактов, счетчика IWKJCOB, счетчика порядка ядер и четырех счетчиков являются установочн.1м входом блока управления, разряднь е входы регистра являются информационными входами блока управления системь, а разрядные выходы регистра соеди 1ены соответственнос входами элемента И, выход которого подключен к входу запуска генератора тактовых импульсов, выход которого подключен к тактовому входу программного узла, первые входы первой, второй, третьей и четвертой схем сравнения соответствующими

Изобретение относится к специализированным средствам вычислительной . техники и может быть использовано при полунатурном моделировании лета-. тельных аппаратов, энергоблоков, технологических процессов и т.п. совместно с системами управления.

Известны устройства предназначенные для полунатурного моделирования нелинейных систем, содержащие блок реальной аппаратуры, установленной на платформе вибрационного стенда, блок моделирования, блок моделирования обратной передаточной функции.

атчик колебаний, сумматор, усилиель и блок усреднения, причем выод датчика колебаний соединен с вхоом блока моделирования, выход котоого соединен с входом блока модели- 5 ования обратной передаточной функции, его выход и выход датчика колеаний через блок усреднения соединены с входами сумматора, выход которого через усилитель соединен с вибрацион-10 ным стендом, выходы которых подсоеинены к входу блока реальной аппаратуры, а его выход соединен с входом датчика колебаний Л и 2j . :

Однако указанные устройства име- 15 ют невысокую надежность, обусловленную замкнутой структурой полунатурной модели, состоящей из блока моделирования математической :части моделируемой модели, сопряженного с. ком- 20 плексом технической аппаратуры, низкую точность, обусловленную неоднократным использованием полунатурного моделирования для получения статистически устойчивых результатов 25 моделирования большую сложность создания полунатурной модели в связи с необходимостью моделирования в реальном времени.

Известно также устройство, содер- зо жащее хронометр, регистр сдвига, блок управления, арифметическологическое устройство и блок памятиj с помощью которого возможно вычис- . ление ядер винера з .35

Наиболее близкой к предлагаемому является система полунатурного моделирования с динамическими стендами, включает в себя имитатор воздействий, динамический стенд, на подвижной Q платформе которого установлена исследуемая реальная аппаратура, а также решающее устройство, причем выход реальной аппаратуры подсоединен к входу решающего устройства, вы- j ход которого соединен с входами динамического стенда и имитатора воздействий, выходы которых соединены с входами реальной аппаратуры. Данная система позволяет воспроизводить в ,« лабораторных условиях режимы полета летательного аппарата, весьма близкие к реальным 4 .

Сложные динамические системы являются обычно многоконтурными. Пору- 55 натурное моделирование такой системы осуществляется путём последовательного моделирования системы с нара1циваемыми контурами управления Причем для решения задач таких как установление источников отказов сИстемы и получение статистических характеристик системы, проводится МП циклов моделирования, где М - чи ло циклов моделирования по каждому контуру управления, п - число кон туров управления.. Такое моделирование сопряжено со значительными материальными и временными затратами, поскольку приходится неоднократно привлекать динамические стенды и реальную аппаратуру. Многократное использование элемента приводит к уменьшению его ресурса, а следовательно, уменьшается вероятность безотказной работы всей полунатурной модели, представляющей последовательное соединение элементов.

Поскольку полунатурное моделирование осуществляется по замкнутому контуру, необходимо, чтобы оно протекало в реальном масштабе времени. От реального времени зависит не только временная последовательность решения тех или иных задач, но и получаемые в результате данные Эффективность моделирования в реальном времени определяется задеркой сообщений перед их обработкой, вероятностью потери сообщений, необходимостью подключения дополнительных вычислительных средств. Поэтому одной из важных проблем полунатурного моделирования является проблема оперативного управления вычислительным процессом в реальном времени и высокого быстродействия вычислительных средств.

Цель изобретения - повышение, точности моделирования и повышение надежности системы путем введения взаимосвязанных реальных модулей по числу подсистем реальной аппаратуры.

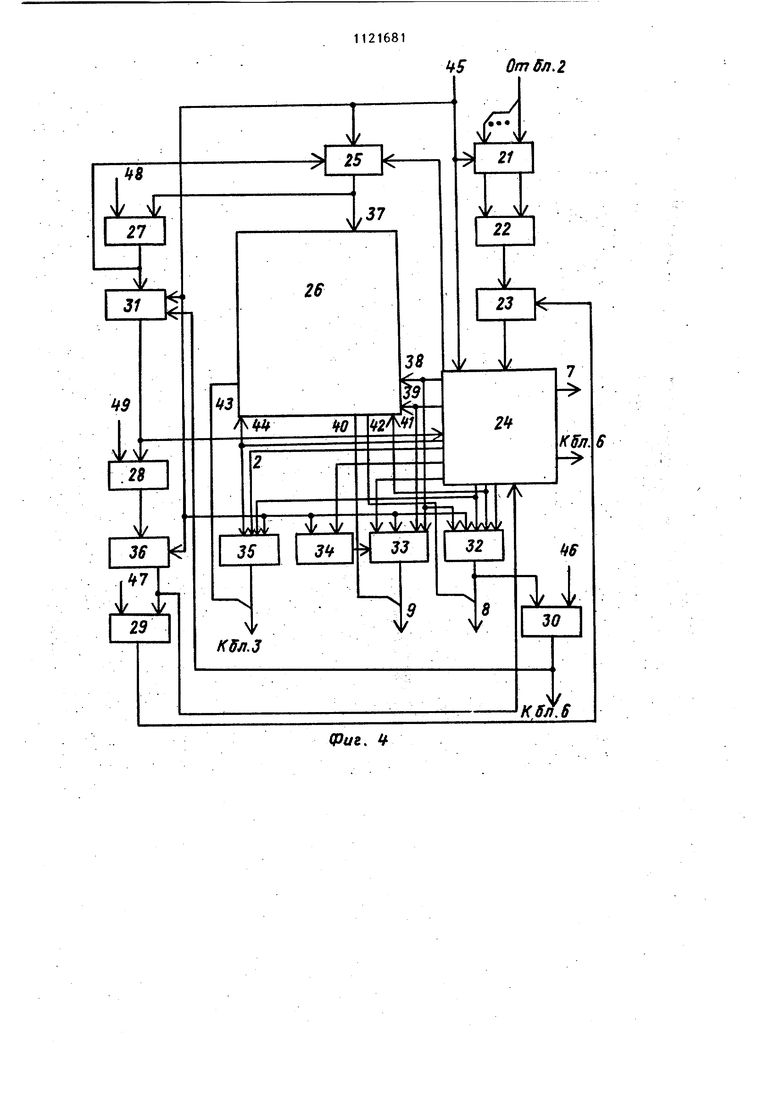

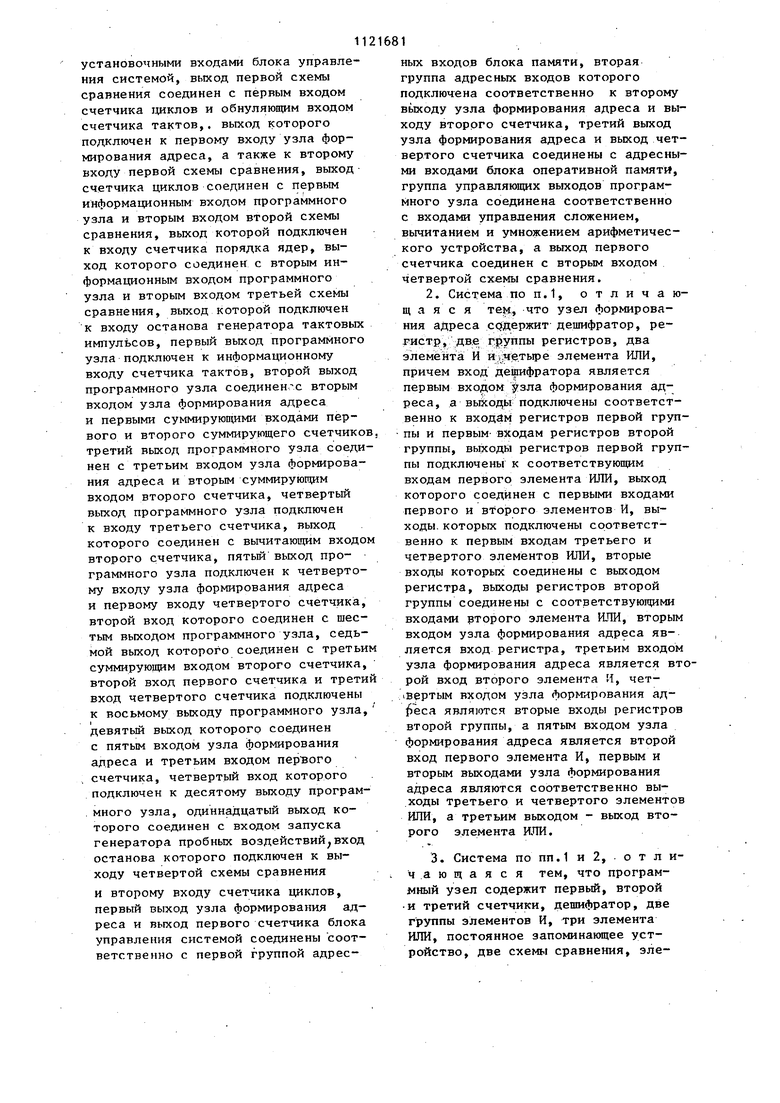

Поставленная цель достигается тем, что в систему полунатурного моделирования динамических систем, содержащую реальный модуль,- включающий аналоговый генератор шума, выход которого подключен к входу динамического стенда и входу исследуемой реальной аппаратуры, кинематически связанной с динамическим стендом., и решающий блок, первый выход которого подключен к .входу аналогового генератора шума, а второй выход является выходом реального модуля, введены генератор пробных воздействий, блок оперативной памяти, блок памяти, блок управления системы, арифметическое устройство и группа реальных модулей по числу моделируемых подсистем реальной аппаратуры, а каждый реальный модуль содержит первый и второй аналого-цифровые преобразователи входы которых соединены соответственно с выходом аналогового генератора шума и выходом исследуемой реальной аппаратуры, а выходы подключены к соответствующим входам решающего блока, выход каждого реального модуля подключен к соответствующим информационным вхоцам блока управл,ения системы и блока оперативной памяти, выход которого соединен с первым информационным входом арифметического устройства, вьгход и второй информационный вход которого соединены соответственно с первым информационным входо и вьгходом блока памяти, второй инфор мационный вход которого подключен к выходу генератора пробных воздействий,а блок управления системой соде жит регистр, элемент И, программный узел, четыре схемы сравнения, четыре счетчика, счетчик тактов, счетчик циклов, счетчик порядка ядер, узел формирования адреса, объединенные установочные входы регистра, программного узла . счетчика тактов, счетчика циклов, счетчика порядка ядер и четырех счет чиков являются установочньтм входом блока управления разрядные входы регистра являются информа--, ционными входами блока управления системы, а разрядные выходы регистра соединены соответственно с входам элемента И, выход которого подключен к входу запуска генератора тактовых импульсов, выход которого подключён к,тактовому входу программного узла первые входы первой, второй, третьей и четвертой схем сравнения являются соответствующими установочными входа блока управления системой,выход перв схемы сравнения соединен с первым входом счетчика циклов и обнуляющим входом счетчика тактов, выход которого подключен к первому входу узла формирования адреса а также второму входу первой схемы сравнения,выход счетчика циклов соединен с первым информационным входом программного узла и вторым входом второй схемы сравнения, выход которой подключен к входу счетчика порядка ядер, выход которого соединен с вторым информационным входом программного узла и вторым входом третьей схемы сравнения, выход которой пс цключен к входу останова генератора тактовых импульсов, первый выход программного узла подключен к информационному входу счетчика тактов, второй выход программного узла соединен с вторым входом узла формирования адреса и первыми суммирующими входами первого и второго суммирующего счетчиков,третий выход программного узла соединен с третьим входом узла формирования адреса и вторым суммирующим входом второго счетчика, четвертый выход программного узла подключен, к входу третьего счетчика, выход которого соединен с вычитающим входом второго счетчика,пятый выход программного узла подключен к четвертому входу узла формирования адреса и первому входу четвертого счетчика, второй вход которого соединен с шестым выходом программного узла, седьмой выход которого соединен с третьим суммирующим входом второго счетчика, второй вход первого счетчика и третий вход четвертого счетчика подключены к восьмому выходу программного узла, девятый выход которого соединен с пятым входом узла формирования адреса и третьим входом первого счетчика, четвертый вход которого подключен к десятому выходу программного узла, одиннадцатый выход которого соединен с входом запуска генератора пробных воздействий, вход останова которого подключен к выходу четвертой схемы сравнения и второму входу счетчика циклов, первый выход узла формирования адреса и выход первого счетчика блока управления системой соединены, соответственно с первой группой адресных входов блока памяти, вторая группа адресных входов которого подключена соответственно к второму выходу узла формирования адреса и выходу второго счетчика, третий выход узла формирования адреса и выход четвертого счетчика соединены с адресными входами блока оперативной памяти, группа управляющих выходов программного узла соединена соответственно с входами управления сложением, вычитанием и умножением арифметического устройства, а выход первого счетчика соединен с вторым входом четвертой схемы сравнения. Узел формирования адреса содержит дешифратор, регистр, две группы регистров два элемента И и четьфе элемента ИЛИ, причем вход дешифратора является первым входом узла формирова ния адреса, а выходы подключе-: ны соответственно к входам регистров первой группы и первым входам регистров второй группы, выхо- ды регистров .первой группы подключены соответственно к входам первого элемента РШИ, выход которого соединен с первыми входами первого и второго элементов И, выходы которых подключены соответственно к первым входам третьего и четвертого элементов ИЛИ, вторые входы которых соединены с выходом регистра,, выходы регистров второй группы соединены с соответствующими входами второго элемента ЮТИ вторым входом узла формирования адре са является вход регистра, третьим входом - второй вход второго элемента И, четвертым входом узла формиро вания адреса являются вторые входы регистров второй группы, а пятьм входом узла формирования адреса явля ется второй вход первого элемента И, : первьш и вторым выходами узла формирования адреса являются соответственно , выходы третьего и четвертого элементов ШШ, а третьим выходом -вы-, ХОД второго элемента ИЛИ. Программный узел содержит первый, второй, и третий счетчики, дешифратор, две группы элементов И, три элемента ИЛИ, постоянное запоминающее устройство, две схемы сравнения, элемент И и триггер, причем тактовьй вход первого счетчика является такто вым входом программного узла, установочным входом которого является установочный вход первого счетчика, соединенный с первыми входами первого и второго элементов.ИЛИ, первым и вторым информационными входами программного узла являются соответствен но первый и второй адресные входы постоянного запоминающего устройства первьтй адресный вход которого соеди нен также с входом третьего элемента ИЛИ, разрядные выходы первого счетчи ка соединены соответственно с входам дешифратора, первый - одиннадцатьй выходы которого подключены соответственно к первым входам элементов И первой группы, вторые входы которых объединены и соединены с первым выходом постоянного запоминающего устройства, второй и третий выходы которого подключены соответственно к первым входам первой и второй схем сравнения, вторые входы которых соединены соответственно с выходами второго и третьего счетчиков, а управляющие входы первой и второй схем сравнения соединены с двенадцатым и тринадцатым 1 выходами дешифратора одиннадцатый выход дешифратора соединен также с информационным входом второго счетчика, установочный вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с выходом первой схемы сравнения, первым входом элемента И и информационным входом третьего счетчика, установочный вход которого подключен к выходу первого элемента ИЛИ, первому входу триггера .и инверсному входу элемента И, выход которого соединен с вторым входом триггера, выход которого подключен к первому инверсному входу первого элемента И второй группы и третьему адресному входу постоянного запоминающего устройства, четвертый адресный вход которого соединен с выходом второго счетчика, выход второй схемы сравнения подключен к второму входу первого элемента ИЛИ, выход первого элемента И первой группы соединен с первым прямым входом первого элемента И второй группы и первыми входами второго и четвертого элементов И второй группы, выход второго элемента И первой группы соединен ..с первыми входами третьего и пятого элементов И второй группы, выход второго элемента ИЖ подключен к второму инверсному входу первого элемента И второй группы и вторым входам второго-пятого элементов, И второй группы, первым выходом программного узла является выход шестого элемента И первой группы, вторым, третьим и четвертым выходами программного узла являются соответст вённо выходы третьего и четвертого элементов И первой группы и выход второго элемента И второй группы. пятым и шестым выходами программного узла являются соответ ственно выходы седьмого элемента И второй группы седьмым выходом являются объединенны выходы четвертого и пятого элементов И второй группы, восьмым, девяты и десятым выходами программного узла являются соответственно выходы одиннадцатого, десятого и второго элемен тов И первой группы, одиннадцатым выходом программного узла является выход первого элемента И второй группы,- а группой управляющих выхо-. дов программного узла являются выход пятого, восьмого и девятого элементов И первой группы. На фиг.1 представлена блок -схема системы полунатурного моделирования динамических систем; на фиг.2 блок-схема реального модуля на фиг.З - сумма.решающего блока; на фиг,4 - блок управления; на фиг.З блок формирования начального адреса на фиг.6 - схема распределителя импульсов. Система содержит блок 1 памяти, группу реальных модулей 2, блок 3 оперативной памяти, блок А управлен системы, арифметический блок 5, генератор 6 пробных воздействий и выходы 7-9 блока управления системы, v Реальный модуль 2 содержит анало го-цифровые преобразователи 10 и 11 аналоговый генератор,12 шума, динам ческий стенд 13, исследуемую реальную аппаратуру 14 и решаюищй блок 1 причем выход аналогового генератора 12 шума соединен с входами динамического стенда 10 и реальной аппаратуры 14, второй вход которой соединен с выходами динамического стенда 13, выход реальной аппаратуры 14 подключен к входу АЦП 11, а его выход соединен с одним из входов решающего блока 15, другой вход которого соединен с выходом А1Щ 10, -первый выход решающего блока 15 соединен с входом аналогового генератора 12 шума, а второй его выход является выходом модуля и сое динен с входом блока оперативной памяти, 3 и входом блока 4 управления системы. Решающий блок 15 реализован по схеме,предложенной в з и содержит хронометр 16, управляющий работой генератора шума блок 17 управления регистр 18 сдвига, арифметико-логическое устройство (АЛУ) 19 и блок 20 памяти. Решающий блок 15 включается в схему реального модуля 2 следующим образом.. Выход АЦП 10 соединен с входом регистра cдвигa a выход АЦП 11 соединен с входами АЛУ 19 и блока 17 управления. Блок 4 управления системы (фиг,4) содержит регистр 21, элемент И 22, генератор 23 тактовых импульсов, программный узел 24, счетчик 25 тактов узел 26 формирования адреса, первую - четвертую схемы 27-30 сравнения, счетчик 31 циклов, первыйчетвертый счетчики 32-35 импульсов, счетчик 36 порядка ядра, входы и выходы 37-44 узла 26 формирования адреса установочньй вход 45 блока и установочные входы 46-49.схем сравнения. Блок 26 формирования адреса содержит первую 50 и вторую 51 группы регистров, первый 52 и второй 53 элементы ИЛИ, первый 54 и второй 55 элементы И, регистр- 56, третий 57 и четвертый 58 элементы ИЛИ, а также дешифратор 59. . . . Распределитель 24 импульсов реализован по схеме фиг.6. Он содержит дешифратор 60 (ДШ); узел 61 блокировки, включаюпд1й в себя первую группу элементов И 62, вторую группу элементов И 63, элемент ИЛИ 64, триггер 65, второй счетчик 66, второй элемент ИЛИ 67, вторую и первую схемы 68,69 сравнения, элемент 70, третий счетчик 71, элемент ИЛИ 72 и постоянное запоминающее устройство 73, а также первый счетчик 74. Назначение сигналов распределителя 24 импульсов (РИ) приведено в табл.1, а порядок выдачи синхросигналов рас пределителем импульсов -.в табл.2. Программный узел работает следующим образом. . При подаче сигналов на 1-й (управляющий) вход счетчика 74 от блока 23 на выходе ДШ 60 формируется повторяющаяся последовательность сигналов с 1 по 13, представляющих собой собственный цикл работы ДШ 60, из которых сигналы с 1 по 11 используются для формирования выходных управляющих сигналов РИ 24 /СИ1-СИ11), а сигналы с 11 по 13 - для управления элементами узла 61 блокировки. Каждый из циклов работы системы представляет собой последовательност выполнения m тактов. В свою очередь каждый такт представляет собой выпол нение одного или ряда собственных циклов ДШ 60 в зависимости от порядка рассчитываемой свертки. В каждом собственном цикле ДШ 60 осуществляет ся блокировка его сигналов с 1 по 11 При этом в тактах с второго по m -и каждого из N циклов условия блокировки сигналов СИ 1-СИ 11 одинаковы (табл.2), . Блокировка сигналов 1-10 ДШ 60 осуществляется элементами И 62 и 63 в соответствии с кодом сигналом блок ровки, поступающим с первого выхода ПЗУ 73. При подаче на ПЗУ 73 кода адреса на его первом, втором и третьем выходах формируется потендиальньтй код числа. Код адреса - А-разрядный код, начиная со старшего разряда состоящий из кода порядка ддра (-разрядов), снимаемого с выхода счетчика 36, кода текущего номера цикла (гразрядов) снимаемого с выхода счетчи ка 31 и выхода триггера 65 (1 разряд и кода текущего номера собственного цикла ДШ 60 (р разрядов),снимаемого с выхода счетчика 66. Код числа, снимаемый с первого, второго, третьего выходов ПЗУ 73- . это В-разрядный код. Начиная с мпа младшего разряда код числа сострит из кода сигналов блокировки (11 разрядов) , снимаемого с первого выхода ПЗУ 73 и используемого для блокировки сигналов СИ 1 - СИ 11, кода максимального числа собственных циклов ДШ 60 в текущем такте (5 разрядов) снимаемого со второго выхода ПЗУ 73 и кода максимального числа тактов в цикле ( разрядов), снимаемого с третьего выхода ПЗУ 73. С изменением любого из разрядов кода адреса с выхода ПЗУ 73 снимается новый код числа. Один из разрядов кода адреса формируется триггером 65, которьй находится в состоянии О в первом такте и.в состоянии 1 во всех ос. тальных тактах. Это вызвано тем, .что в тактах со 2-го по w-и каж, дого из циклов условия блокировки 11 12 сигналов СИ 1 - СИ 11 одинаковы, и в то же время отличаются от условий блокировки в первом такте (табл.2). С каждым собственным циклом ДШ 60 состояние счетчика 66 увеличивается на единицу, при совпадении кода счетчика 66 с кодом на втором выходе ПЗУ 73 схема 69 сравнения вьдает сигнал окончания такта, обнуляющий счетчик 66 и увеличивающий состояние счетчика 71 на единицу. При этом триггер 65 при вьтолнении 1-го такта находится в нуле, а при вьтолнении тактов с 2-го по гп -и в единице. С каждым тактом состояние счетчика 71 увеличивается на единицу. При совпадении кода счетчика 71 с кодом на 3-ем выходе ПЗУ 73 схема 68 сравнения вьщает сигнал окончания цикла, обнуляющий счетчик 71 и триггер 65. Прежде чем начать- полунатурное моделирование, динамическая система подвергается расчленению, т.е. из моделируемой системы выделяется изготовленная реальная аппаратура, образующая реальную подсистему, оставшаяся часть системы, которая не может быть воспроизведена реально в Лабораторных условиях, описывается математической моделью, причем все внешние связи между математической моделью и реальной аппаратурой разрьшаются. Принцип работы системы заключается в следующем. В реальных модулях 2 производится идентификация реальной аппаратуры с цепью определения ее динамических характеристик, В зависимости от сложности моделируемой системы она может содержать несколько реальных подсистем, которые идентифицируются в несвязанных реальных модулях 2, т.е. осуществляется независимая идентификация реальных подсистем. Работа каждого реального модуля происходит в следующем порядке. В качестве тестирующего воздействия на реальную аппаратуру, а также входного воздействия на динамический стенд выбирается бельй гауссов процесс;, который вырабатывается генератором 12. Работой генератора 12 управляет хронометр, включенный в решающий блок 15. - Непрерывный бельш гауссов процесс x(t). и реакция на него реальной аппаратуры 14 преобразуетс в дискретные процессы в соответствующих АЦП 10 и 11. Результатом идентификации являет ся рассчитанный набор ядер Винера, которые представляют собой взаимоко реляционную функцию соответствующег порядка. Ядро первого порядка рассчитывае ся за К циклов (к максимальное числ дискретов ядра), т.е. ядро содержит К точек. В результате расчетов по ч лу по каждому циклу определяется очередная точка ядра. Для ядра перв го порядка каждьй цикл содержит N-К тактов (k - текущий дискрет ядра). Схема работы разрешающего блока 15 для расчета ядра первого порядка имеет вид: о цикл. Расчет нулевой точки ядраЬ 1такт: У(0)Х(0-0)У(0)Х(0) 2такт: У(1)Х(1-0)У(1)Х(1) NTaKT: y(N)X(N-0)y(N)X(N) 1 ЦИКЛ: Расчет первой тояки ядраЬ ( 1такт: У(1)Х(1-1)У(1)Х(0) 2такт:У(2)Х(2-1)У(2)Х(1) Н-1 такт y(N)X(N-1) К цикл: Расчет К-й точки ядра h (К) 1такт:У(М-К)Х(0) 2такт: y(N-K+1)X(1) N-K такт: y(N)X(N-K) В каждом цикле расчеты всех тактов суммируются и умножаются на масштабный коэффициент Аналогично осуществляется расчет яд более высоких порядков с той лишь разницей, что в зависимости от порядка ядра количество циклов увеличивается. Рассчитанные значения ядер каждо порядка записываются в блок 3 опера тивной памяти. После записи последнего из рассчитываемых порядков яде во всех разрядах регистра 21 блока 4 утгравления система- занимает единица. На этом первый этап моделирования заканчивается и начинается второй этап полунатурного моделирования. В результате первого этапа в оперативной памяти 3 записана матрица ядра (П на п (где m - максимальное число столбцов, равное числу реальных модулей, П - максимальное число строк, равное максимальному порядку ядер Винера). Матрица имеет следуюпщй вид Ьщ пг На втором этапе моделирования осуществляется композиция подсистем согласно структурной схеме моделируемой системы. Эта схема задается очередностью порядковых номеров реальных модулей 2, причем для первого реального модуля определяется свертка ядра с белым гауссовским процессом, а для последующих модулей определяется свертка ядра с выходным сигналом предыдущего модуля. Работой управляет блок 4 управления системы. Система полунатурного моделирования позволяет моделировать как замкнутые, так и разомкнутые динамические системы. Для обоих случаев второй этап моделирования осуществляется зал--(Нн1) циклов (где п - максимальный порядок ядер Винера,. N - максимальный порядковый номер дискрета). Каждый цикл состоит из № тактов (где m максимальное число реальных модулей 2). Обычно выбирается одно значение N , одинаковое для всех hi реальных модулей. Значение П также выбирается для всех реальных модулей, исходя из максимального значения h всех .гп реальных модулей. В первом цикле осуществляется обработка нулевого дискретаY, (0) по всем модулям, т-, е. проводится свертка входного сигнала с ядром первого порядка. В последующих циклах обрабатываются последующие номера дискретов также по всем реальным модулям. Начиная со второго цикла проявляётся отличие в моделировании замкнутых .и разомкнутых систем. Это отличие возникает только в первом такте, где осуществляется свертка ядра первого реального модуля с белым гауссовским процессом. Если система замкнута, то свертывается с разностью текущего дискрета Х(О и предьщущего дискретаУп,щ(-1) (результат fn -го такта предыдущего цикла), причем текущее значение переменной i выбирается с учетом значения переменной свертываемого ядра. Это отличие сохраняется при свертке с любым порядком ядра. Если система разомкнута, то ядро свертывается только с белым , гауссовским процессом Х(1), причем текущее значение дискрета также выбирается с учетом значения перемен ной свертываемого ядра. Рассмотрим подробнее очередность действий системы полунатурного моделирования на втором этапе, причем пусть, как более; общий случай, моделируется динамическая система замкнутого типа. Исходное состояние всех счетчиков устанавливается сигналом по линии 45 связи. / Работа системы моделирования заключается в последовательном вьшолнении ряда циклов под управлением программного узла 24 и блока 4 улрав ления. Нулевой цикл - запуск генератора 6 пробных воздействий, формирование входных чисел X(i).,N в виде белого дискретного гауссовского про цесса и запись их в блок 1 памяти. Код адреса ёаписи чисел состоит из кода постоянного начального адрес формируемого регистром 56 и передаваемого через элемент ИЛИ 57, и кода переменного текущего адреса. формируемого счетчиком 32 адреса за писи чисел. Перед записью каждого очередного числа Х() в блок 1 памя сигналом от узла 24 состояние.счетчи ка 32 увеличивается на единицу.При записи в блок 1 памяти N -го числа X(N) происходит совпадение выходног кода счетчика 32 и N -го кода длины массива чисел, заданного в схеме 30 1 сравнения, при этом управляющий сиг нал, ИДУ1ТИЙ с выхода схемы 30 сравнения, останавливает работу генератора 12 шума. После записи входных чисел после довательно обрабатываются ядра всех порядков начиная с первого, т.е. осу ществля.ется композиция всех реаль8116ных подсистем. Сначала вьшолняется | первая группа N +1 циклов каждый по m тактов, в результате чего определяется свертка входного сигнала с ядром первого порядка всех реальньк модулей. Эта свертка является линейной частью реакции моделируемой системы. Далее выполняется выгорая группа циклов по определению свёртки С ядром второго порядка, т,е. определяется квадратическая реакция моделируемой системы, и т.д. Всего выполняется п (N+1) циклов (где И - максимальный порядок ядер Винера всех остальных подсистем). Ниже приведенное напряжение,поясняющие алгоритм функционирЪвания системы полунатурального моделирования на втором этапе дпя более общего сл:1учая, когда моделируемая замкнутая система, причем, если система разомкнута, работа осуществляется по такому же алгоритму, с той лишь розницей, что в первом такте каждого цикла ядра свертываются только с входным сигналом. Первая группа N+1 циклов, в которой осуществляется свертка с ядрами первого порядка hi, U),h (К),.., ,h,n (К), (где Кмаксималъное число дискретов ядра. 1 цикл: Обработка нулевой точкиУ,(0) по всем реальным модулям :Y,,CO)iCO)(О) - для первого 1 такт; модуля, ti2tO)) ) композиция 2 такт: . первых двух реаль:ных модутакт: V,(0ll Н,5(0)(:0) - композиция первых трех реальных модулей m TaKTt,(0)hi(0)(0)- композиция модулей, нулевая точка линейной реакции модулируемой системы2 цикл: Обработка первой точки Y., ПОвсем реальным модулям 1 такт: .,,co)x(AbY,(o)l + h,, 17 - для 1-го модуля 2 такт: Y,2W h,,(OVV,4Ub,j(Al,( композиция первых двух модулей 3 такт: .,tO b;,tQ)X,2(A,tb,,(MY,,jCoV - композиция первых трех модулей М такт: : n,obb,(o)Y,.,(,(ov,.,(o)- композиция m модулей первая точка линейной реакции моделируемой системы В (N+1)-M цикле определяется композиция модулей и определенная точка линейной реакции моделируемой системы. На -этом заканчивается опре деление массива дискретов Ч (N) , я ляющихся линейной реакцией моделиру мой системы. Аналогично определяются квадра тичная реакция и т.д. моделируемой системы. В исходном состоянии счетчики 74 66,71 и триггер 65 обнулены. программного узла 24 начинается с момента запуска генератора 23. При этом в нулевом цикле работы устройс ва выполняется N собственных цикло ДШ 60, причем в первом собственном цикле ДШ 60 кодом сигналов блокиров ки разрешается прохождение на выход РИ 24 сигналов СИ 1, СИ 2, СИ 3. - Сигналом СИ 1 запускается генера тор 6 пробных воздействий, сигналом СИ 2 состояние счетчика 32 увеличивается на единицу и сигналом СИ 3 р решается выдача кода адреса записи чийел в блок 1 памяти по линии 8 св зи. При этом код адреса состоит в из кода начального адреса, формируе мого блоком 26, и кода текущего адреса, формируемого счетчиком 32. В собственных циклах ДШ 60 с вто рого по (М-1)-й кодом сигналов блокировки разрешается выход сигналов 8118 СИ 2, СИ 3 с назначением, аналогичным первому собственному циклу ДШ 60. В N -м собственном цикле ДШ 60 распределитель 24 выдает сигналы СИ 2, СИ 3, СИ 11. Назначение сигналов СИ 2 и СИ 3 аналогично предьщущему. Сигналом СИ 11 обнуляется счетчик 32. С каждым сигналом СИ 2 состояние счетчика 32 увеличивается на единицу. При совпадении кода счетчика 32 с кодом, заданным в схеме 30 сравнения, она срабатьшает. Сигналом с ее выхода останавливается генератор 12 пробных сигналов и увеличивается на единицу состояния счетчика 31 (из нулевого в единичное). На этом заканчивается нулевой цикл и начинается первый цикл для расчета свертки первого порядка. В первом цикле в первом такте в , соответствии с назначением синхроимпульсов табл.1 по коду адреса, формируемому блоком 26 и счетчиком 33, из блока 1 памяти считывается число X и записывается в АЛУ 5. Далее по коду адреса, формируемому блоком 26 и счетчиком 35, из блока 3 оперативной памяти считывается значение ядра и записывается в АЛУ 5. Записанное число X со значением ядра и результат остаются в АЛУ 5 и записываются в блок 1 памяти. В первом цикле в тактах с второго по m -и действия аналогичны за исключением считывания чисел, X, которое не производится, так как в этих тактах перемножается значение ядра с числом У (т.е. с результатом предьщущего перемножения), находящемся уже в АЛУ 5. При этом с каждым тактом состояние счетчика 25 увеличивается на единицу. В конце первого цикла при совпадении кода счетчика 25 с кодомj заданным в схеме 27 сравнения, она срабатывает и состояние счетчика 31 циклов увеличивается на единицу, что соответствует началу второго цикла. Работа устройства в циклах с второго по (N-Я) аналогична работе в первом цикле с той лишь разницей, что с увеличением номера цикла увеличивается число сложений, вычитаний и умножений, выполняемых в АЛУ 5. Следовательно, с увеличением номера цикла увеличивается максимальное число собственных циклов

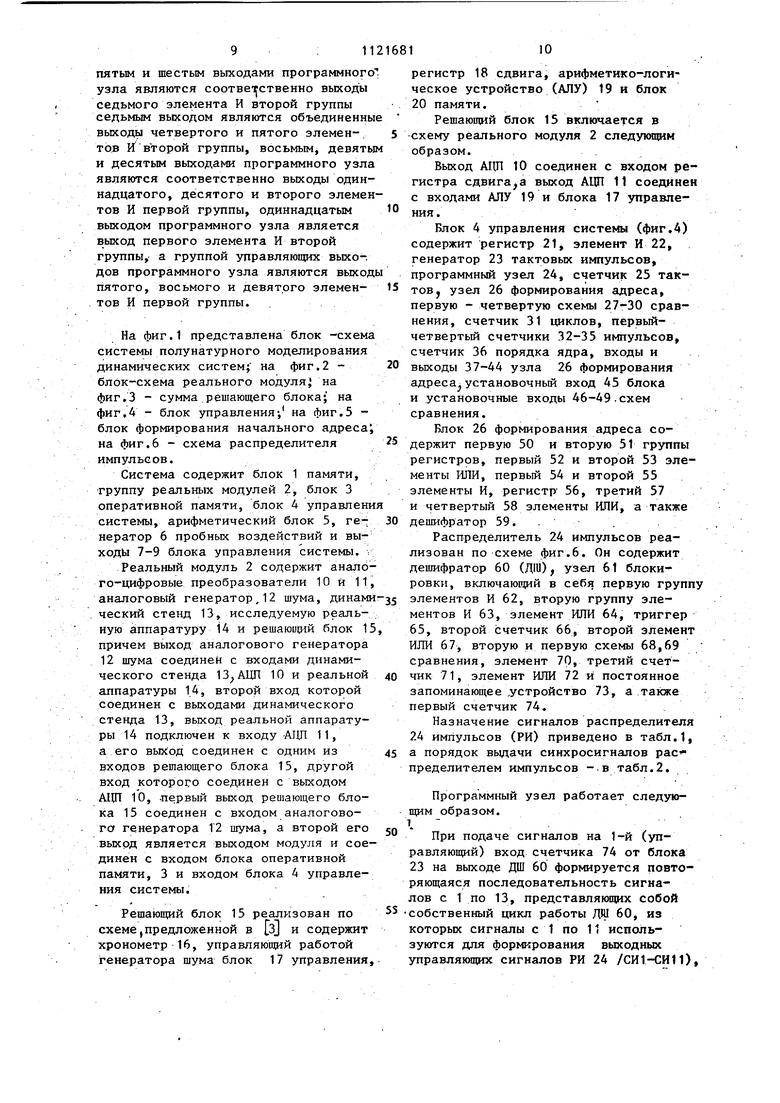

19

ДП1 60 и меняется код сигналов блокировки.

Кроме того, в каждом цикле увеличивается на единицу реверсивное состояние счетчика 34, которое используется как начальное состояние реверсивного счетчика 33, работающего на вычитание при формировании кода адреса считьшания чисел Х,У из блока 1 памяти.

. При достижении счетчиком 31 кода максимального числа циклов срабатыв ет схема 28 сравнения и увеличивает на единицу состояние счетчика 36. На этом заканчивается расчет свертки первого порядка. Для свертки с ядром каждого порядка реализуется последовательность (N+1) циклов. Работа устройства аналогична рассмотренной.

Блок формирования начального адреса запускается счетчиком 25, увеличивающим свое состояние в каждом цикле. При этом в каждом такте состояние счетчика увеличивается на единицу, а в конце цикла счетчик 25 обнуляется. С каждым новым состоянием счетчика 25 сигнал появляет ся на очередном по номеру выходе дешифратора 59, которьй выбирает тот или иной узел 50 начального чисел X в блоке 1 памяти (8) Выдача кода адреса считывания чисел 1 памяти (9) Управление работой АЛУ 15 (операция +1 счетчика 25 Вьщача кода адреса считывания ядер из блока 4 оперативной памяти Управление работой АЛУ 15 (операция Управление работой АЛУ 5 (операция с Выдача кода адреса записи чисел У в оперативной памяти

СИ11

Установка исходного состояния счетчиков

168120

кода адреса, с выхода которого снимается начальный код адреса. Этот код проходит через элемент ИЛИ 52 и поступает или в линию 42 при записичисел Х,У в блок 1 памяти, или в линию связи 40 при считывании чисел Х,У. Выбор линии 42 или 43 производится сигналом распределителя 14 импульсов, поступающим на элемент И 55 или 54.

Аналогично формируется сигнал на линии 43 связи. При этом разрешение на выдачу кодов из регистров 51 производится сигналом программного

узла 24 по линии 44 связи.

Таким образом, получение характеристик реальной аппаратуры в виде набора ядер Винера за одну достаточно длинную реализацию позволяет сократнть износ технической аппаратуры реального модуля.

На последнем этапе полунатурного моделирования сохраняется ресурс аппаратуры реального модуля, поскольку все исследования осуществляются на математических моделях реальной аппаратуры без привлечения технической аппаратуры реального модуля. Кроме того, нет необходимости моделировать в реальном масштабе времени, что позволяет повысить точность.

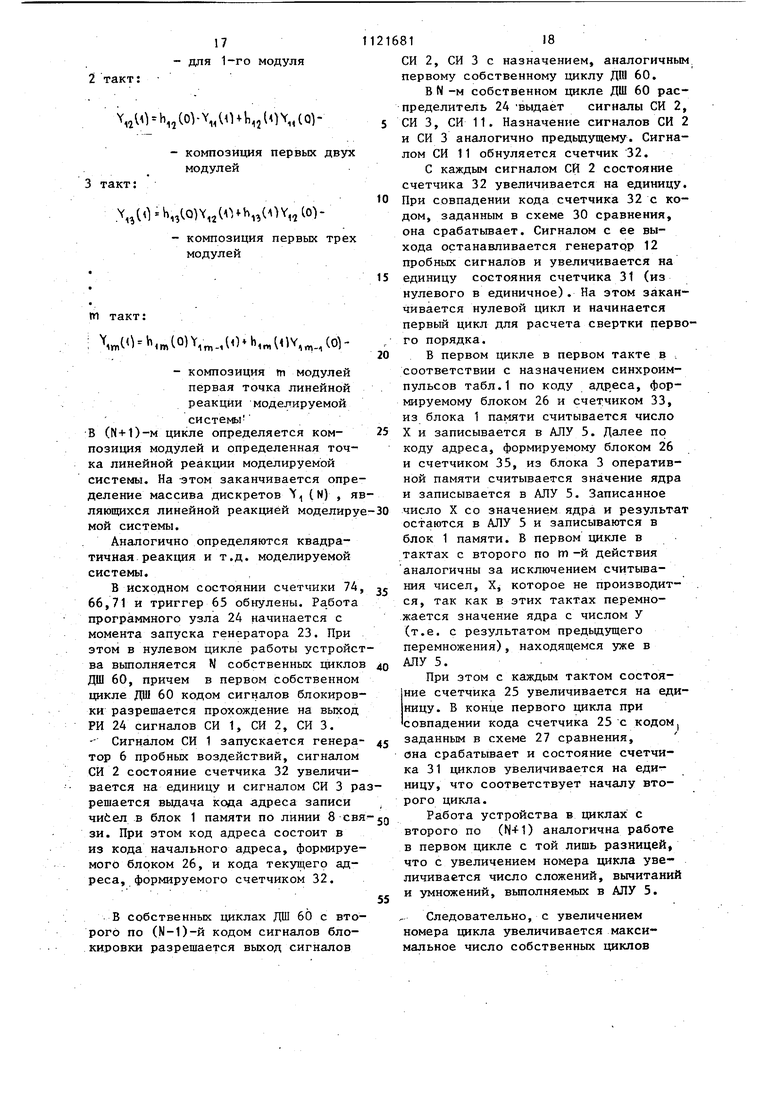

Таблица 1 У из блока вычитания) умножения) ложения) блок 3

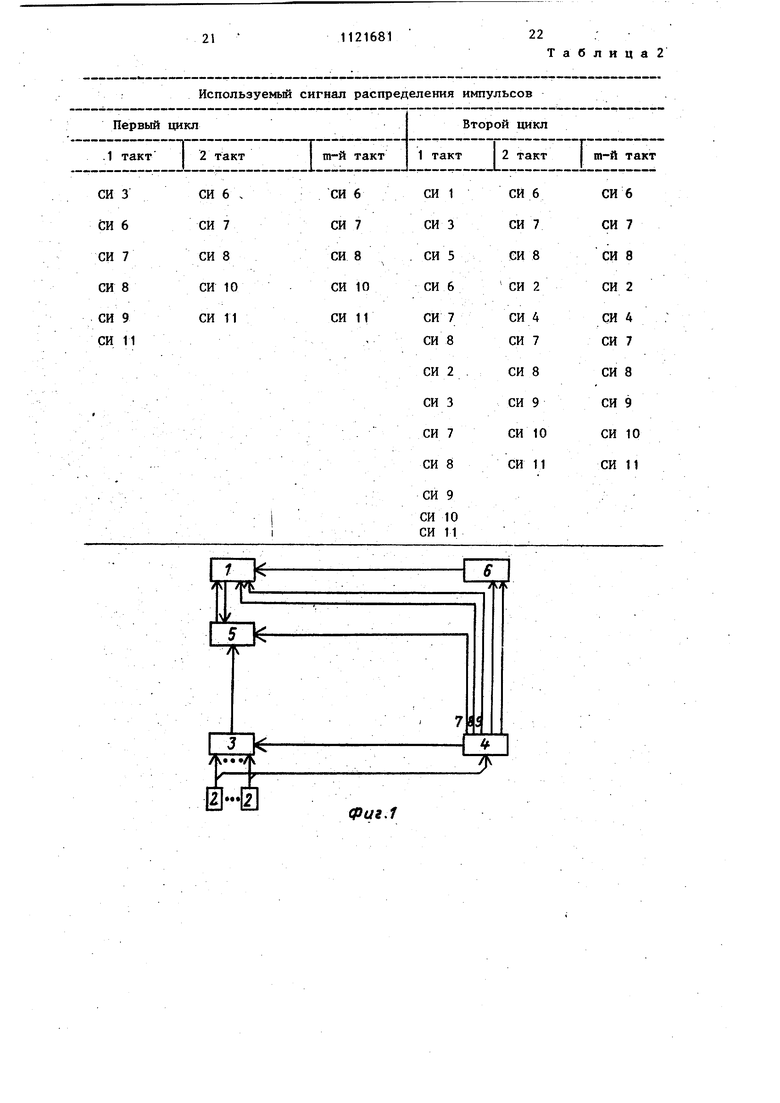

Используемый сигнал распределения импульсов

СИ 6

СИ 6

3 СИ 7 СИ 7 6 СИ 8 СИ 8 7 СИ 10 СИ 10 8 СИ 11 СИ 11

9 11

4

1

СИ 6

СИ б

1 СИ 7

СИ 7 3

СИ 8 СИ 8 5

СИ 2 6 СИ 2

СИ 4

СИ 4

7 СИ 7 8 СИ 7

СИ 8

2

СИ 8 СИ 9 3 СИ 9 СИ 10 7 СИ 10 СИ 11 8 СИ 11

9

0 1

d

3

Фиг.1

.З.

.2 От Ъл. 10

Кблл

W

Фиг.З

0тдл.11

Фиг. 5

42

СИ1 KffJT.6

К б/г. 32

(риг.6

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для полунатурного моделирования | 1976 |

|

SU734734A1 |

| Г, 06 ц , 197.6 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ получения мыла | 1920 |

|

SU364A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Радиоуправление снарядами и космическими аппаратами | |||

| М., Советское радио, 1968, с.372, рис.17.8 (прототип). | |||

Авторы

Даты

1984-10-30—Публикация

1982-10-01—Подача