(54) УПРАВЛЯЕМБШ ДЕЛИТЕЛБ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛБСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Устройство для преобразования частоты следования импульсов | 1978 |

|

SU764114A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1064477A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Устройство для автоматической регистрации радиотелеграфных сигналов | 1983 |

|

SU1092747A1 |

| Устройство формирования отметок времени | 1985 |

|

SU1415437A2 |

| Устройство для контроля | 1985 |

|

SU1295421A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Система управления многоканальнымэлЕКТРОпРиВОдОМ РОбОТА | 1979 |

|

SU805246A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

1

Изобретение относится к цифровой технике и может быть использовано в радиотехнических системах, системах автоподстройки частоты.

Известен делитель частоты следования импульсов, содержащий два счетчика импульсов, один с постоянным, другой с переменным коэффициентом деления, триггер переключения входов этих счетчиков импульсов, блок установки коэффициента деления, блок переписи 1.

Недостатком известного устройства является низкая надежность, которая обусловлена тем, что если коэффициент ; деления сменится во время окончания цикла работы устройства, то происходит неправильная запись коэффициента деления. Поэтому необходима какая-либо привязка момента смены коэффициента деления к тактовому или выходному сигналу счетчика.

Наиболее близким по технической сущности к предлагаемому изобретению является устройство, содержащее счетчик импульсов на N триггерах, дешифратор, входы которого соединены с выходами разрядов счетчика импульсов в порядке соответствующем требуемому коэффициенту деления.

элементы И-НЕ и инвертор, причем первый вход первого элемента И-НЕ соединен с выходом второго элемента И-НЕ, первым входом третьего элемента И-НЕ и входом установки в нуль счетчика импульсов, второй вход - со вторым входом третьего элемента И-НЕ и выходом дещифратора, третий вход - с входной щиной и первым входом второго элемента И-НЕ, второй вход которого подклю 1ен к выходу третьего элемента И-НЕ, а выход - с тактовым входом 0 счетчика импульсов 2.

Недостатком устройства является низкая надежность, обусловленная тем, что при переходе с одного коэффициента деления на другой возможен сбой в работе счетчика импульсов.

5

Цель изобретения - повыщение надежности.

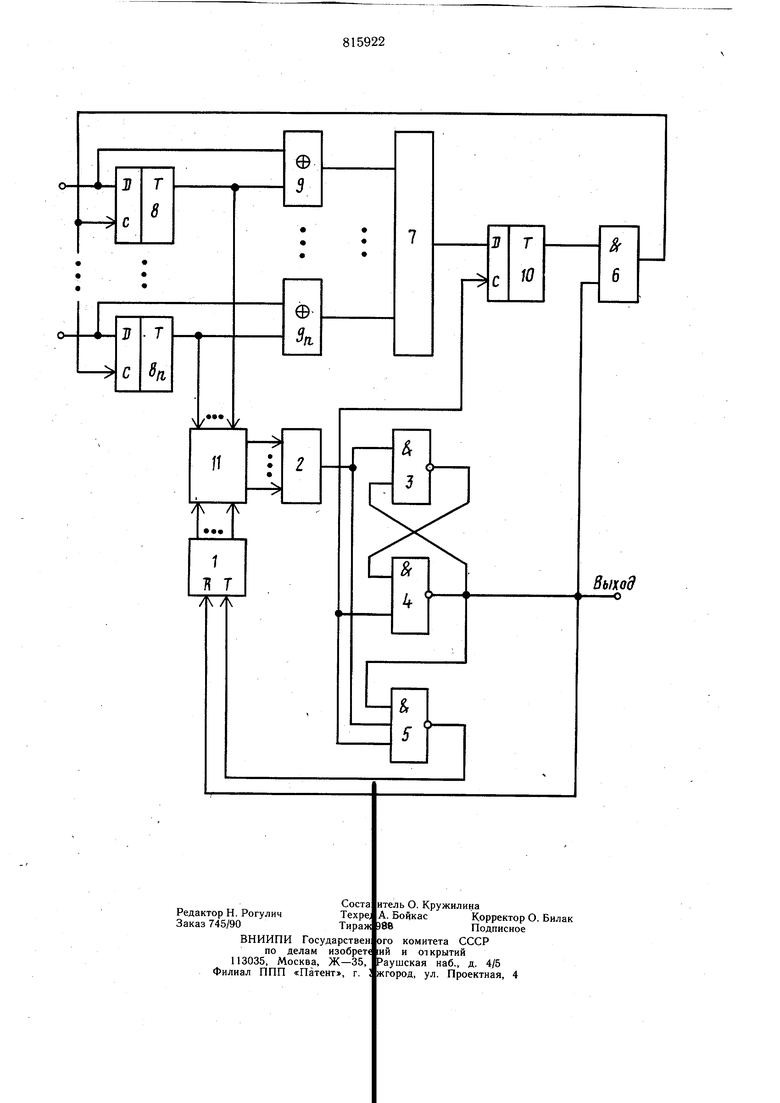

Поставленная цель достигается тем, что, в управляемый делитель частоты следования импульсов, содержащий счетчик импульсов, дещифратор, элементы И-НЕ, первый вход первого из которых соединен с выходом второго элемента И-НЕ, первым входом третьего элемента И-НЕ и входом установки в нуль счетчика импульсов, второй вход - со вторым входом третьего элемента И-НЕ и выходом дешифратора, третий вход - с входной шиной и первым входом второго элемента И-НЕ, второй вход которого подключен к выходу третьего элемента И-НЕ, а выход - с тактовым входом счетчика импульсов, введены коммутатор, элемент ИЛИ, параллельный регистр памяти на Dтриггерах, сумматоры, по модулю два, дополнительный D-триггер, дополнительный элемент И-НЕ, первый вход которого соединен с выходом дополнительного D-триггера, второй вход - с входом установки в нуль счетчика импульсов, разрядные выходы которого соединены с управляюшими входами коммутатора, информационные входы которого соединены с выходами соответствуюш,их D-триггеров параллельного регистра, С-входы которых подключены к выходу дополнительного элемента И-НЕ, D-входы - к первым входам, а выходы - ко вторым входам соответствующих сумматоров по модулю два, выходЬ1 которых соединены с соответствующими входами элемента ИЛИ, выход которого соединен с D-входом дополнительного D-триггера, С-вход которого подключен к входной шине, а выходы коммутатора - к соответствуюшим входам дешифратора. На чертеже изображена структурная электрическая схема устройства. Оно содержит счетчик 1 импульсов, дешифратор 2, элементы 3 - 6 И-НЕ, элемент 7 ИЛИ, D-триггеры 8, ..., 8п параллельного регистра памяти, сумматоры 9, ..., 9п по модулю два, D-триггер 10 дополнительный, коммутатор 11. Устройство работает следующим образом. На коммутатор 11 поступают сигналы с разрядов счетчика 1, и с выходов D-триггеров 8, ..., 8п. На каком-либо i-том выходе коммутатора 11 сигнал равен «1, если нд соответствующем i-том управляющем входе сигнал равен сигналу на i-том информационном. Если сигналы на управляющем и информационном входе отличаются друг от друга, то сигнал на выходе равен «О. Таким образом, на вход дещифратора 2 при совпадении состояния счетчика 1 с кодом, установленным на D-триггерах 8, ..., 8п, поступают с выхода коммутатора п «Ь. Дешифратор выдает сигнал «О на элементы 5 и 3 и на их выходах появляются «Ь. Тактовые (входные) импульсы перестают проходить на вход счетчика 1 через элемент 5. Следующий тактовый импульс проходит на выход элемента 4 и обнуляет счетчик 1. Сигнал на выходе дещифратора 2 становится равным «1 и после окончания импульса на выходе элемента 3 устанавливается «О, который удерживает на выходе элемента 5 «1, из-за чего все следующие импульсы проходят через элемент 5 на тактовый вход счетчика 1 до появления имульса на выходе дещифратора 2, после чего цикл повторяется. На входах D-триггеров 8, ,.., 8п изменяется один или несколько сигналов, т. е. изменяется коэффициент деления. При этом состояние D-входа одного или нескольких D-триггеров 8, ..., 8п отличается от состояния их выхода, что вызовет появление сигнала «1 на соответствующих выходах сумматоров 99п, выполняющих операцию «сумма по модулю Действительно ,XzVXiXi, где Z функция «сумма по модулю Xi - первая переменная; Хг - вторая переменная. Положив, что У| Q (jQ-выход триггера) Х D fD-вход триггера) получим, что при Xi Хг о или 1 при Xi 4 X2(Xi Хг) - Z 1. Этот сигнал поступает на вход D-триггеР через элемент 7 и по ближайшему положительному фронту тактового сигнала на С-вход D-триггера 8, на выходе D-триггера 8 устанавливается сигнал «1 и следующий импульс обнуления с элемента 4 проходит через элемент 6 на С-входы D-триггеров 8, ..., 8п и своим задним фронтом (относительно выходного сигнала) устанавливает их в положение, соответствующее новому значению управляющего сигнала. После этого сигналы на входах и выходах -триггеров 8, ..., 8п станут одинаковыми и схема приходит в исходное состояние, но с новым коэффициентом деления. Положительный эффект от использования предлагаемого устройства заключен в повышении надежности. Импульс, по заднему фронту которого происходит запись нового кода в параллельный регистр, что соответствует установке нового коэффициента деления, приходит принципиально после смены кода, так как он появляется после того, как сумматоры 9, ..., 9п обнаружат смену кода. Сигнал на выходе элемента 7 появляется одновременно с тактовым сигналом, т. е. смена кода происходит раньще появления тактового сигнала на время, равное сумме задержек в элементе 7 и в сумматорах 9, ..., 9п. В этом случае сигналы на D-БХОД и С-вход D-триггера 10 приходят одновременно, но сбоя не происходит. Если D-триггер 10 сработает, то все происходит как обычно, т. е. ближайшим импульсом обнуления происходит смена кода. Если D-триггер 10 не сработает, то он сработает на следующем такте, но когда тактовый импульс, перекрывающийся со сменой кода является и обнуляющим триггер 10 не успевает срабатывать, устройство отработает еще один цикл со старым коэффициентом деления (т. е. произвольного коэффициента деления не будет). При построении различных систем автоматического управления автоподстройки

частоты, надежность функциональных узлов, входящих в систему слежения или подстройки, играет первостепенную роль, поскольку от этого зависит точность слежения или подстройки т. е. качество системы в целом, иногда бывает трудно сделать измеритель, выдающий сигнал синхронно с тактовой частотой системы управления. Тогда надо либо выдавать аналоговую информацию, либо передавать информацию синхронно с. внутренним генератором измерителя, а в системе принимать меры, делающие ее нечувствительной к возможным сопротивлениям фронтов импульсов, приводящих к состязанию логических элементов. Передача аналоговых сигналов нежелательна. Это уменьшает помехоустойчивость системы. Изобретение исключает состязание элементов относительно простым путем, кроме того, такая схема работает с любым кодом, необходимо только, чтобы информация о коэффициенте деления передавалась тем же кодом, в котором работает счетчик импульсов, и чтобы счетчик имел вход начальной установки (не обязательно нулевой). Это всегда легко выполняется.

Формула изобретения

Управляемый делитель частоты следования импульсов, содержащий счетчик импульсов, дешифратор, элементы И-НЕ, первый вход первого из которых соединен с выходом второго элемента И-НЕ, первым входом третьего элемента И-НЕ и входом установки в нуль счетчика импульсов, второй вход -

со вторым входом третьего элемента И-НЕ и выходом дешифратора, третий вход - с входной шиной и первым входом второго элемента И-НЕ, второй вход которого подключен к выходу третьего элемента И-НЕ,

а выход - с тактовым входом счетчика импульсов, отличающийся тем, что, с целью повышения надежности, в него введены коммутатор, элeмeнt ИЛИ, параллельный регистр памяти на D-триггерах, сумматоры по модулю два, дополнительный D-триггер,

0 дополнительный элемент И-НЕ, первый вход которого соединен с выходом дополнительного D-трнггера, второй вход - с входом установки в нуль счетчики импульсов, разрядные выходы которого соединены с

j управляющими входами коммутатора, информационные входы которого соединены с выходами соответствующих D-трнггеров параллельного регистра, С-входы которых подключены к выходу дополнительного элемента И-НЕ, D-входы - к первым входам,

0 а выходы - ко вторым входам соответствующих сумматоров по. модулю два, выходы которых соединены с соответствующими входами элемента ИЛИ, выход которого соединен с D-входом дополнительного Dтриггера, С-вход которого подключен к входной шине, а выходы коммутатора - к соответствующим входам дешифратора.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР

0 № 502503, кл. Н 03 К 23/00, 04.07.74. 2. Авторское свидетельство СССР № 517164, кл. Н 03 К 23/24, 03.01.75.

Авторы

Даты

1981-03-23—Публикация

1979-04-16—Подача