(54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ СИСТЕМ ПЕРЕДАЧИ ИНФОРМАЦИИ

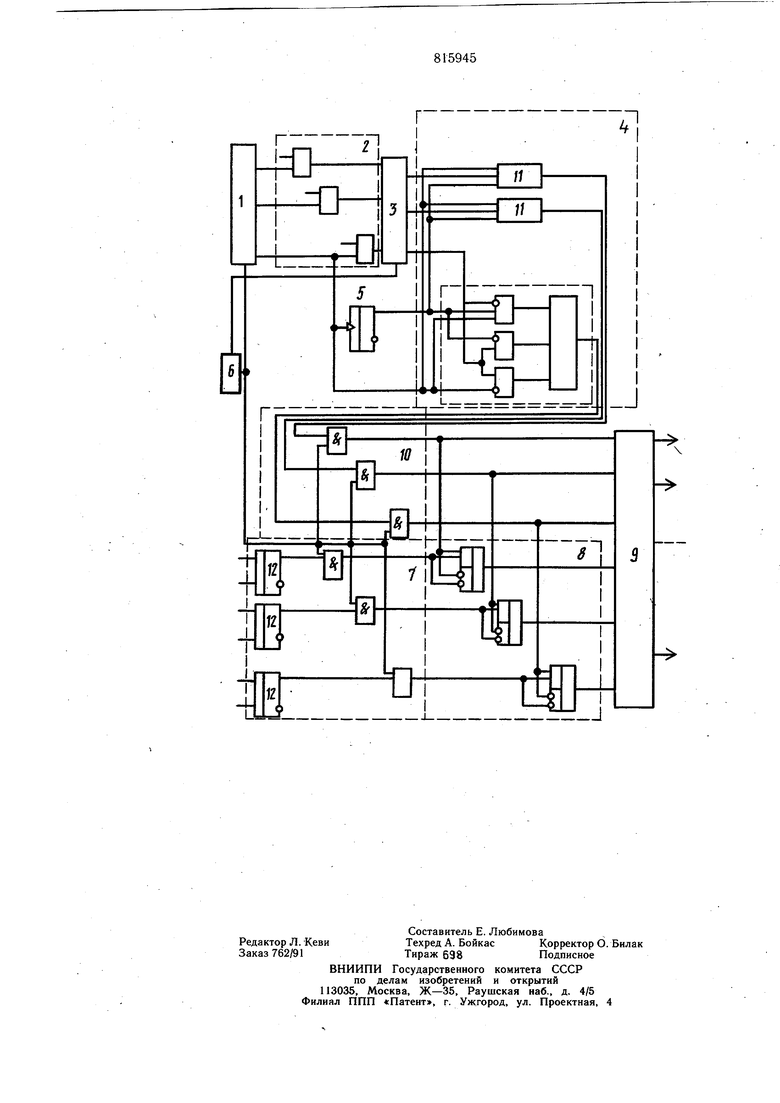

триггеров 12 формирователя 7. Эталонные сигналы периодически меняются. Коммутирующий сигнал ,N-ro канала поступает на вход триггера 5 и на запараллельные первые входы fi логических схем 11 блока 4, вторые входы которых подключены к соответствующим выходам преобразователя 3, а третьи запараллельные входы связаны с выходом триггера 5.

Разрядные сигналы п-значного двоичного сигнала, отображающего величину выборки входного сигнала, подаются на первые входы элементов И блокаЮ, на вторые входы которых поступает синхронизирующий импульс в конце каждого канального интервала. Эти импульсы поступают также на вторые входы элементов И формирователя 7. Блок 8 выдает сигнал единица при . совпадении качества входных сигналов. В остальных случаях он выдает сигнал ноль. В регистр 9 записывается 2 п-значный двоичный сигнал. На его четных ячейках записываются элементы информационных слов, а на нечетных элементы слов, образованных поразрядным перемножением элементов эталонного и информационного сигналов. Нечетные элементы сигналов содержат сведения об элементах эталона и об элементах информационных слов.

Таким образом, передавая по каналу связи вместо п-значных двоичных информационных сигналов 2п-значиые сигналы, п-элементов которых повторяют исходный сигнал, а остальные п-элементов являются результатом операции поразрядного преобразования исходного сигнала и эталонного сигнала, обладающего острой функцией корреляции, на приемной стороне иа элементах равнозначности выделяют сигналы синхронизации, сигналы символьной синхронизации, повышают точность кадровой синхронизации, восстанавливают информационные сигналы и отбраковывают 2 п-значные слова при возникновении ошибок нечетной кратности.

Формула изобретения

Устройство для синхронизации систем передачи информации, содержащее последовательно соединенные распределитель импульсов, блок ключей, преобразователь аналог-цифра и блок коммутации, второй вход которого через триггер соединен с одним из выходов распределителя импульсов и

третьим входом блока коммутации, и синхро низатор, подключенный к входам синхронизации распределителя импульсов и преобразователя аналог-цифра, отличающееся тем, что, с целью повыщения точности синхронизации, введены последовательно соединенные формирователь опорного сигнала, блок определения рассогласования сигналов и регистр, другие входы которого соединены с другими входами блока определения рассогласования сигналов и выходами блока

элементов И, первые входы которого соединены с выходами блока коммутации, а вторые входы с входами формирователя опорного сигнала, при этом выход синхронизатора подключен к вторым входам блока элементов И и входам формирователя опорного сцг-

нала.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 462299, кл. Н 04 L 7/04, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая система связи с исправле-НиЕМ ОшибОК | 1979 |

|

SU818024A1 |

| Устройство передачи информации с защитой от ошибок | 1984 |

|

SU1188893A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Многоканальное устройство для сбора данных | 1983 |

|

SU1095163A1 |

| Устройство для передачи информации с контролем ошибок высокой кратности | 1987 |

|

SU1480129A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Фазометр мгновенных значений | 1981 |

|

SU980015A1 |

Авторы

Даты

1981-03-23—Публикация

1979-01-04—Подача