(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Устройство для умножения | 1988 |

|

SU1615706A1 |

| Устройство для умножения | 1989 |

|

SU1672441A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Множительно-сдвиговое устройство | 1978 |

|

SU805307A1 |

| Устройство для умножения | 1989 |

|

SU1612295A1 |

| Устройство для умножения двоичныхчиСЕл B дОпОлНиТЕльНыХ КОдАХ | 1979 |

|

SU813420A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Устройство для умножения | 1981 |

|

SU1012245A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

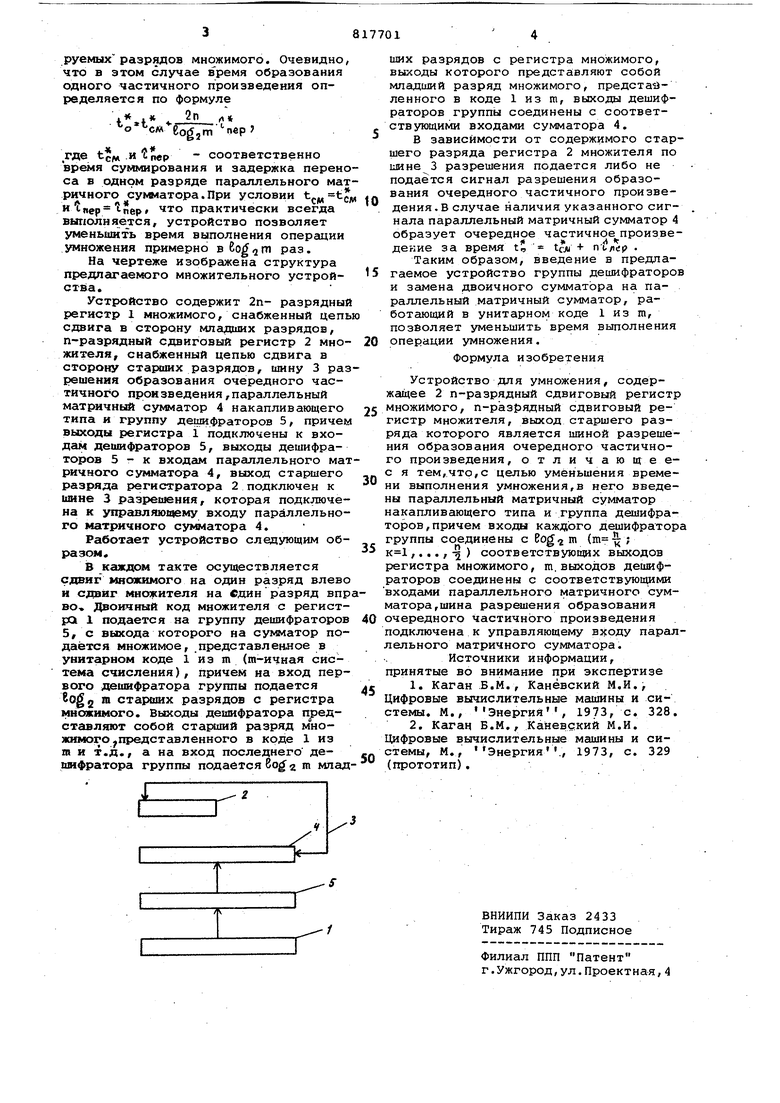

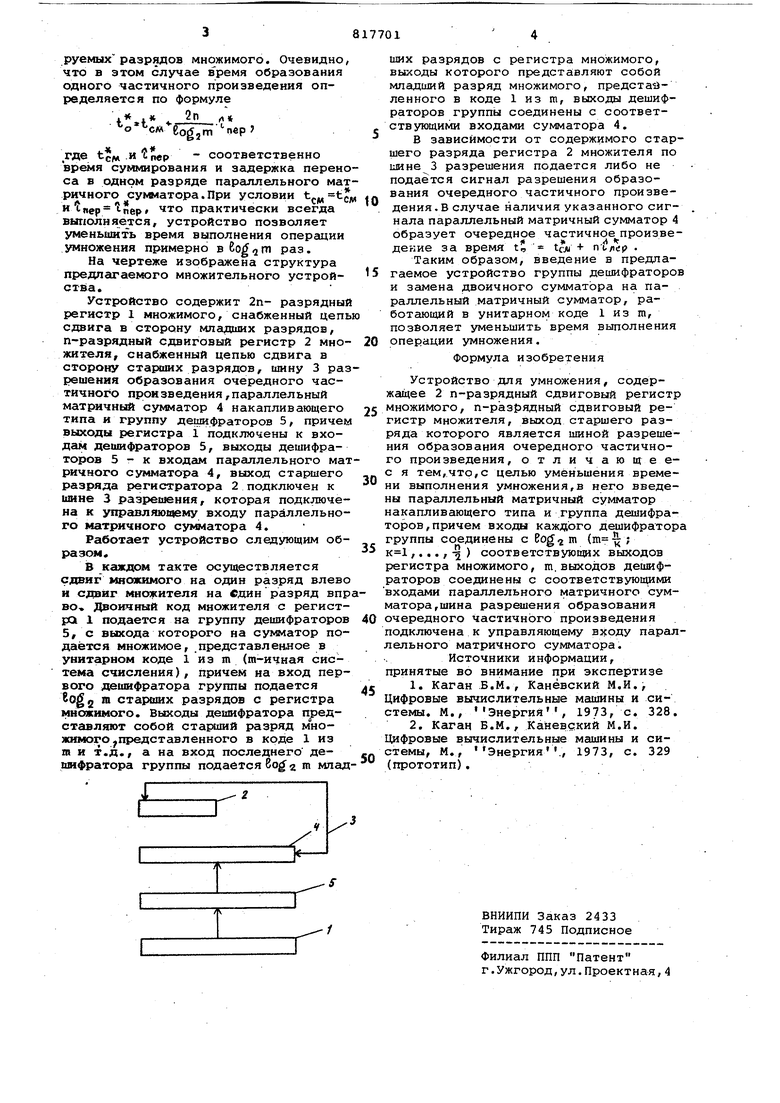

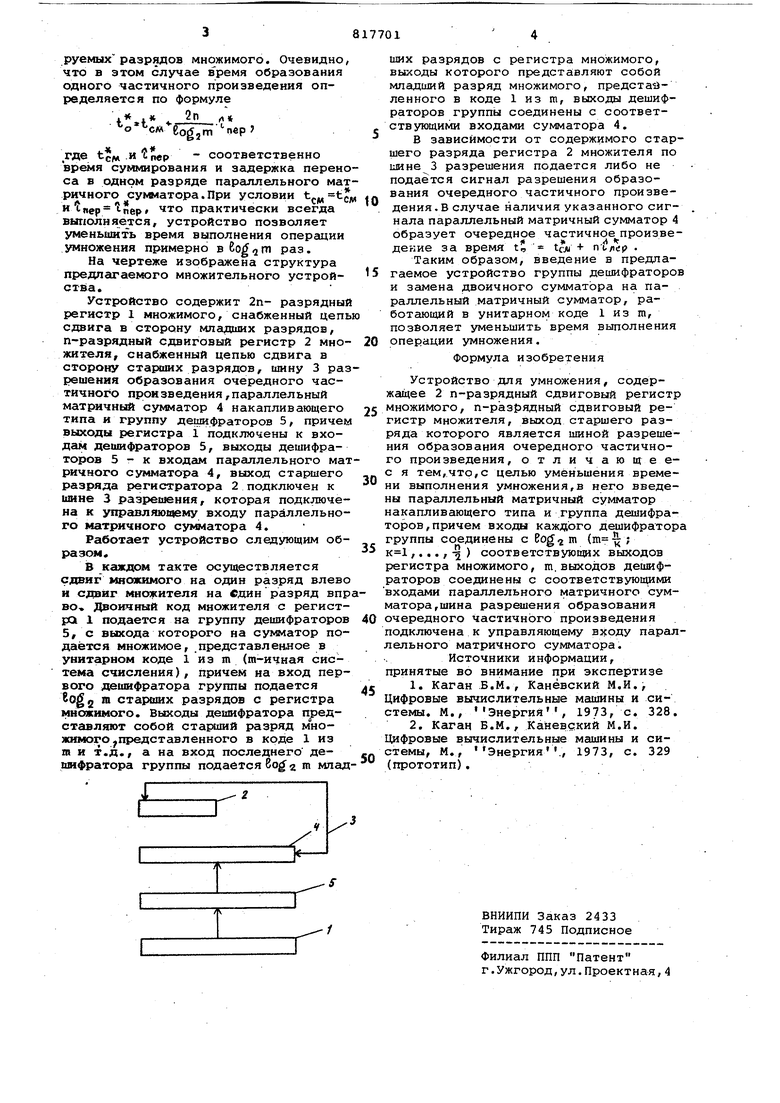

Изобретение относится к вычиСлитальной технике и может быть использовано в арифметико-логических устройствах специализированных ЦАМ. Известны множительные устройства, содержащие регистры множимого и множителя и сумматор частичных преягзведений, снабженные цепями сдвига 1. Однако данные устройства обладают низким быстродействием. Наиболее близким к предлагаемому является устройство, содержащее 2празрядный регистр множимого, снабженный цепью сдвига в сторону младших разрядов, п-разрядный регистр множителя, снабженный цепью сдвига в сторону старших разрядов, шину разрешения образования очередного частичного произведения, 2п-разрядный двоичный сумматор 2. Недостатком данного устройства является низкое быстродействие, обусловленное быстродействием двоичного сумматора, которое при отсутствии средств ускорения переноса определяется по формуле-to -ом 2п пер где to - общее время суммирова - время суммирования в одном разряде; задержка переноса в одном разряде. Цель изобретения - уменьшение времени выполнения умножения. Поставленная цель достигается тем, что в устройство для умножения, содержащее 2п-разрядный сдвиговый регистр множимого, п-разрядный сдвиговый регистр множителя, выход старшего разряда которого является шиной разрешения образования очередного частичного произведения, введены параллельный матричный сумматор накапливающего типа и группа дешифраторов, причем входы каждого дешифратора группы соединены cEogjm m 2 , ksX,,..,- , 1Где к - число единиц в коде множите(ЛЯ) соответствующих выходов регистра множимого, m выходов дешифраторов соединены с соответствующими входами параллельного матричного сумматора, шина разрешения образования очередного произведения подключена к ,управляюпэму входу параллельного ма тричного сумматора. : Введение указанных элементов позволяет осуществлять образование частичнш: произведений в Kojfe 1 из т, где cog ; п - группа дешифрируемыхразрядов множимого. Очевидно что в этом случае время образования одного частичного произведения определяется по формуле , .« 2п где t .и - соответственно время суммирования и задержка перено са в одном разряде параллельного мат ричного сукматора.При условии t,.|, tg и , что практически всегда выполняется, устройство позволяет уменьшить время выполнения операции умножения примерно раз. На чертеже изображена структура предлагаемого множительного устройства. Устройство содержит 2п- разрядный регистр 1 множимого, снабженный цепь сдвига в сторону младших разрядов, п-разрядный сдвиговый регистр 2 множителя, снабженный цепью сдвига в сторону старших разрядов, шину 3 раз решения образования очередного частичного произведения,параллельный матричный сумматор 4 накапливающего типа и группу дешифраторов 5, причем выходы регистра 1 подключены к входам дешифраторов 5, выходы дешифраторов 5 - к входам параллельного мат ричного сумматора 4, выход старшего разряда регистратора 2 подключен к шине 3 разреиюния, которая подключена к управляющему входу парйллельного матричного сумматора 4. Работает устройство следующим образом. В каждом такте осуществляется сдвиг множимого на один разряд влево и сдвиг множителя на един разряд впр во. Двоичный код множителя с регистра 1 подается на группу дешифраторов 5, с выхода которого на сумматор подаётся множимое, представленное в унитарном коде 1из m (m-ичная система счисления), причем на вход первого дешифратора группы подается Ogg m старших разрядов с регистра множимого. Выходы дешифратора представляют собой стаЕ«1Шй разряд множимого представленного в коде 1 из m и т.д., а на вход последнего дешифратора группы подается Bog г m млад ших разрядов с регистра множимого, выходы которого представляют собой младший разряд множимого, представленного в коде 1 из т, выходы дешифраторов группы соединены с соответствующими входами сумматора 4. В зависимости от содержимого старшего разряда регистра 2 множителя по шине 3 разрешения подается либо не подается сигнал разрешения образования очередного частичного произведения. В случае наличия указанного сигнала параллельный матричный сумматор 4 образует очередное частичное произведег;ие за время t + пияер Таким образом, введение в предлагаемое устройство группы дешифраторов и замена двоичного сумматора на параллельный матричный сумматор, работающий в унитарном коде 1 из го, позволяет уменьшить время выполнения операции умножения. Формула изобретения Устройство для умножения, содержащее 2 п-разрядный сдвиговый регистр множимого, п-разрядный сдвиговый регистр множителя, выход старшего разряда которого является шиной разрешения образования очередного частичного произведения, отличаю щеес я тем,что,с целью уменьшения времени выполнения умножения,в него введены параллельный матричный сумматор накапливающего типа и группа дешифраторов, причем входы каждого дешифратора группы соединены с Bog i ,..., -5 ) соответствующих выходов регистра множимого, т.выходов дешифраторов соединены с соответств5ющими входами параллельного матричного сумматора,шина разрешения образования очередного частичного произведения подключена к управляющему входу паралельного матричного сумматора. Источники информации, принятые во внимание при экспертизе 1.Каган .Б.М., Каневский М.И., Цифровые вычислительные машины и системы. М., Энергия, 1973, с. 328. 2.Каган Б.М., Каневс.кий М.И. Цифровые вычислительные машины и системы, М., Энергия., 1973, с. 329 (прототип).

Авторы

Даты

1981-03-30—Публикация

1979-02-08—Подача