i

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах цифровых вычислительных машин и систем.

Известно устройство для умножения двоичных чисел в дополнительных кодах, содержащее регистр множителя, дешифратор, регистр множимого, сумматор, регистр результата, группу схем И 1.

Недостаток этого устройства заключается в недостаточном быстродействии, связанном с потерями времени на распространение переносов при каждом суммировании очередного частичного произведения с текущим кратным множимого.

Известно также устройство для умножения двоичных чисел, содержащее регистр множимого, регистр множителя, регистр результата (п -f 1) сумматоров, поразрядные элементы И-ИЛИ 2.

Недостатком этого устройства является недостаточное быстродействие, связанное с потерями времени на проведение переносов в каждом из сумматоров, э также большой объем оборудования.

Из известных устройств для умножения двоичных чисел, представленных в дополнительных кодах, наиболее близким к предлагаемому является устройство, содержащее регистр множимого, сдвиговый регистр множителя, трехвходовой сумматор, регистр поразрядных сумм, регистр поразрядных переносов, преобразователь цифр множителя, триггер запоминания результата преобразования, три группы элементов И, группу элементов ИЛИ, узел задержки, причем выходы двух младщих разрядов сдвигового регистра множителя соединены с первым и вторым входами дещифратора цифр множителя, первый выход дещифратора соединен со входами всех элементов И первой группы, второй выход дешифратора соединен со входом узла задержки, первый выход узла задержки соединен со входами всех элементов И второй группы и с управляющими входами регистров множителя, поразрядных сумм и поразрядных переносов, а второй выход -

с входом младшего разряда-сумматора, третий выход дешифратора соединен со входами всех элементов И третьей группы, а четвертый выход через триггер запоминания результата дешифратора соединен с третьим

входом преобразователя, вторые входы элементов И первой группы соединены с прямыми выходами соответствующих разрядов регистра множимого, вторые входы элементов И второй группы соединены с инверсными выходами соответствующих разрядов регистра множимого, вторые входы элементов И третьей группы соединены со сдвигом влево на один разряд с прямыми выходами соответствующих разрядов регистра множимого, выходы элемента И первой, второй и третьей группы соединены со входами соответствующих элементов ИЛИ, выходы элементов ИЛИ соединены с соответствующими разрядами первого входа сумматора, первый выход сумматора соединен со входом регистра поразрядных, сумм, второй выход сумматора соединен со входом регистра поразрядных переносов, выходы регистров поразрядных сумм и поразрядных переносов соединены со вторым и с третьим входами сумматора соответственно 3.

Недостатком данного устройства является недостаточное быстродействие. Это связано с необходимостью двух циклов суммирования при передаче, инверсного кода множимого.

В первом цикле на первый вход сумматора подается обратный код множимого с одновременной блокировкой сдвига множителя, суммы и переносов, а во втором цикле - единица, отличающая дополнительный код отрицательного числа от обратного.

Цель изобретения - увеличение быстродействия устройства.

Для достижения поставленной цели в устройство для умножения двоичных чисел в дополнительных кодах, содержащее регистр множимого, сдвиговый регистр множителя, трехвходовой сумматор, регистр поразрядных сумм, регистр поразрядных переносов, дешифратор цифр множителя, триггер запоминания результата дешифрации, три группы элементов И, группу элементов ИЛИ, причем выходы двух младших разрядов сдвигового регистра множителя соединергы с первым и вторым входами дешифратора цифр множителя, первый и второй выходы которого соединены с первыми входами элементов И первой и второй групп соответственно, третий выход дешифратора цифр множителя через триггер запоминания результата дешифрации соединен с третьим входом дешифратора цифр множителя, вторые входы элементов И первой группы соединены с прямыми выходами соответствующих разрядов регистра множимого, первые входы элементов И третьей группы соединены с инверсными выходами соответствующих разрядов множимого, вторые входы элементов И второй группы соединены со сдвигом влево на один разряд с прямыми выходами разрядов регистра множимого, выходы элементов И первой, второй и третьей групп

соединены со входами соответствующих элементов ИЛИ группы, выходы которых соединены со входами соответствующих разрядов первого входа сумматора, первый и второй выходы сумматора, соединены со входами

регистра поразрядных сумм и регистра поразрядных переносов соответственно, выходы которых соединены соответственно со вторьГм и третьим входами сумматора, введены триггер запоминания единицы дополнительного кода, триггер запоминания переноса и дополнительный сумматор, причем установочный вход триггера запоминания единицы дополнительного кода и вторые входы элементов И третьей группы соединены с четвертым выходом дещифратора цифр

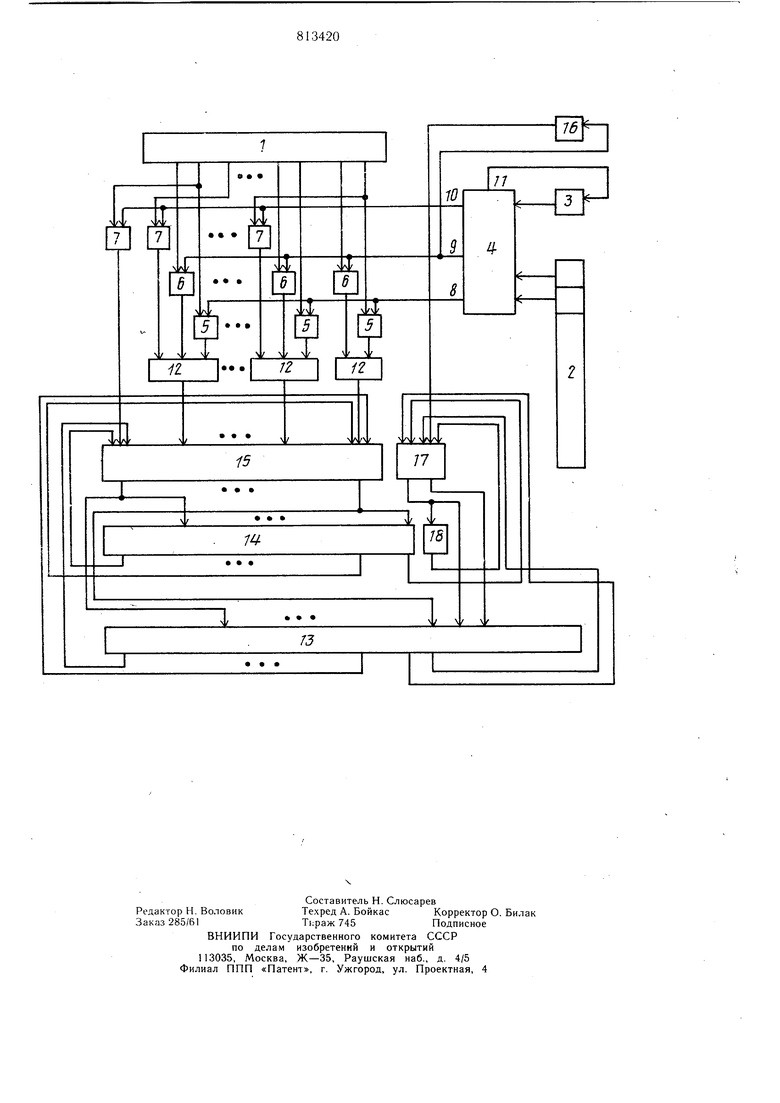

множителя, выход триггера запоминания единицы дополнительного кода соединен с младшим разрядом первого входа дополнительного сумматора, выход младшего разряда регистра поразрядных переносов соединен со старшим разрядом первого входа дополнительного сумматора, выход младшего разряда регистра поразрядных переносов соединен со старшим разрядом первого входа дополнительного сумматора, разряды второго входа дополнительного сумматора соединены с выходами дополнительных разрядов регистра поразрядных сумм, входы которых соединены с выходами разрядов дополнительного сумматора, выход переноса дополнительного сумматора через триггер запоминания переноса соединен с третьим входом дополнительного сумматора. На чертеже представлена схема устройства для умножения двоичных чисел.

Устройство содержит п-разрядный регистр 1 множимого, сдвиговый п-разрядный регистр 2 множителя, триггер 3 запоминания результата преобразования цифр множителя, дешифратор 4 цифр множителя, группу элементов И 5 прямой передачи кода множимого, группу элементов И 6 инверсной передачи кода множимого, группу элементов И 7 передачи кода множимого со сдвигом влево, выход 8, выход 9, выход 10 и выход 11 дещифратора 4 цифр множителя, группу элементов ИЛИ 12, 2п-разрядный регистр 13 поразрядных сумм, (л -f 2)разрядный регистр И запоминания переносов, (п + 1)-разрядный основной сумматор 15, триггер 16 запоминания единицы дополнительного кода, дополнительный двухразрядный сумматор 17, триггер 18 запомина0 ния переноса.

Перед выполнением умножения в регистре 1 хранится множимое, представленное в дополнительном коде, а в регистре 2 - представленный в дополнительном коде множитель. В первом такте умножения

в дешифраторе 4 одновременно анализируются два младших разряда множителя и значение выхода триггера 3, которое в исходном состоянии устройства всегда равно нулю. При единичном значении первого разряда множителя и нулевом значении второго разряда множителя, а также при единичном значении выхода триггера 3 и нулевом значении первого и второго разрядов множителя в дешифраторе 4 управляющий импульс формируется на первом выходе. При единичном значении первого и второго разрядов множителя и нулевом значении выхода триггера 3, а также при единичном значении выхода триггера 3 и второго разряда множителя и нулевом значении первого разряда множителя в дешифраторе 4 управляюший импульс формируется одновременно на выходах 9 и 11. При этом на выходе 11 управляюший импульс формируется также и при единичном значении триггера 3 и обоих младших разрядов множителя, причем данный импульс поступает на единичный вход триггера 3 и переводит его к началу следуюшего такта в единичное состояние. При единичном значении второго разряда множителя и нулевом значении первого разряда множителя и триггера 3, а также при единичном значении первого разряда множителя и триггера 3 и нулевом значении второго разряда множителя управляюший импульс в дешифраторе 4 формируется на выходе 10. По импульсу, формируемому на выходе 8 дешифратора 4, разрешается срабатывание элементов И 5 и, соответственно, прохождение на вход сумматора 15 пря.мого значения множимого, по импульсу на выходе 9 дешифратора 4 разрешается срабатывание элементов И 6 и прохождение на вход сумматора 15 инверсного значения множимого, а по импульсу на выходе 10 разрешается срабатывание элементов И и прохождение на вход сумматора 15 значения множимого со сдвигом на один разряд влево. Если ни на одном из первых выходов 8-10 дешифратора 4 управляюший импульс не формируется, то на вход сумматора 15 значение множимого не поступает, что соответствует передаче на вход сумматора нулевого значения кода. Управляющий импульс, формируемый на выходе 9 дешифратора 4, поступает на единичный вход триггера 16 и переводит его к началу следующего такта в единичное состояние. При этом запись единицы в триггере 16 соответствует запоминанию единицы, отличающей дополнительный код подлежащего передаче в сумматор 15 отрицательного значения множимого от обратного кода. В сумматоре 15 производится поразрядное суммирование преобразованного множимого и содержимого регистров 13 и 14, поступающего на второй и третий входы сумматора соответственно.

В результате суммирования на выходе сумматора 15 в каждом разряде формируется соответствующее значение суммы и соответствующее значение переноса. Далее поразрядные значения поразрядных переносов записываются в регистр 14 со сдвигом на

один разряд вправо, а значения поразрядных сумм - в регистр 13 со сдвигом на два разряда вправо. При этом значения поразрядных сумм и переносов появляются на выходе указанных регистров к началу следующего такта умножения. В конце первого такта умножения в регистре 2 производится сдвиг множителя на два разряда вправо, в результате чего к началу второго такта на выходе двух младших разрядов регистра 2 появляются соответственно третий и

nUI-,

четвертый разряды множителя. Во втором такте умножения цикл формирования частичного произведения повторяется. Если в первом такте управляющий импульс формировался на выходе 9 дешифратора 4, т. е.

5 в сумматор 15 передавалась инверсная форма множимого, то во втором такте на выходе триггера 16 появляется единица, которая поступает на вход младшего разряда двухразрядного сумматора 17, с выхода старшего разряда которого значение переноса пос0 тупает на вход триггера 18. Поразрядные суммы с выхода сумматора 17 поступают на входы соответствующих разрядов регистра 13, расположенные правее от разрядов, в которые записывается значение с сумматора 15, и к началу следующего такта записываются в эти разряды. Причем предыдущие значения указанных разрядов и разрядов регистра 13, расположенных правее, сдвигаются к началу следуюшего такта на два разряда вправо (в одном из вариантов

0 конкретного выполнения устройства эти разряды .могут сдвигаться в регистр множителя). Далее в следуюших тактах умножения все повторяется аналогично рассмотренным выше тактам, а сумматор 17 работает также, как и сумматор 15, обрабатывая информацию, поступающую с выхода регистров 13 и 14 и триггеров 16 и 18. По окончанию сдвига всех разрядов множителя в регистре 13 формируется сум.ма всех частичных произведений, в которой необходимо только

0 прибавить значение, полученное к этому моменту на выходе регистра 14. Поэтому в последнем такте умножения значения этих регистров суммируются в сумматоре 15 с выполнением сквозного переноса по всем разрядам сумматора и с анализом знаковых

5 разрядов сомножителей, в результате чего в регистре 13 формируется окончательное значение произведения.

Данное техническое решение позволяет Q исключить второй цикл суммирования (суммирование содержимого регистров суммы и переносов с единицей дополнительного кода). Любое из двух возможных значений каждого разряда множителя равновероятно. Поэтому вероятность подачи множимого на вход сумматора инверсным кодом равна 1/4. Увеличение быстродействия устройства зависит от разности множителя. В среднем данное техническое решение повышает быстродействие на 30-35% по сравнению с устройством-прототипом. Формула изобретения Устройство для умножения двоичных чисел в дополнительных кодах, содержащее регистр множимого, сдвиговый регистр множителя, трехвходовой сумматор, регистр поразрядных сумм, регистр поразрядных переносов, дешифратор цифр множителя, триггер запоминания результата дешифрации, три группы элементов И, группу элементов ИЛИ, причем выходы двух младших разрядов сдвигового регистра множителя соединены с первым и вторым входами дешифратора цифр множителя, первый и второй выходы которого соединены с первыми входами элементов И первой и второй групп соответственно, третий выход дешифратора цифр множителя через триггер запоминания результата дешифрации соединен с третьим входом дешифратора цифр множителя, вторые входы элементов И первой группы соединены с прямыми выходами соответствуюших разрядов регистра множимого, первые входы элементов И третьей группы соединены с инверсными выходами соответствующих разрядов регистра множимого, вторые входы элементов И второй группы соединены со сдвигом влево на один разряд с прямыми выходами разрядов регистра множимого, выходы элементов И первой, второй и третьей групп соединены со входами соответствующих элементов ИЛИ группы, выходы которых соединены со входами соответствующих разрядов первого входа сумматора, первый и второй выходы сумматора соединены со входами регистра поразрядных сумм и регистра поразрядных переносов соответственно, выходы которых соединены соответственно со вторым и третьим входами сумматора, отличающееся тем, что, с целью увеличения быстродействия, в устройство введены триггер запоминания единицы дополнительного кода, триггер запоминания переноса и дополнительный сумматор, причем установочный вход триггера запоминания единицы дополнительного кода и вторые входы элементов И третьей группы соединены с четвертым выходом дещифратора цифр множителя, выход триггера запоминания единицы дополнительного кода соединен с младшим разрядом первого входа дополнительного сумматора, выход младшего разряда регистра поразрядных переносов соединен со старшим разрядом первого входа дополнительного сумматора, выход младшего разряда поразрядных переносов соединен со старшим разрядом первого входа дополнительного сумматора, разряды второго входа дополнительного сумматора соединены с выходами дополнительных разрядов регистра поразрядных Сумм, входы которых соединены с выходами разрядов дополнительного сумматора, выход переноса дополнительного сумматора через триггер запоминания переноса соединен с третьим входом- дополнительного сумматора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР Л-Ь 487386, кл. G 06 F 7/39, 1975. 2.Авторское свидетельство СССР № 556434, кл. G 06 F 7/39, 1977. 3.Папернов А. А. Логические основы ЦВТ. М., «(Советское радио, 1972, с. 210- 213, 219-223.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двоичных чисел в дополнительных кодах | 1983 |

|

SU1119008A1 |

| Устройство для ускоренного умножения | 1977 |

|

SU714395A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1348836A1 |

| Устройство для умножения | 1980 |

|

SU960805A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1972 |

|

SU357561A1 |

| Устройство для умножения | 1975 |

|

SU555401A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для умножения @ -разрядных чисел | 1984 |

|

SU1256018A1 |

Авторы

Даты

1981-03-15—Публикация

1979-02-13—Подача