(54) УСТРОЙСТВО ЦИФЮАНАЛОГОВОГО ПРЕОБРАЗОВАНИЯ С КОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательныйАНАлОгО-цифРОВОй пРЕОбРАзОВАТЕль | 1978 |

|

SU819952A1 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1102033A1 |

| Способ аналого-цифрового преобразования с контролем выходного кода и аналого-цифровой преобразователь с контролем выходного кода | 1985 |

|

SU1292180A1 |

| Цифро-аналоговый преобразователь | 1980 |

|

SU949800A1 |

| Устройство для контроля сопротивления | 1987 |

|

SU1596273A1 |

| Реверсивный аналого-цифровой преобразователь | 1986 |

|

SU1361710A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU1117835A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Устройство для измерения гистерезиса @ характеристик | 1985 |

|

SU1247797A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

I

Изобретение относится к импульсной технике, в частности к области цифроаналогового преобразования, и предназначено для применения в системах связи управляющих вычислительных комплексов с объектами управления, для которых требуется повышенная достоверность выдачи аналоговых управляющих воздействий.

Известно устройство цифроаналогового преобразования, содержащее преобразователь кодток, буферный регистр, кодовые входы которого соединены с выходами сдвигающего регистра 11.

Недостатком этого устройства является то, что в нем ие осуществляется автоматический контроль правильности его функционирования.

Известно устройство цифроаналогового преобразования с контролем, содержащее преобразователь код-ток, соединенный входами с выходами первого регистра, первый вход которого соединен с первым выходом блока управления и с входом элемента задержки, соединенного выходом с первым входом первого элемента И, выход которого соединен со входом блока

управления и второй его вход - с выходом компаратора, соединенного первым входом с общей шИной, усилитель с первым резистором в цепи отрицательной обратной связи, .эталонный цифроаналоговый преобразователь, входами подсоединенный к выходам второго регистра и выходом через второй резистор к выходу преобразователя код-ток и к инвертирующему входу усилителя, неинвертирующий вход и выход которого соединены соответственно с общей шиной и со вторым входом компаратора (21.

Недостатком этого устройства является низкая надежность, так как для контроля преобразователя код-ток используется дополнительный сложный прецизионный цифроаналоговый преобразователь, который должен формировать эталодшые уровни для всех значений кодов, записьтаемых в основной преобразователь.

Цель изобретения - повьпиение надежности устройства цифроаналогового преобразования с контролем.

Поставленная цель достигается тем, что в устройство цифроаналогового преобразования

с контролем, содержащее преобразователь код-ток, соединенный входами с выходами первого регистра, первый вход которого соединен с первым выходом блока управления и со входом элемента задержки, соединенного выходом с первым входом первого элемента И, выход которого соединен со входом блока управления и второй его вход - с выходом компаратора, соединенного первым входом с общей шиной, усилитель с первым резистором в цепи отрицательной обратной связи, второй регистр и второй резистор, введены источник эталонного напряжения, первый, второй, третий и четвертый ключи, триггер / логический И1шертор, второй и третий элементы И, элемент ИЛИ и конденсатор, причем выход преобразователя код-ток соединен с сигнальными входами первого и второго ключей, соединенных выходами соответственно с инвертирующими и неинвертирующими входами усилителя, последний из которых через второй резистор соединен с выходами третьего и четвертого ключей, соединенных сигнальными входами соответственно с выходом источника эталонногонапряжения и с общей шиной, управляющие входы первого и четвертого ключей соединены с нулевым выходом триггера, единичный выход которого соединен с управляющими входами второго и третьего ключей, счетный вход триггера соединен со вторым выходом блока управления, третий выход которого соединен со входом гашения триггера и с первым входом второго элемента И, соединенного вторым входом с входной шиной и выходом - с первым входом элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, соединенного первым и вторым входами соответственно с четвертым выходом блока управления и с выходом логического инвертора, вход которого соединен с первым выходом второго регистра, соединенного вторыми выходами со вторыми входами первого регистра и первым и вторым входами - соответственно с выходом элемента ИЛИ и с пятым выходом блока управления, а конденсатор подсоединен между выходом усилителя и вторым входом компаратора.

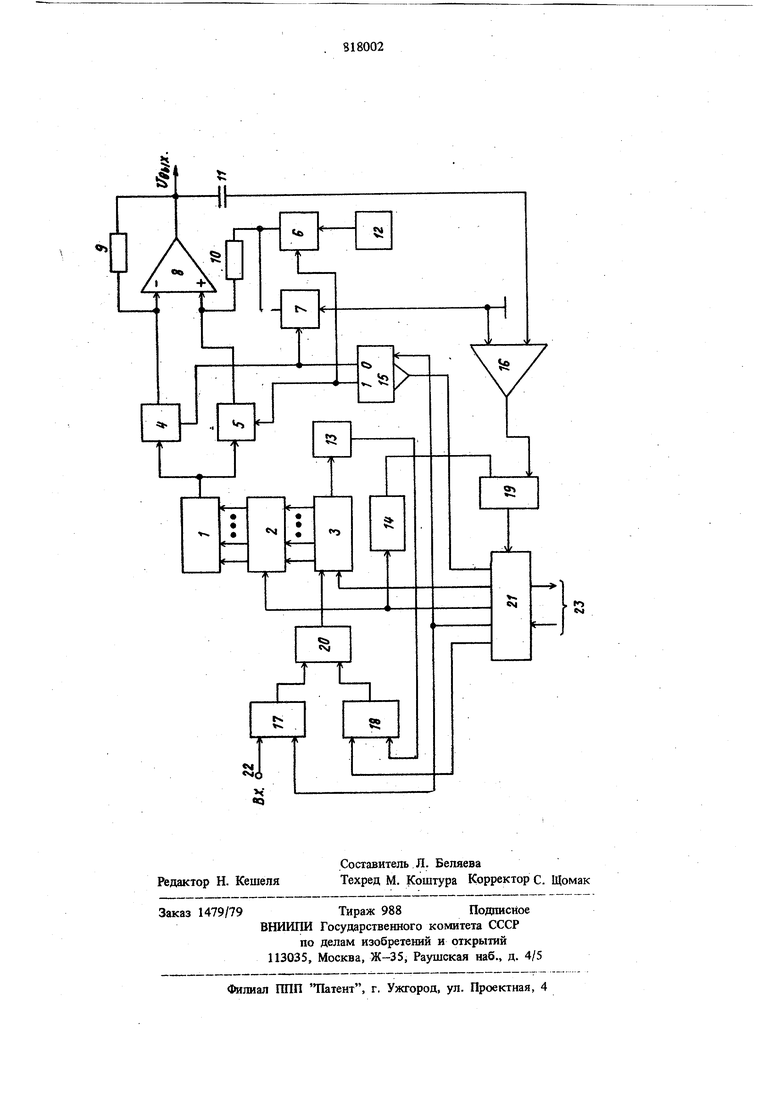

На чертеже представлена структурная схема устройства цифроаналогового преобразования с контролем.

Устройств1О содержит преобразователь 1 кодток, первый и второй регистры 2 и 3, первый, , третий и четвертый ключи - 4- 7, усилитель 8, первый и второй резисторы 9 и 10, конденсатор 11, источник 12 эталонного напряжения, логический инвертор 13, элемент 14 задержки, триггер 15, компаратор 16, первый, второй и третий элементь) И 17-19, элемент 20 ИЛИ, блок 21 управления,

входную шину .22, шины связи с процессором 23.

Устройство работает следующим образом.

Последовательный код, подлежащий преобразованию поступает из процессора управляющего комплекса по входной щине 22 на второй вход элемента 17. Блок 21 формирует на пятом выходе импульсы сдаига, на третьем выходе разрешающий сигнал приема кода и устанавливает триггер 15 в нулевое состояние. В результате этого код записывается в регистр 3, который является сдвигающим, и далее по сигналу, формируемому на первом выходе блока 21, записьгаается в регистр 2. Аналоговый сигнал тока с выхода пробразователя 1 через ключ 4 поступает на инвертирующий вход усилителя 8, на выходе которого образуется аналоговый сигнал напряжения У Bbix- При этом резистор 10 подключен к общей шине с помощью ключа 7, управляемого, как и ключ 4, сигналом с Нулевого выхода триггера 15. После записи кода в регистр 2 блок 21 начинает выполнять режим контроля, который заключается в том, что элемент 17 закрывается по первому входу, по первому входу открывается элемент 18, на второй вход которого поступает сигнал с выхода . регистра 3 через инвертор 13, и вновь формируются сдвигающие импульсы, поступающие на второй вход регистра 3. В результате этого в регистре 3 устанавливается инверсное значение кода по отношению к коду, хранящемуся в регистре 2.

Далее блок 21 снова формирует сигнал на первом выходе для записи кода из регистра 3 в регистр 2 и одновременно устанавливает триггер 15 по счетному входу в единичное состояние. Выход преобразователя 1 подкл(6чается -через ключ 5 к неинвертирующему вхоДу усилителей 8, а резистор 10 с помощью ключа 6 подключается к выходу источника 12, напряжения которого равно максимальному значению (J вых.

При правильном фзгнкционировании устройства после окончания переходньГх процессов, вызвашоис переключением триггера 15 и ключей 4-7, уровень сигнала на выходе усилителя 8 установится прежним, который был до момента этого переклчэчения. Объясняется это тем, что напряжение на инвертирующем входе усилителя 8, которое повторяется на его выходе, в этом случае определяется разностью между выходным напряжением источника 12 и падением напряжения на резисторе 10 от выходного тока преобразователя 1, проходящего через ключ 5. Поскольку этот ток определяется значением инверсного кода, а сопротивления резисторов 9 и 10 выбираются 5. одинаковыми, то напряжение U, вых остается таким же, каким оно было до инверсии кода. Сигнал записи кода в регастр 2, задержанный элементом 4 на время переходного процесса на выходе усилителя 8, используется в качестве стробирующего импульса для элемента 19. Поскольку измене1Ше уровня сигнала на выходе усилителя 8 к моменту стробирующего импульса отсутствует, то и компаратор 16 не изменяет своего выходного сигнала, т.е. импульс с выхода элемента 14 не проходит че рез элемент 19. Затем с помощью блока 21 в регистре 3 устанавливается прямое значение преобразуемого кода, который одновременно с переключением триггера 15 в нулевое состояние записывается в регастр 2, резистор 10 вновь подклю чается к общей ши}1е, а выход преобразователя 1 подсоединяется через ключ 4 к инверти. рующему входу усилителя 8 и тд. Таким образом, при правильном функционировании устройства в блок 21 не поступает импульс через элемент 19. При каком-либо нарушеши работы устройст ва, приводящем к изменению уровня выходного напряжения усилителя 8 на величину, превы щающую значение порога срабатывания компар тора 16, открывается элемент 19, через кото-рый стробирующий импульс с выхода элемента 14 проходит в блок 21, и формируется сигнал неисправности устройства преобразовани Введенные элементы и новые взаимосвязи позволяют в процессе работы предлагаемого устройства производить контроль правильности его функционирования для всех преобразуемых кодов только по одному эталонному уровню, т.е. не требуется эталонный Нифроаналоговый преобразователь, представляющий собой сложный прецизионный узел. Следовательно, надежность устройства цифро аналогового преобразования с контролем повы щается. Этот положительный эффект будет еще более существенным при использовании в многоканальной системе выдачи аналоговых сигналов, так как источник эталонного напряжения может быть общим для всех каналов. Формула изобретения Устройство цифроаналогового преобразования с контролем, содержащее преобразователь кодток, соединенный входами с выходами первого регистра, первый вход которого соединен с первым выходом блока управления и со входом элемента задержки, соединенного выходом с первым входом первого элемента И, выход которого соединен со входом блока управления и второй его вход - с выходом компаратора, соеданенного первым входом с общей пшной, усилитель с первым резистором в цепи отрицательной обратной связи, второй регистр и вто,рой резистор, отличающееся тем, что, с целью повышения надежности, в него введены источник эталонного напряжения, первый, второй, третий и четвертый ключи, триггер, логический инвертор, второй и третий элементы И, элемент ИЛИ и конденсатор, причем выход преобразователя код-ток соещгнен с сигнальными входами первого и второго ключей, соединенных выходами соответственно с инвертирующим и неинвергирующим входами усилителя, последний из которых через второй резистор соединен с выходами третьего и четвертого ключей, соединенных сигнальными входами соответственно с выходом источника эталонного напряжения и с общей щиной, управляюцдае входы первого и четвертого ключей соединены с нулевым выходом триггера, единичный выход которого соединен с управляющими входами второго и третьего ключей, счетный вход триггера соединен со вторым выходом блока управления, третий выход которого соединен со входом гащения триггера и с первым входом второго элементаИ, соединенноговторым входом с входной щиной и выходом - с первым входом элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, соединенного первым и вторым входами соответственно с четвертым выходом блока управления и с выходом логического инвертора, вход которого соединен с первым выходом второго регистра, соединенного вторыми выходами со вторыми входами первого регистра и первым и вторым входами - соответственно с выходом элемента ИЛИ и с пятым выходом блока управления, а конденсатор подсоединен между выходом усилителя и вторым входом компаратора. Источники информации, принятые во внимание при экспертизе 1. Conversion Products Сс1 аесх; л«(яЕо{ evices, inc., igij, р.Ъ7. 2 flhaec «r-dli jitaE conversiO tioinol . -by D.H.3iiein«5oedl, Anaeoif Devices, I ИС., 1972, p. (ПРОТОТИП).

Авторы

Даты

1981-03-30—Публикация

1978-08-03—Подача