(54) ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ АНАЛОГОЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения в код | 1977 |

|

SU705671A1 |

| Устройство цифро-аналогового преобра-зОВАНия C КОНТРОлЕМ | 1978 |

|

SU818002A1 |

| Функциональный преобразователь | 1983 |

|

SU1166147A1 |

| Параллельно-последовательный аналого- цифровой преобразователь | 1978 |

|

SU790287A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU630743A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU938396A1 |

| Устройство сигнатурной проверки аналого-цифровых преобразователей | 1979 |

|

SU790293A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1640818A1 |

| Устройство для автоматизированного контроля параметров реле | 1985 |

|

SU1265704A1 |

| Емкостно-электронный преобразователь перемещения | 1989 |

|

SU1721434A1 |

1

Изобретение относится к импульсной технике, в частности к преобразователям аналоговых сигналов в цифровые с повышенным быстродействием, и предназначено для построения на его основе систем сбора аналоговой информации для управляющих вычислительных комплексов.

Известен преобразователь, содержащий блок сравнения, состоящий из аналоговых компараторов с триггерами-защелками на выходах, каждый из которых, кроме старшего, имеет на выходе элемент несовпадения, при этом первые входы всех компараторов соединены с первым выходом аналогового переключателя и с выходом аналогового ключа, второй вход каждого аналогового компаратора соединен с соответствующим выходом формирователя эталонных уровней, общий стробирующий вход триггеровзащелок соединен с первым выходом блока управления, выход каждого триггера защелки, кроме старщего, соединен с прямым входом соответствующего элемента несовпадения, инверсный вход которого соединен с выходом соседнего старщего триггера-защелки, выход старщего триггера-защелки и выходы всех элементов несовпадения соединены с входами шифратора, выходы которого соединены с первыми входами регистра, вторым и третьим входами соединенного соответственно с вторым и третьим выходами блока управления, четвертый и пятый выходы которого соединены с управляющими входами соответственно аналогового ключа и аналогового переключателя, сигнальный вход аналогового ключа соединен с выходом вычитателя, соединенного входом суммирования с вторым выходом аналогового переключателя, сигнальный вход которого соединен с входной щиной, а также цифроаналоговый преобразователь, входами соединенный с выходами регистра и выходомс входом вычитания вычитателя 1.

Этот преобразователь обладает сравнительно невысоким быстродействием из-за формирования сигнала обратной связи с помощью цифроаналогового преобразователя, выходной сигнал которого, начинает изменяться только после записи в регистр кода первого такта преобразования.

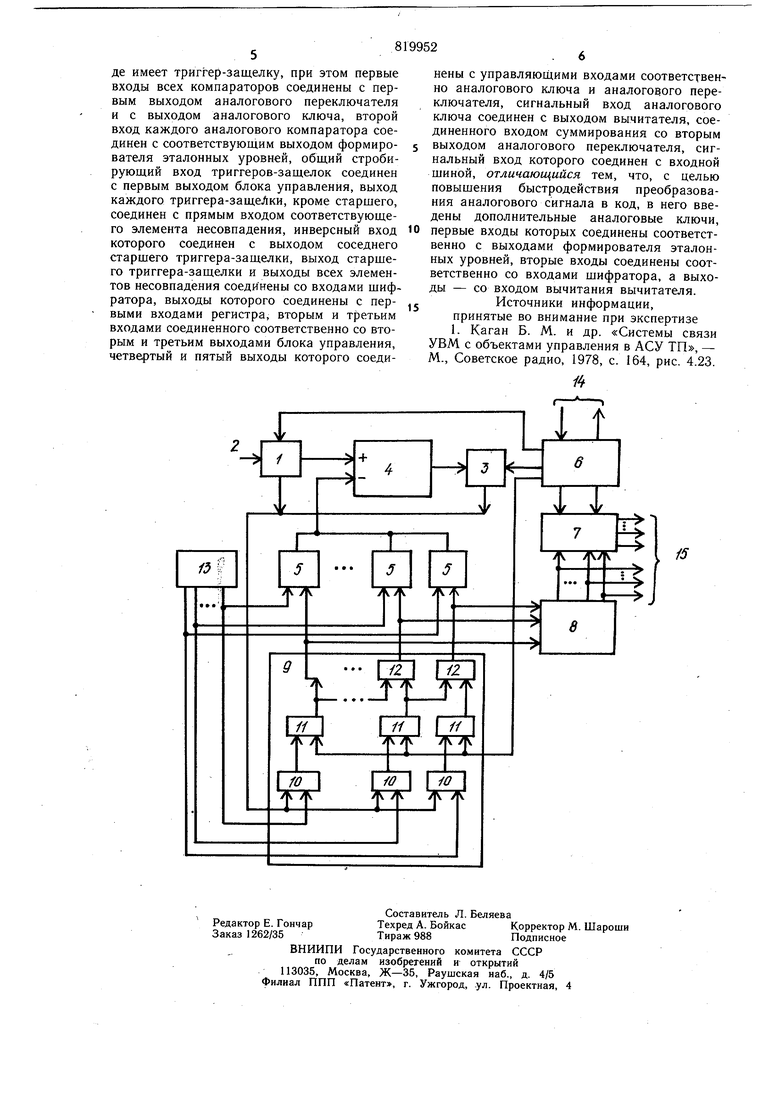

Целью изобретения является повыщение быстродействия преобразования аналогового сигнала в код. Достигается это тем, что в параллельнопоследовательный аналого-цифровой преобразователь, содержащий блок сравнения, состоящий из аналоговых компараторов, каждый из которых на выходе имеет триггер-защелку, при этом первые входы всех компараторов соединены с первым выходом аналогового переключателя и с выходом аналогового ключа, второй вход каждого аналогового компаратора соединен с соответствующим выходом формирователя эталонных уровней, общий стробирующий вход триггеров-защелок соединен с первым выходом блока управления, выход каждого триггера-защелки, кроме старщего, соединен с прямым входом соответствующего элемента несовпадения, инверсный вход которого соединен с выходом соседнего старшего триггера-защелки, выход старщегО Tpjirreра-защелки и выход всех элементов несовпадения соединены с входами щифратора, выходы которого соединены с первыми входами регистра, вторым и третьим входами соединенного соответственно с вторым и третьим выходами блока управления, четвертый и пятый выходы которого соединены с управляющими входами соответственно аналогового ключа и аналогового переключателя, сигнальный вход аналогового ключа соединен с выходом вычитателя, соединенного входом суммирования с вторым выходом аналогового переключателя, сигнальный вход которого соединен с входной щиной, введены дополнительные аналоговые ключи, первые входы которых соединены соответственно с выходами формирователя эталонных уровней, вторые входы соединены соответственно с входами щифратора, а выходы - с входом вычитания вычитателя. На чертеже представлена структурная схема параллельно-последовательного аналого-цифрового преобразователя, содержащего аналоговый переключатель 1, входную щину 2, аналоговый ключ 3, аналоговый вычитатель 4, дополнительные аналоговые ключи 5, блок управления 6, регистр 7, шифратор 8, блок аналогового сравнения 9, содержащий компараторы 10, триггеры-защелки 11 и элементы несовпадения 12, формирователь эталонных уровней 13, шину связи с микропроцессором 14, выходные щины 15. Преобразователь работает следующим образом. Сначала блок 6 формирует сигнал для гашения регистра 7 и одновременно устанавливает такие уровни сигналов, что ключ 3 запирается, аналоговый переключатель 1 устанавливается в такое состояние, когда преобразуемый аналоговый сигнал напряжения постоянного тока с входной шины 2 проходит через этот переключатель, поступая далее на общий вход компараторов 10 блока аналогового сравнения 9. Затем блок 6 формирует стробирующий сигнал, по которому результат сравнения преобразуемого сигнала с уровнями, формируемыми блоком 13 и поступающими на вторые входы компараторов 10, запоминается в триггерах-защелках в виде унитарного кода. Запоминаемый в этих триггерах унитарный код результата сравнения преобразуется в позиционный код на выходах элементов несовпадения 12. Преобразование унитарного кода в позиционный заключается в том, что каждый триггер 11, находящийся в единичном состоянии, запрещает по инверсному входу элемента 12 прохождение через его прямой вход единичного сигнала с выхода соседнего младщего триггера 11. Поэтому сигнал логической единицы будет на выходе только того элемента, который соответствует в данном случае наиболее старщему триггеру 11, находящемуся в единичном состоянии. Сигналы позиционного кода далее преобразуются в двоичный код с помощью щифратора 8 и одновременно подаются на управляющие входы дополнительно введенных аналоговых ключей 5. Один из этих ключей на вход которого поступает сигнал логической единицы, открывается и на вход вычитателя 4 поступает аналоговый сигнал, уровень которого соответствует результату преобразования первого такта. Первый такт преобразования заканчивается записью кода в регистр 7 по сигналу, формируемому блоком 6. Одновременно с этой записью блок 6 изменяет уровни выходных сигналов так, что ключ 3 открывается и переключатель 1 устанавливается в такое состояние, когда преобразуемый сигнал проходит на суммирующий вход вычитателя 4. Затем, после установления сигнала на общем входе компараторов 10, блок 6 вновь формирует сигналы стробирования для триггеров 11. После этого код результата преобразования с выходов блоков 7 и 8 может быть передан в микропроцессор по сигналу, поступающему с щины 14. Расмотренный параллельно-последовательный аналого-цифровой преобразователь выгодно отличается от преобразователя прототипа, так как обладает большим быстродействием. Это объясняется тем, что второй такт преобразования начинается без ожидания записи кода первого такта преобразования в регистр и его преобразования в аналоговый сигнал обратной связи. Кроме того, схема преобразователя проще известного, так как формирование сигнала обратной связи выполняется без использования сложного аналогового узла - цифроаналогового преобразователя. Формула изобретения Параллельно-последовательный аналогоцифровой преобразователь, содержащий блок сравнения, состоящий из аналоговых компар аторов, каждый из которых на выходе имеет триггер-защелку, при этом первые входы всех компараторов соединены с первым выходом аналогового переключателя и с выходом аналогового ключа, второй вход каждого аналогового компаратора соединен с соответствующим выходом формирователя эталонных уровней, общий стробирующий вход триггеров-защелок соединен с первым выходом блока управления, выход каждого триггера-защеЛки, кроме старшего, соединен с прямым входом соответствующего элемента несовпадения, инверсный вход которого соединен с выходом соседнего старщего триггера-защелки, выход старшего триггера-защелки и выходы всех элементов несовпадения соединены со входами шифратора, выходы которого соединены с первыми входами регистра, вторым и третьим входами соединенного соответственно со вторым и третьим выходами блока управления, четвертый и пятый выходы которого соединены с управляющими входами соответственно аналогового ключа и аналогового переключателя, сигнальный вход аналогового ключа соединен с выходом вычитателя, соединенного входом суммирования со вторым выходом аналогового переключателя, сигнальный вход которого соединен с входной шиной, отличающийся тем, что, с целью повышения быстродействия преобразования аналогового сигнала в код, в него введены дополнительные аналоговые ключи, первые входы которых соединены соответственно с выходами формирователя эталонных уровней, вторые входы соединены соответственно со входами шифратора, а выходы - со входом вычитания вычитателя.

Источники информации, принятые во внимание при экспертизе 1. Каган Б. М. и др. «Системы связи УВМ с объектами управления в АСУ ТП, - М., Советское радио, 1978, с. 164, рис. 4.23.

/4

it

Авторы

Даты

1981-04-07—Публикация

1978-12-08—Подача