(54) ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый логический элемент | 1981 |

|

SU1005317A1 |

| Пороговый логический элемент | 1981 |

|

SU1005316A1 |

| Пороговый логический элемент | 1980 |

|

SU974588A1 |

| Пороговый логический элемент | 1980 |

|

SU1023661A2 |

| Пороговый логический элемент | 1987 |

|

SU1492469A1 |

| СПОСОБ ПОЛНОГО СЛОЖЕНИЯ - ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2132566C1 |

| Пороговый логический элемент | 1987 |

|

SU1422401A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Пороговый логический элемент | 1987 |

|

SU1506544A1 |

| Многопороговый логический элемент | 1990 |

|

SU1728966A2 |

Изобретение относится к импульсной технике и может быть использовано в различных устройствах автоматики.

Известно устройство, содержащее последовательно соединенные каскады настройки весрв входного кода, позволяющее определить произвольный порог срабатывания 1.

Недостаток устройства - сложность его и больщие затраты оборудования.

Наиболее близким к предлагаемому является устройство, содержащее блок сложения по модулю два входных сигналов, число которых не превыщает семи, состоящий из сумматоров, входы которых соединены со входами устройства, а выходы переносов с входами выходного сумматора, выход переноса которого является выходом устройства 2.

Однако в этом устройстве ограниченные функциональные возможности.

Цель изобретения - расширение функциональных возможностей, заключающихся в возможности анализа произвольного порогового значения входного кода.

Поставленная цель достигается тем, что в устройство, содержащее блок сложения по модулю два входных сигналов,, состоящий

из сумматоров, введены аналогичные последовательно соединенные блоки сложения по модулю два, входы каждого из которых соединены с выходами переносов сумматоров предыдущего блока сложения по модулю два,

а выход переноса последнего блока сложения по модулю два является выходом устройства.

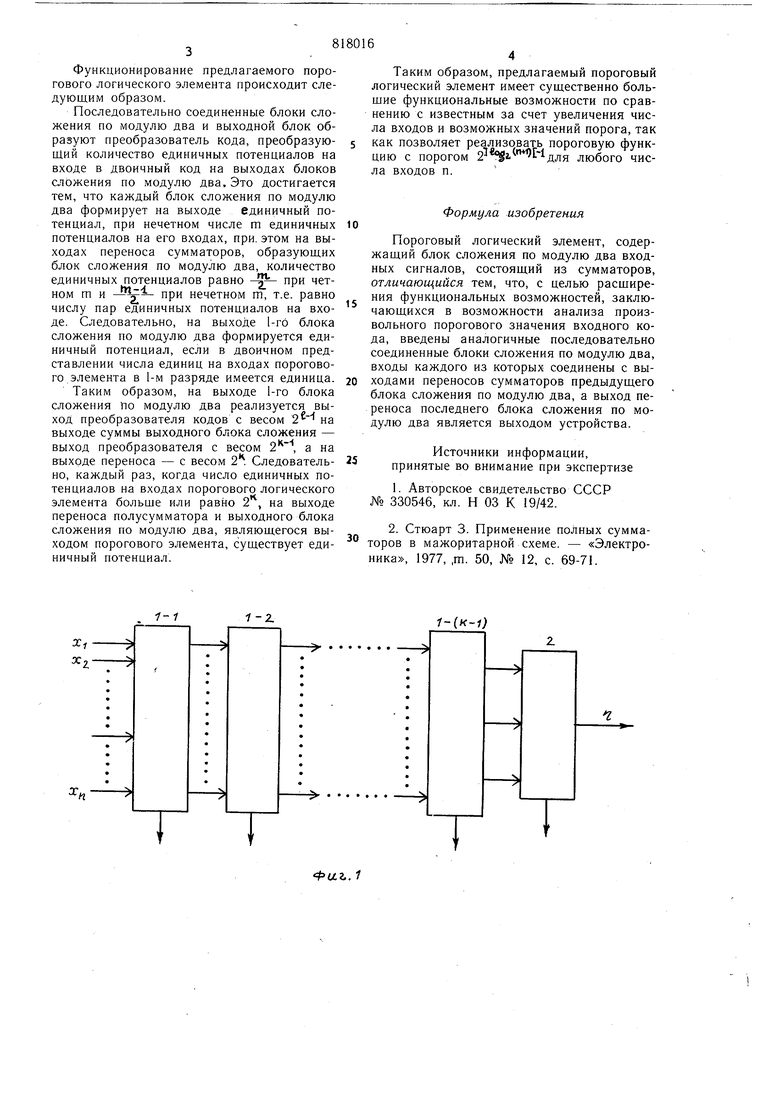

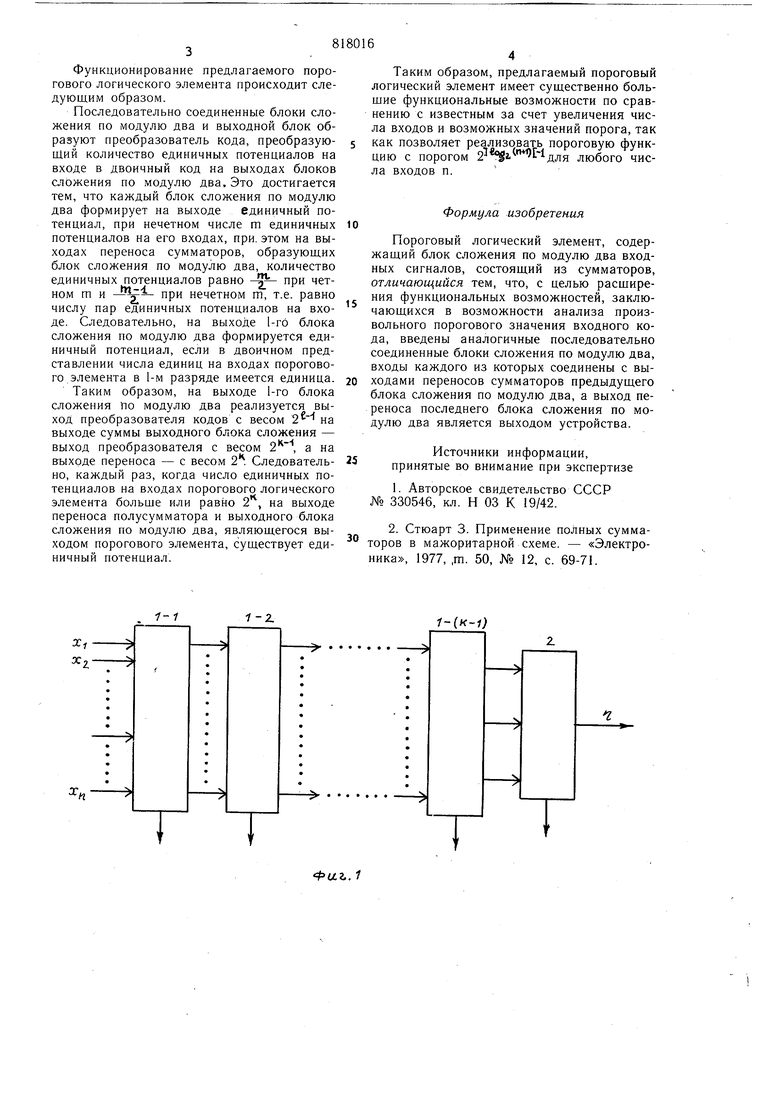

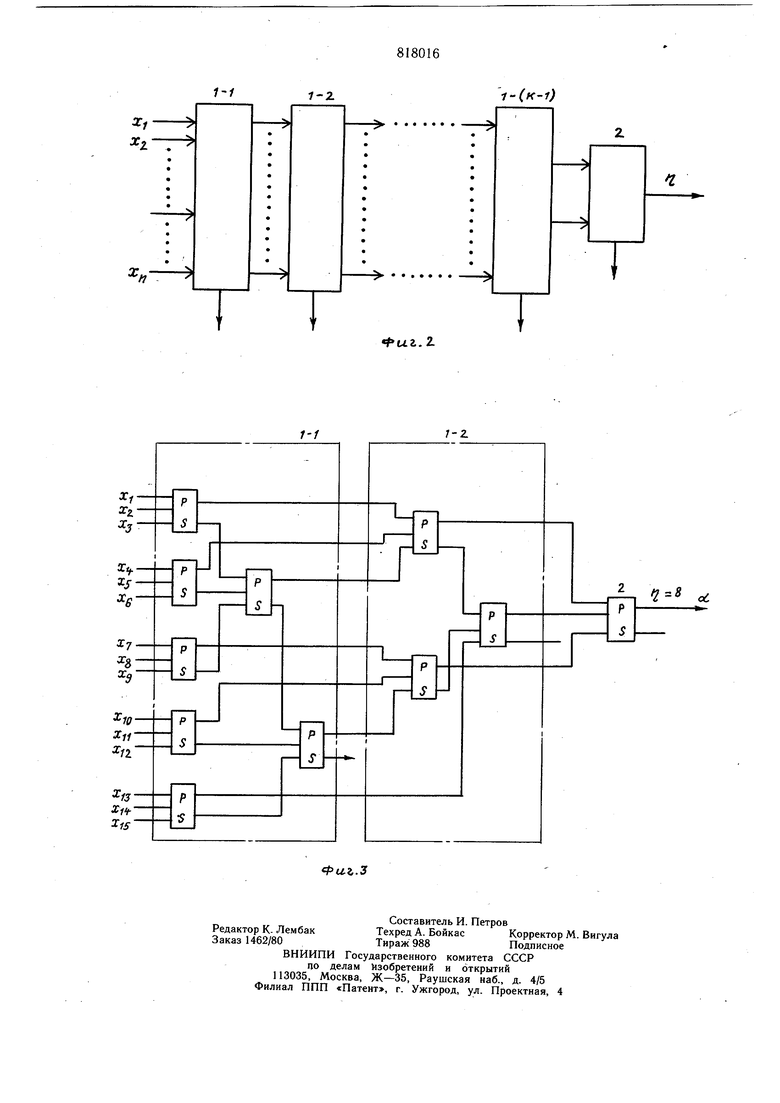

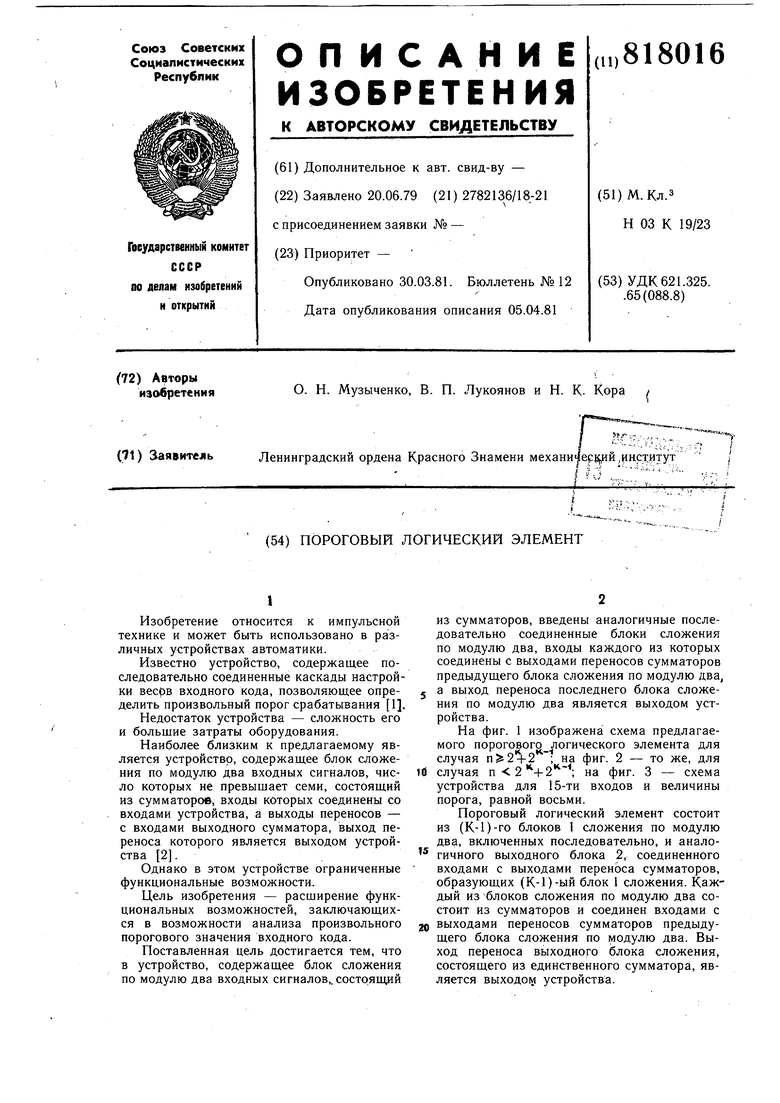

На фиг. 1 изображена схема предлагаемого порогового логического элемента для случая на фиг. 2 - то же, для случая п на фиг. 3 - схема устройства для 15-ти входов и величины порога, равной восьми.

Пороговый логический элемент состоит из (K-l)-ro блоков 1 сложения по модулю два, включенных последовательно, и аналогичного выходного блока 2, соединенного входами с выходами переноса сумматоров, образующих (К-1)-ый блок 1 сложения. Каждый из блоков сложения по модулю два состоит из сумматоров и соединен входами с

выходами переносов сумматоров предыдущего блока сложения по модулю два. Выход переноса выходного блока сложения, состоящего из единственного сумматора, является выходом устройства. Функционирование предлагаемого порогового логического элемента происходит следующим образом. Последовательно соединенные блоки сложения по модулю два и выходной блок образуют преобразователь кода, преобразующий количество единичных потенциалов на входе в двоичный код на выходах блоков сложения по модулю два. Это достигается тем, что каждый блок сложения по модулю два формирует на выходе единичный потенциал, при нечетном числе m единичных потенциалов на его входах, при. этом на выходах переноса сумматоров, образующих блок сложения по модулю два, количество единичных потенциалов равно - при четном m и при нечетном т, т.е. равно числу пар единичных потенциалов на входе. Следовательно, на выходе 1-го блока сложения по модулю два формируется единичный потенциал, если в двоичном представлении числа единиц на входах порогового элемента в 1-м разряде имеется единица. Таким образом, на выходе 1-го блока сложения По модулю два реализуется выход преобразователя кодов с весом 2 на выходе суммы выходного блока сложения - выход преобразователя с весом 2, а на выходе переноса - с весом 2 . Следовательно, каждый раз, когда число единичных потенциалов на входах порогового логического элемента больше или равно 2, на выходе переноса полусумматора и выходного блока сложения по модулю два, являющегося выходом порогового элемента, существует единичный потенциал.

1-1

1-2.

г

Фи.. 1

1-(К-1) Таким образом, предлагаемый пороговый логический элемент имеет существенно больщие функциональные возможности по сравнению с известным за счет увеличения числа входов и возможных значений порога, так как позволяет реализовать пороговую функцию с порогом любого числа входов п. Формула изобретения Пороговый логический элемент, содержащий блок сложения по модулю два входных сигналов, состоящий из сумматоров, отличающийся тем, что, с целью расщирения функциональных возможностей, заключающихся в возможности анализа произвольного порогового значения входного кода, введены аналогичные последовательно соединенные блоки сложения по модулю два, входы каждого из которых соединены с выходами переносов сумматоров предыдущего блока сложения по модулю два, а выход переноса последнего блока сложения по модулю два является выходом устройства. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 330546, кл. Н 03 К 19/42. 2. Стюарт 3. Применение полных сумматоров в мажоритарной схеме. - «Электроника, 1977, ,т. 50, № 12, с. 69-71.

1-11-г

1 1

1-1

1-(к-1)

.г.

J-Z

Авторы

Даты

1981-03-30—Публикация

1979-06-20—Подача