(5) ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый логический элемент | 1980 |

|

SU1023661A2 |

| Пороговый логический элемент | 1987 |

|

SU1492469A1 |

| Пороговый логический элемент | 1987 |

|

SU1422401A1 |

| Пороговый логический элемент | 1979 |

|

SU818016A1 |

| Пороговый логический элемент | 1981 |

|

SU1005317A1 |

| Контролируемый двоично-десятичныйСуММАТОР | 1979 |

|

SU845156A1 |

| Пороговый логический элемент | 1981 |

|

SU1005316A1 |

| Преобразователь двоичного кода в код по модулю К | 1989 |

|

SU1732472A1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ | 1987 |

|

RU2034401C1 |

| Пороговый логический элемент | 1987 |

|

SU1506544A1 |

1

Изобретение OTHOCVITCR к автоматике и вычислительной технике и может быть использовано для построения различных устройств переработки дискретной информации.

Известен пороговый логический элемент, содержащий преобразователи весов на два входа, состоящие из элемента И и элемента ИЛИ с параллельно соединенными входами, блок формирова- д 1НИЯ порога и выходной элемент ИЛИ. Блок формирования порога выполнен двухступенчатым, содержащим два однотипных каскада формирования набора

весов первой ступени, взаимнодополнят з щи$ весовые выходы которых попарно соединены с входами элементов И каскада формирования порога второй ступени 1 J.

Недостатком этого порогового го логического элемента являются ограниченные функциональные возможности.

Известен также пороговый логический элемент, содержащий блоки сложения по модулю два, входы каждого иа которых, кроме первого, соединены с. выходами предыдущего блока сложения по модулю два, входы первого блока сложения по модулю два соединены с входами порогового логического элемента, а каждый блок сложения по модулю два содержит группы сумматоров, входы сумматоров первой группы соединены с входами данного блока сложения по модулю два, входы сумматоров остальных групп соединены с выходами сумм предыдуи ей группы сум-, маторов, выходы переносов сумматоров соединены с выходами данного блока сложения по модулю два, а выход суммы сумматора последней группы сумматоров данного блока сложения по модулю два соединен с вспомогательным выходом данного блока сложения по модулю два f2J.

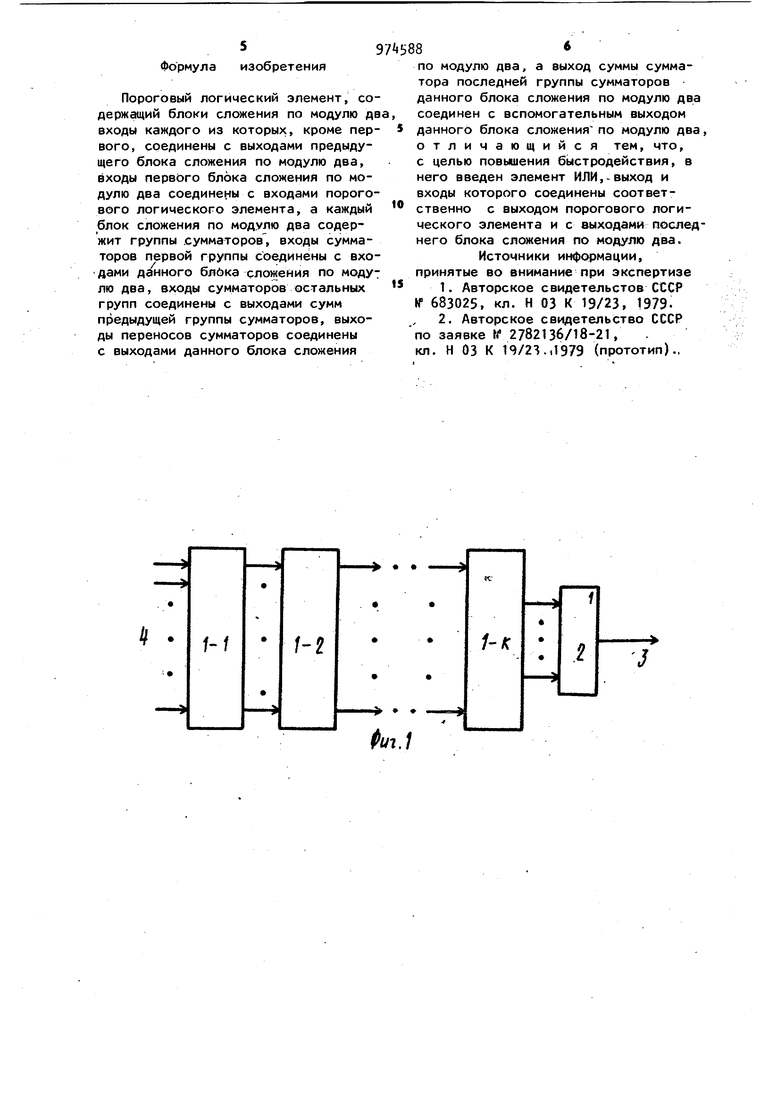

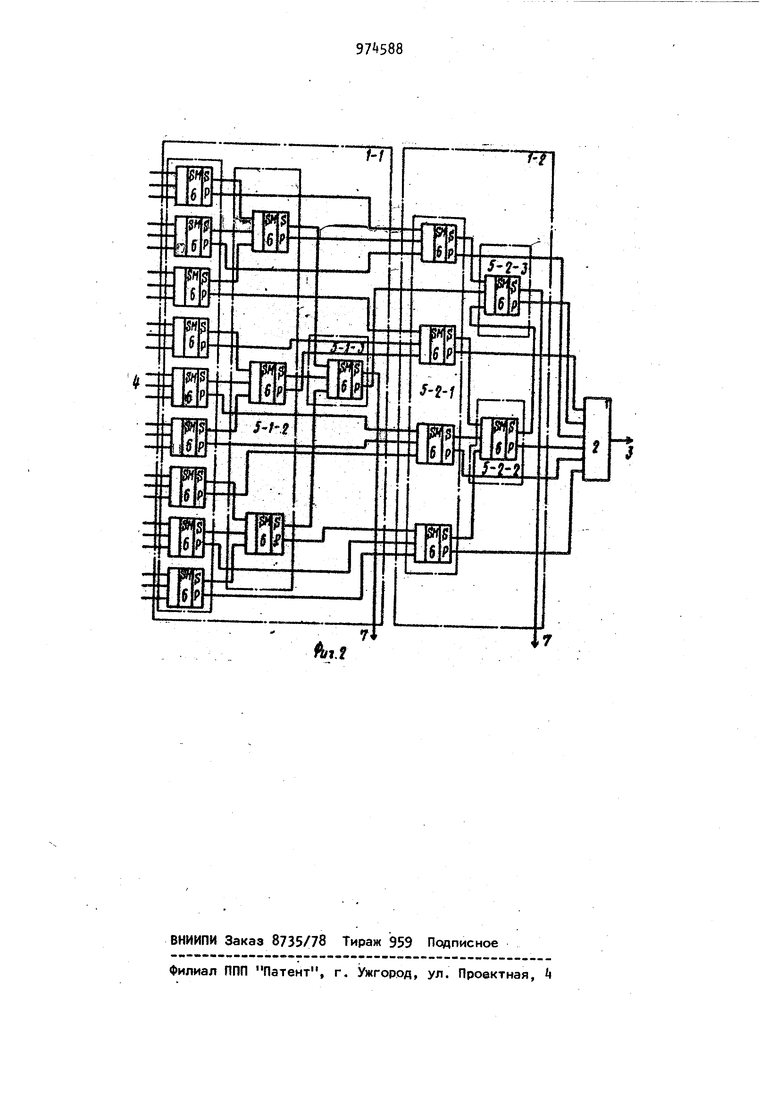

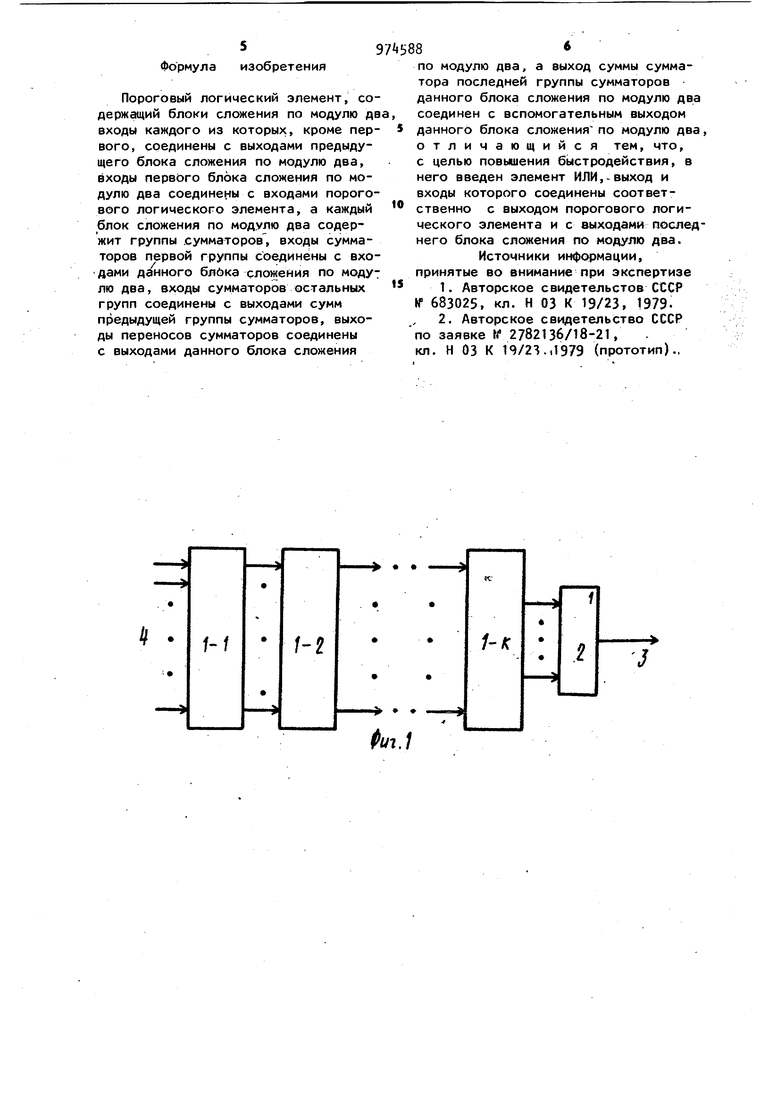

Недостатком этого порогового эле- мента является относительно низкое быстродействие. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем что в пороговый логический элемент, содержащий блоки сложения по модулю два, входы каждого из которых, кро ме первого, соединены с выходами пре дыдущего блока сложения по модулю два, входы первого блока сложения по модулю два соединеныс входами порогового логического элемента, а каждый блок сложения по модулю два iсодержит группы сумматоров,входы сумматоров первой группы соединены с входами данного блока .сложения по модулю два, входы сумматоров остальных групп соединены с выходами предыдущей группы сумматоров, выходы переносов сумматоров сое динены с выходами данного блокаеложения по модулю два, а выход суммы сумматора последней группы сумматоро данного блока сложения по модулю два соединен с вспомогательным выходом данного блока сложения по мо-, дулю два, введен элемент ИЛИ выход и входы которого соединены соответственно с выходом порогового логичес кого элемента и с выходами последне блока сложения по модулю два. На фиг.1 показана cтpyктypJ aя схема порогового логического элемен та; на фиг.2 - пример реа/1изации порогового логического элемента для порога, равного четырем, рассчитанного на двадцать семь входов. Пороговый логический элемент содержит блоки 1-1 - 1-К сложения по модулю два и элемент ИЛИ 2, выход которого соединен с выходом 3 порого вого элемента, а входы элемента ИЛИ 2 соединены с выходами последнего блока 1-К сложения по модулю два. Входы каждого блока сложения по модулю два, кроме первого 1-1, соединены с выходами предыдущего блока сложения по модулю два, входы перво блока 1-1 сло хения по модулю два соединены с входами k порогового ло гического элемента, а каждый t-ый блок сложения по модулю два содержит группы сумматоров 6, вход сумматоров 6 первой группы 5-J-1 со динены с входами данного i ого блок сложения по модулю два, входы сумматоров 6 остальных групп соединены с выходами сумм предыдущей группы сумматоров 6,выходы переносов, сумма торов 6 соединены с выходами данног лока сложения .по модулю два, а выход суммы сумматора 6 последней группы сумматоров 6 данного блока сложения по модулю два соединен с вспомогательным выходом 7 данного блока слоения по модулнэ два, Пороговый логический элемент раотает следующим образом. Каждый блок 1-1 - 1-К сложения по модулю два формирует определенное количество единичных логических си1- налов при нечетном числе ty единичных логических сигналов на его входах, : при этом на выходах переноса сумматоров блока количество единичных логических сигналов равно -JJ2. при четном при нечетном m числу пар единичных логических на входе. Таким образом, на выходах переноса сумматоров 6 блока 1-1 сложения по модулю два число единичных логических сигналов равно -1 где 1 - знак округления в меньшую сторону до ближайшего целого. На выходах переноса сумматоров 6 блока 1-2 сложения по модулю два число единичных логических сигналов равно . Аналогично на выходах переноса сумматоров i-го блока 1-1 сложения г w т по модулю два их число равно - -q-1, а на выходах последнего 1-К--го блока 1 ,где К о.д(а+1)Г-1.Таким образом , всякий раз, когда число единичных логических сигналов на входах порогового логического элемента mi а, т.е. больше или равно порогу, на выходе по крайней мере одного сумматора блока 1-К сложения по модулю два присутствует единичный логическии сигнал, который поступает на вход элемента ИЛИ 2 и вызывает на его выходе, являющемся выходом порогового логического элемента,единичный логический сигнал. Следовательно, каждый раз, когда число единичных логических сигналов на входах порогового логического элемента больше или равно а, на его выходе присутствует единичный логический сигнал. Поскольку между выходом 3 и входами для получения нужного порога требуется срабатывание относительно малого количества последовательно соединенных сумматоров, пороговый логический элемент обеспечивает получение повышенного быстродействия. Формула изобретения Пороговый логический элемент, содержащий блоки сложения по модулю дв входы каждого из которых, кроме первого, соединены с выходами предыдущего блока сложения по модулю два, входы первого блока сложения по модулю два соединены с входами порогового логического элемента, а каждый блок сложения по модулю два содержит группы .сумматоров, входы сумматоров первой группы соединены с входами данного блбка сложения по модулю два, входы сумматоров остальных групп соединены с выходами сумм предыдущей группы сумматоров, выходы переносов сумматоров соединены с выходами данного блока сложения

« .

ь/

1-2 9

IK

J

W7./ 8 по модулю два, а выход суммы сумматора последней группы сумматоров данного блока сложения по модулю два соединен с вспомогательным выходом данного блока сложения по модулю два, отличающийся тем, что, с целью повышения быстродействия, в него введен элемент ИЛИ,-выход и входы которого соединены соответственно с выходом порогового логического элемента и с выходами последнего блока сложения по модулю два. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельстов СССР № 683025, кл. Н 03 К 19/23, 1979. 2.Авторское свидетельство СССР по заявке V 2782136/18-21, кл. Н 03 К iq/23.,1979 (прототип).,

Авторы

Даты

1982-11-15—Публикация

1980-11-17—Подача