Изобретение относится к импульсной технике и может использоваться в системах автоматического управления, например, скоростью двигателя.

Цель изйб.ретения - повышение быст- родействия и точности,

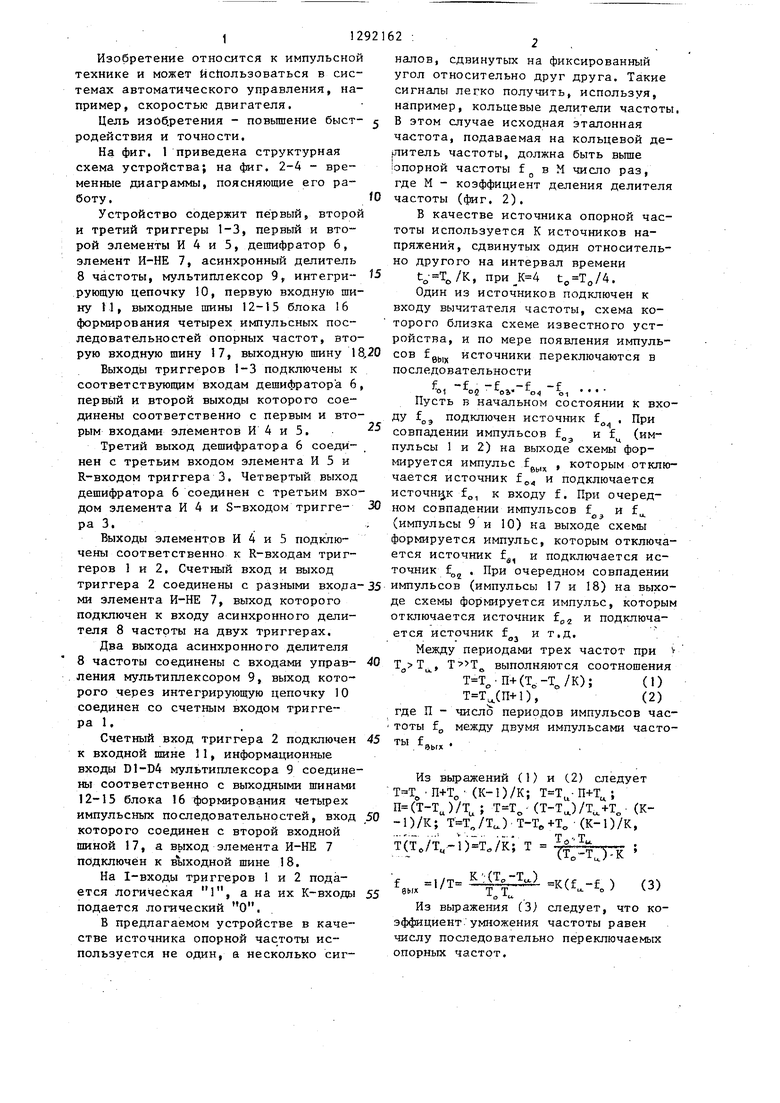

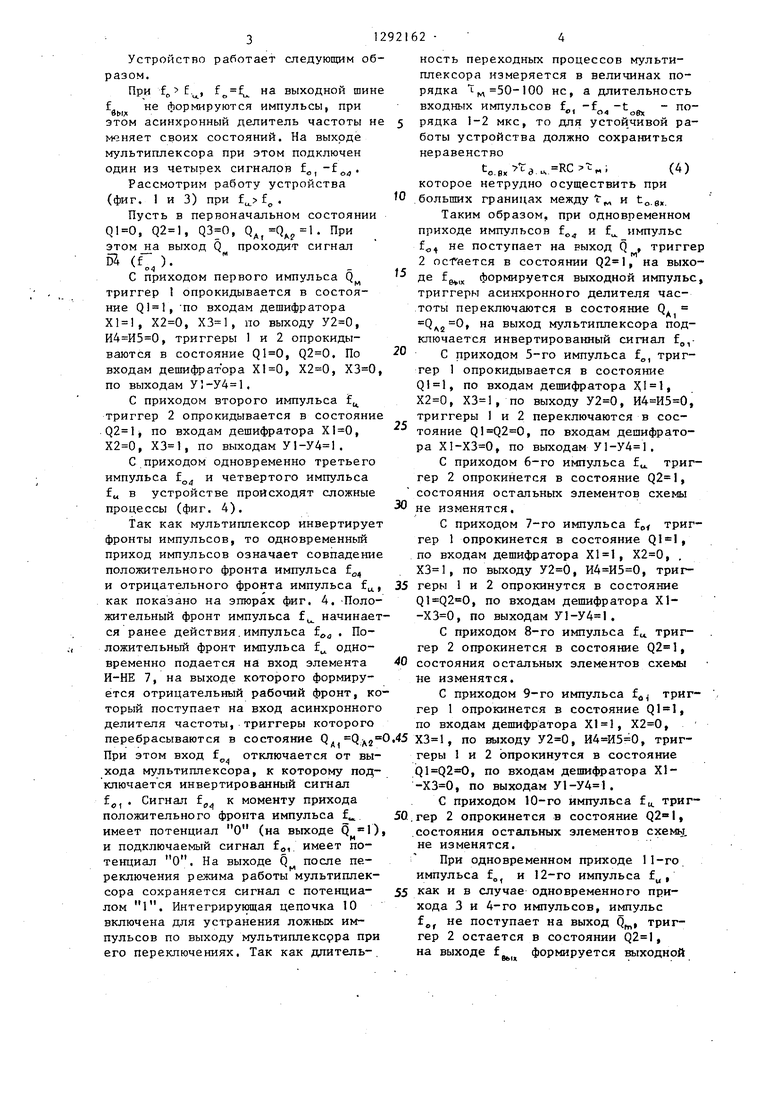

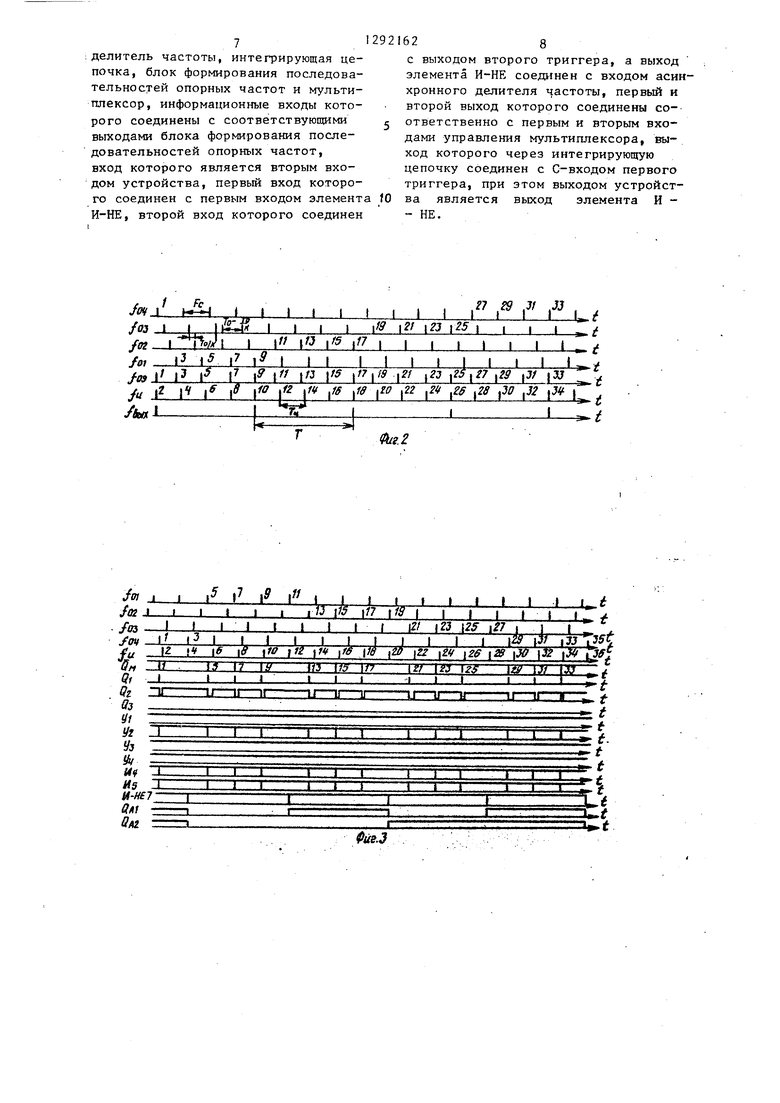

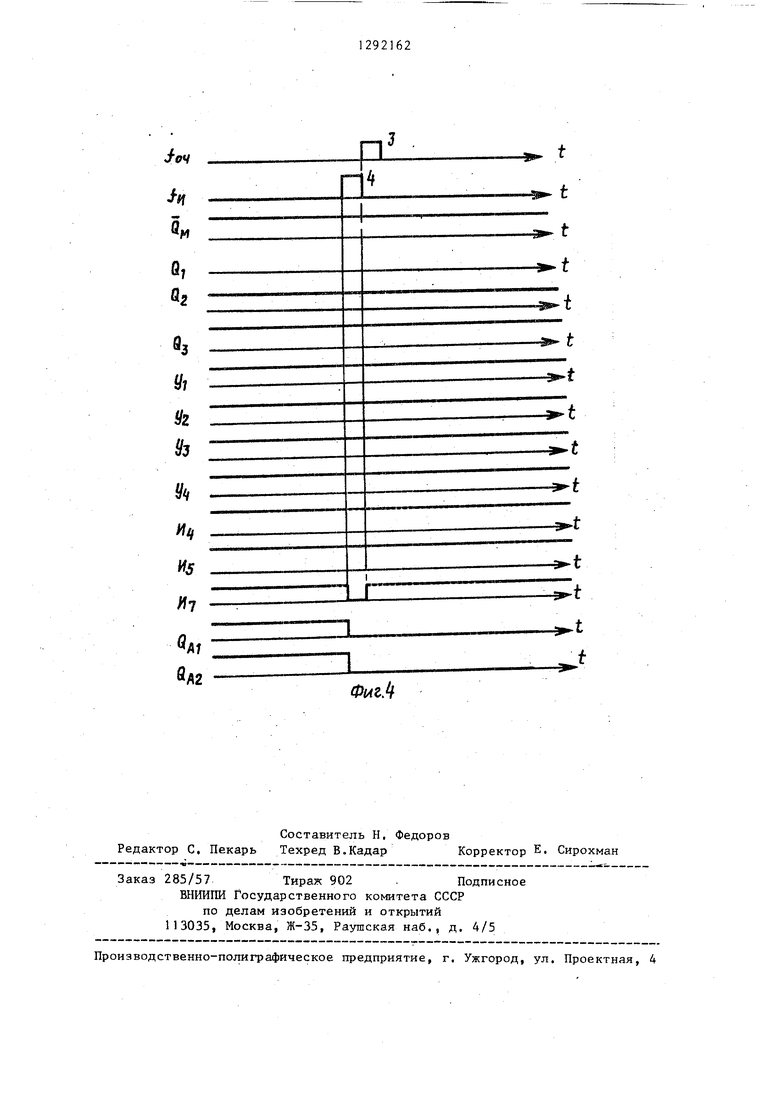

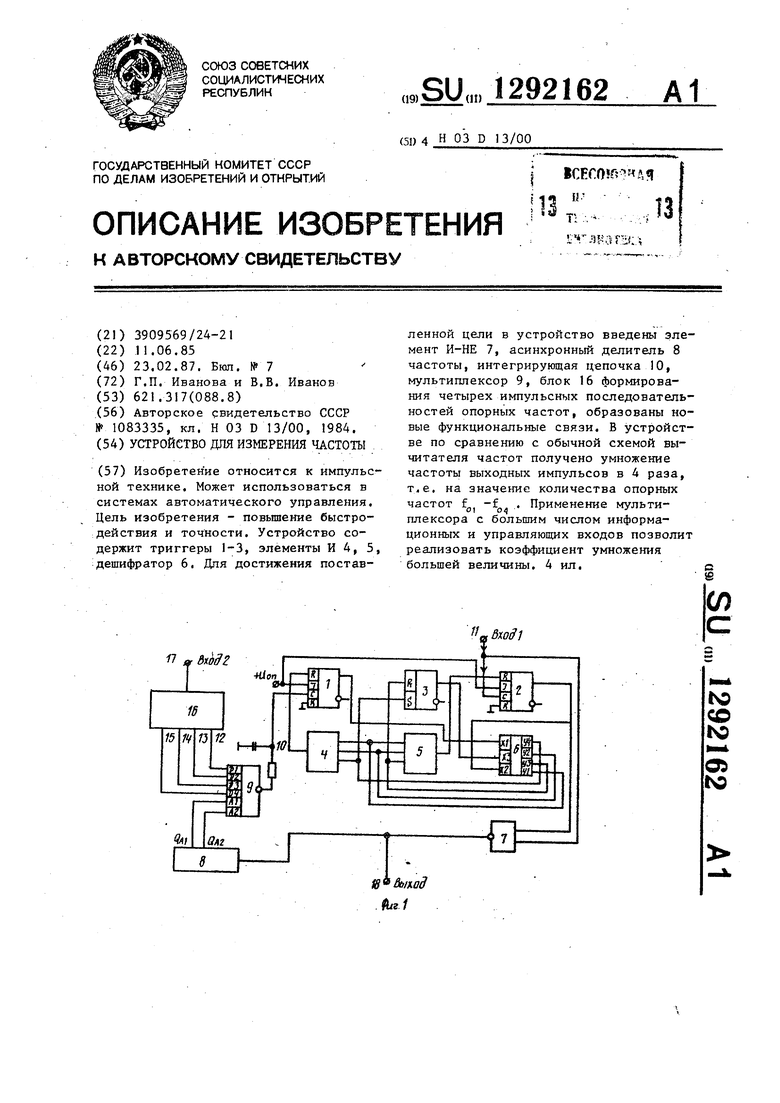

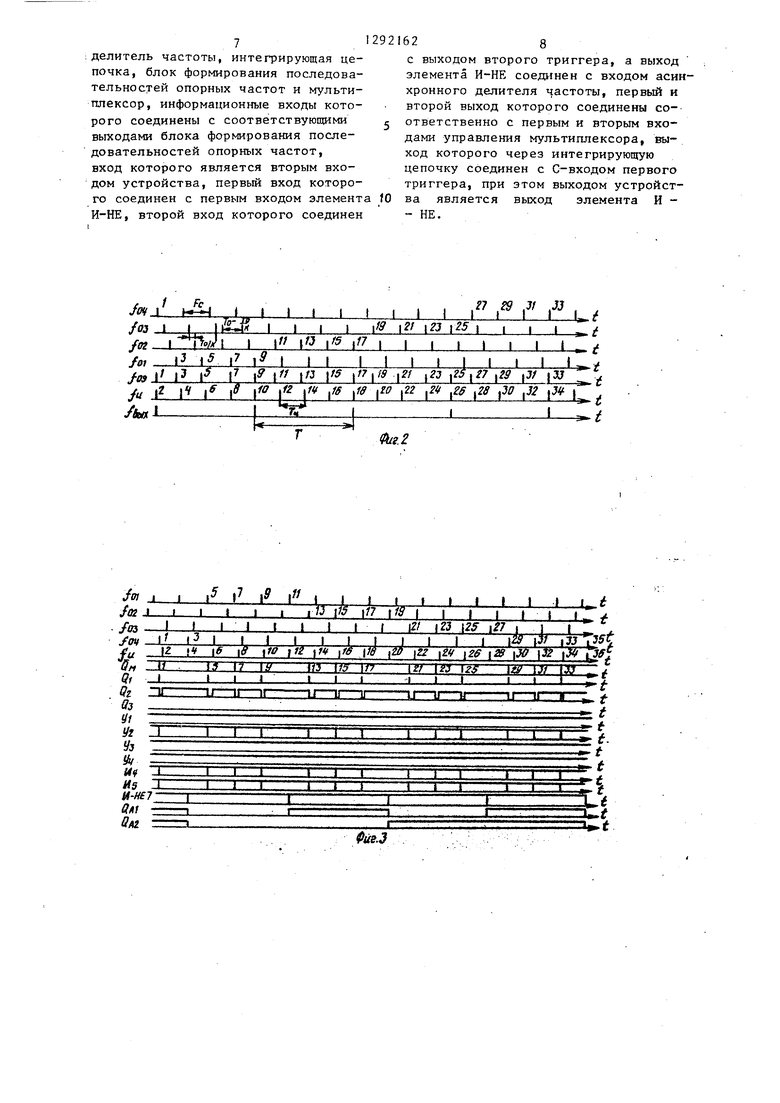

На фиг. 1 приведена структурная схема устройства; на фиг. 2-4 - временные диаграммы, поясняющие его работу.

Устройство содержит первый, второй и третий триггеры 1-3, первый и второй элементы И 4 и 5, дешифратор 6, элемент И-НЕ 7, асинхронный делитель 8 частоты, мультиплексор 9, интегри- рующую цепочку 10, первую входную шину 11, выходные шины 12-15 блока 16 формирования четырех импульсных последовательностей опорных частот, вторую входную шину 17, выходную шину 18

Выходы триггеров 1-3 подключены к соответствующим входам дешифратора 6 первый и второй выходы которого соединены соответственно с первым и вторым входами элементов И 4 и 5.

Третий выход дешифратора 6 соеди- нен с третьим входом элемента И 5 и R-входом триггера 3. Четвертый выход дешифратора 6 соединен с третьим входом элемента И 4 и S-входом тригге- ра 3,

Выходы элементов И 4 и 5 подключены соответственно к R-входам триггеров 1 и 2, Счетный вход и выход триггера 2 соединены с разными входами элемента И-НЕ 7, выход которого подключен к входу асинхронного делителя 8 частоты на двух триггерах.

Два выхода асинхронного делителя 8 частоты соединены с входами управ- , ления мультиплексором 9, выход которого через интегрирующую цепочку 10 соединен со счетным входом триггера 1 .

Счетный вход триггера 2 подключен к входной шине 11, информационные входы D1-D4 мультиплексора 9 соединены соответственно с выходными шинами 12-15 блока 16 формирования четырех импульсных последовательностей, вход которого соединен с второй входной шиной 17, я выход элемента И-НЕ 7 подключен к выходной шине 18.

На 1-входы триггеров 1 и 2 подается логическая 1, а на их К-входы подается логический О.

В предлагаемом устройстве в качестве источника опорной частоты используется не один, а несколько сигналов, сдвинутых на фиксированный угол относительно друг друга. Такие сигналы легко получить, используя, например, кольцевые делители частоты В этом случае исходная эталонная частота, подаваемая на кольцевой даритель частоты, должна быть вьш1е |опорной частоты f в М число раз, где М - коэффициент деления делителя частоты (фиг. 2).

В качестве источника опорной частоты используется К источников напряжения, сдвинутых один относительно другого на интервал времени

, .

Один из источников подключен к входу вычитателя частоты, схема которого близка схеме известного устройства, и по мере появления импульсов источники переключаются в последовательности

f f -F - f- -f

-01 oъ oA 01

Пусть В начальном состоянии к входу fo3 подключен источник f . При совпадении импульсов f и f (импульсы 1 и 2) на выходе схемы формируется импульс , которым отключается источник f j, и подключается источн1 к „, к входу f. При очередном совпадении импульсов f и f (импульсы 9 и 10) на выходе схемы формируется импульс, которым отключается источник f и подключается источник f , При очередном совпадении импульсов (импульсы 17 и 18) на выходе схемы формируется импульс, которым отключается источник f и подключается источник и т.д.

Между периодами трех частот при , выполняются соотношения .n-f(T,); (О T Tjn+l),(2)

где И - число периодов импульсов час тоты fj, между двумя импульсами часто™.вь-х . .

Из выражений (1) и (2) следует Т-Т П+Т„ (К-1) /К; П+Т ; n(T-Tj/T ; (T-TJ/T +T - (К- -1) /К; /Т, ) Т-Т, +Т„ (К- О /К,

T()T,/k; Т -1

()К

. /Т ЫЕ|1Ьа.к(-4) (3)

Из выражения (3J следует, что коэффициент ум11ожения частоты равен числу последовательно переключаемых опорных частот.

Устройство работает следующим образом.

При fо Е., „ на выходной шине f не формируются импульсы, при этом асинхронный делитель частоты не меняет своих состояний. На выходе мультиплексора при этом подключен один из четырех сигнапов f

Рассмотрим работу устройства (фиг. 1 и 3) при .

Пусть в первоначальном состоянии , , , . При этом на выход Q проходит сигнал

7, )

с приходом первого импульса Q триггер 1 опрокидывается в состояние Q l, ПО входам дешифратора , , , по выходу , , триггеры 1 и 2 опрокидываются в состояние , . По входам дешифрат ора , , , по выходам .

С приходом второго импульса f триггер 2 опрокидывается в состояние по входам дешифратора , , , по выходам У1-У4 1.

С приходом одновременно третьего импульса и четвертого импульса „ в устройстве происходят сложные процессы (фиг. 4).

Так как мультиппексор инвертирует фронты импульсов, то одновременный приход импульсов означает совпадение положительного фронта импульса f и отрицательного фронта импульса f, как показано на эпюрах фиг. 4. -Положительный фронт импульса f. начинается ранее действия.импульса f

ложительный фронт импульса f одновременно подается на вход элемента И-НЕ 7, на выходе которого формируется отрицательный рабочий фронт, который поступает на вход асинхронного делителя частоты, триггеры которого перебрасываются в состояние Q При этом вход fp отключается от выхода мультиплексора, к которому подключается инвертированный сигнал f,, . Сигнал fg к моменту прихода положительного фронта импульса f имеет потенциал О (на выходе Q Г), и подключаемый сигнал fo,. имеет потенциал О. На выходе Q после переключения режима работы мультиплексора сохраняется сигнал с потенция- лом 1. Интегрирующая цепочка 10 включена для устранения ложных импульсов по выходу мультиплексрра при его переключениях. Так как длитель-.

5

0

0

ЗО

35 400,45 5Q , 55

ность переходных процессов мультиплексора измеряется в величинах порядка 1 50-100 НС, а длительность

входных импульсов fp, ot о9х

рядка 1-2 МКС, то для устойчивой работы устройства должно сохраниться неравенство

to..u,(4)

которое нетрудно осуществить при больших границах между t и t.g.

Таким образом, при одновременном приходе импульсов f и f импульс f не поступает на выход Q , триггер 2 ос Гается в состоянии , на выходе fg, формируется выходной импульс, триггеры асинхронного делителя частоты переключаются в состояние Q , на выход мультиплексора подключается инвертированный сигнал f,С приходом 5-го импульса „, триггер 1 опрокидывается в состояние , по входам дешифратора , , по выходу , , триггеры 1 и 2 переключаются в состояние , по входам дешифратора Х1-ХЗ 0, по выходам У1-У4 1.

С приходом 6-го импульса „. триггер 2 опрокинется в состояние , состояния остальных элементов схемы не изменятся.

С приходом 7-го импульса „ триггер 1 опрокинется в состояние , по входам дешифратора , , , , по выходу , , триггеры 1 и 2 опрокинутся в состояние , по входам дешифратора XI- , по выходам У1-У4 1.

С приходом 8-го импульса „. триггер 2 опрокинется в состояние , состояния остальных элементов схемы Ие изменятся.

С приходом 9-го импульса f триггер 1 опрокинется в состояние , по входам дешифратора , , , по выходу , , триггеры 1 и 2 опрокинутся в состояние , по входам дешифратора XI- , по выходам У1-У4 1.

С приходом 10-го импульса триг- . гер 2 опрокинется в состояние , .состояния остальных элементов схемы, не изменятся.

При одновременном приходе 11-го импульса f, и 12-го импульса f , как и в случае одновременного прихода 3 и 4-го импульсов, импульс д, не поступает на выход Q, триггер 2 остается в состоянии , на выходе формируется выходной

импульс, триггеры ассинхронного делителя опрокидываются в состояния , Q 0. На выход мультиплексора подключается инвертированный сигнал ,,.

С приходом 13-го импульса триггер 1 опрокинется в состояние , по входам дешифратора , , , по выходу , , триггер)1 и 2 опрокинутся в состояние , по входам дешифратора Х1-ХЗ 0, по выходам У1-У4 1.

С приходом 14-го импульса „. триггер 2 опрокинется в состояние Q2, состояния остальных элементов схемы не изменятся,

С приходом 15-го импульса f, триггер 1 опрокинется в состояние , по входам дешифратора , , , по выходу , ,, триггеры 1 и 2 опрокинутся в состояние , по входам дешифра то- ра Х1-ХЗ 0, по выходам .

С приходом 16-го импульса f триггер 2 опрокинется в состояние , состояния остальных элементов схемы не изменятся.

С приходом 17-го импульса f Ql- .

С приходом 18-го импульса f, триггер 2 опрокинется в состояние Q2--1, состояния остальных элементов схемы не изменятся.

При одновременном приходе 19-го импульса f,j и 20-го импульса f импульс 4j не поступает на выход О ,, триггер 2 остается в состоянии , на выходе f формируется выходной импульс, триггеры асинхронного делителя опрокидываются в состояния QAI выход мультиплексора поступает инвертированный сигнал ,.

С приходом 21-го импульса f,, Q1- ,

С приходом 22-го импульса f триггер 2 опрокинется в состояние , Состояния остальных элементов схемы не изменятся,

С приходом 23-го импульса f Q1-Q3 0,

С приходом 24-го импульса f триггер 2 опрокинется в состояние , состояния остальных элементов cxeNibi е изменятся,

С приходом 25-го импульса f . 01- ,

С приходом 26-го импульса f триггер 2 опрокинется в состояние

3

, состояния остальных элементов схемы не изменятся.

При одновременном приходе 27-го импульса f, и 28-го импульса f, им- пульс foj не поступает на выход Q, триггер 2 остается в состоянии , на выходе „, формируется выходной

PD1X

импульс, триггера асинхронного делителя опрокидываются в состояния Q. Q|, 1, На выход мультиплексора поступает инвертированный сигнал f. В. устройстве по сравнению с обычной схемой вычитателя частот получено умножение частоты выходных им- пульсов в 4 раза, т.е. на значение количества опорных частот ,, 04

Применение мультиплексора с большим числом информационных и управ- ляющих входов позволит реализовать коэффициент умножения большей величины.

Коэффициент умножения, необходимый для каждого устройства, обычно определяется конкретными требования- мй к устройству для измерения частоты, диапазону измерения исследуемой частоты, определяемому выражением uf f,-f,.,.H . Чем меньше отношение

LLmCXKC(лМИН

if/f , тем большим будет эффект от применения устройства с большим коэффициентом умножения.

Ф.ормула изобретения

Устройство для измерения частоты, содержащее первый, рторой и третий триггеры, первый и второй элементы И и деишфратор,, входы которого соединены соответственно с выходами триггеров, при этом первый выход дешифратора соединен с первыми входами элементов И, второй выход - с вторыми входами элементов И, третий выход - с третьим входом второго элемента И

и R-входом третьего триггера, а четвертый выход - с S-входом третьего триггера и третьим входом первого элемента И, выход которого соединен с R-входом первого триггера, выход

второго элемента И соединен с R-входом второго триггера, С-вход которого является первым входом устройства, на 1-входы первого и второго триггеров поданы потенгщалы логической

единицы, на К-входы этих триггеров - логического ыуля, отличающееся тем, что, с целью повьше- кия быстродействия и точности, в него введены элемент И-НЕ, асинхронный

71292

елитель частоты, интегрирующая цепочка, блок формирования последовательностей опорных частот и мультиплексор, информационные входы которого соединены с соответствующими выходами блока формирования последовательностей опорных частот, вход которого является вторым входом устройства, первый вход которого соединен с первым входом элемента 0 И-НЕ, второй вход которого соединен

Им.

1628

с выходом второго триггера, а выход элемента И-НЕ соединен с входом асинхронного делителя частоты, первый и второй выход которого соединены соответственно с первым и вторым входами управления мультиплексора, выход которого через интегрирующую цепочку соединен с С-входом первого триггера, при этом выходом устройства является выход элемента И - - НЕ.

Фиг

t

04 Н

бт бг

8з (/1

2 3

И И

И5 /f

ДТ бА2

f

Ф1АгМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления инвертором | 1987 |

|

SU1617584A1 |

| Широтно-импульсный модулятор | 1989 |

|

SU1677857A1 |

| Устройство для определения углового положения вала | 1987 |

|

SU1439739A1 |

| Дискриминатор импульсов | 1980 |

|

SU924847A1 |

| Устройство для измерения частоты | 1985 |

|

SU1372243A1 |

| Устройство для сравнения частот | 1982 |

|

SU1083335A1 |

| Делитель частоты | 1977 |

|

SU746942A1 |

| Устройство для измерения отношения частот | 1988 |

|

SU1661664A1 |

| Генератор псевдослучайной М-последовательности | 1985 |

|

SU1264317A2 |

| Счетчик импульсов с управляемым коэффициентом пересчета | 1974 |

|

SU517165A1 |

Изобретение относится к импульсной технике. Может использоваться в системах автоматического управления. Цель изобретения - повышение быстродействия и точности. Устройство содержит триггеры 1-3, элементы И 4, 5, :дешифратор 6. Дпя достижения поставленной цели в устройство введены элемент И-НЕ 7, асинхронный делитель 8 частоты, интегрирующая цепочка 10, мультиплексор 9, блок 16 формирования четырех импульсных последовательностей опорных частот, образованы новые функциональные связи. В устройстве по сравнению с обычной схемой вы- читателя частот получено умножение частоты выходных импульсов в 4 раза, т.е. на значение количества опорных частот fgj -f . Применение мультиплексора с большим числом информационных и управляющих входов позволит реализовать коэффициент умножения большей величины. 4 ил. to QD 1ЧЭ Од N9

| Устройство для сравнения частот | 1982 |

|

SU1083335A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-02-23—Публикация

1985-06-11—Подача