54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство преобразования параллельного кода в последовательный | 1982 |

|

SU1075408A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1983 |

|

SU1140125A1 |

| Преобразователь частоты импульсов в код | 1983 |

|

SU1156259A1 |

| Многоканальный преобразователь сопротивления в код | 1986 |

|

SU1411684A1 |

| Преобразователь частоты в код | 1987 |

|

SU1418906A2 |

| Преобразователь последовательного кода в параллельный | 1986 |

|

SU1383508A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Преобразователь частоты в код | 1985 |

|

SU1305857A1 |

| Преобразователь частота-код | 1987 |

|

SU1515368A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1990 |

|

SU1727126A1 |

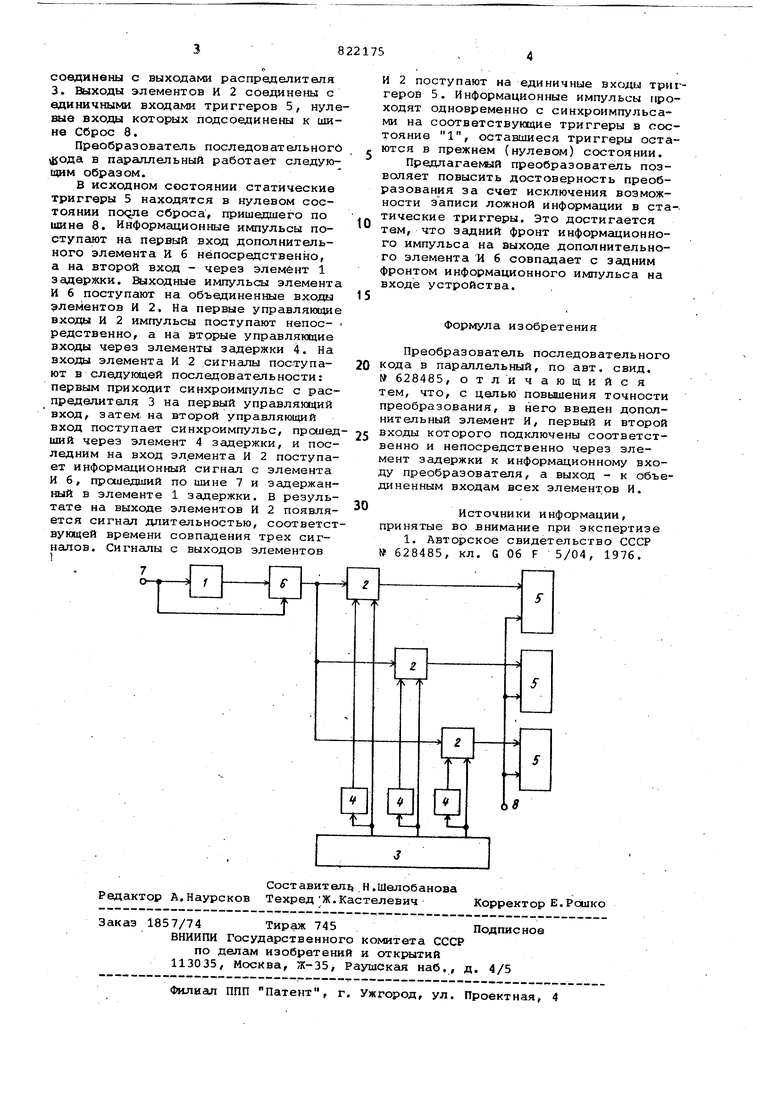

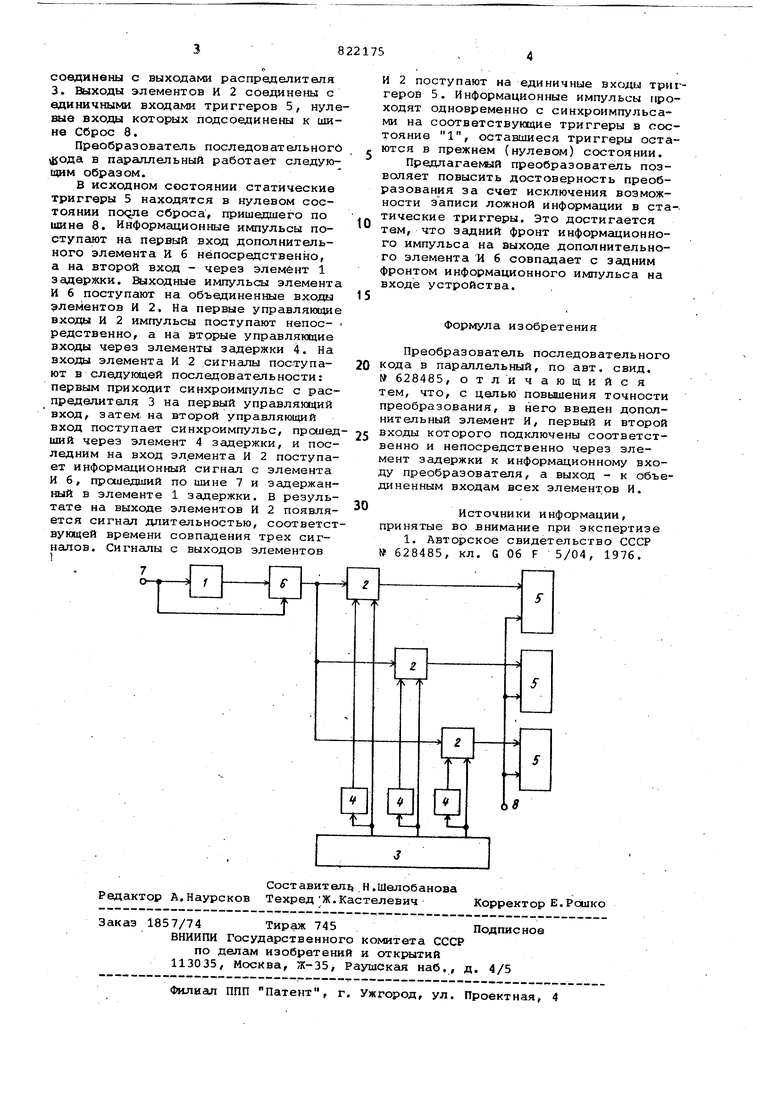

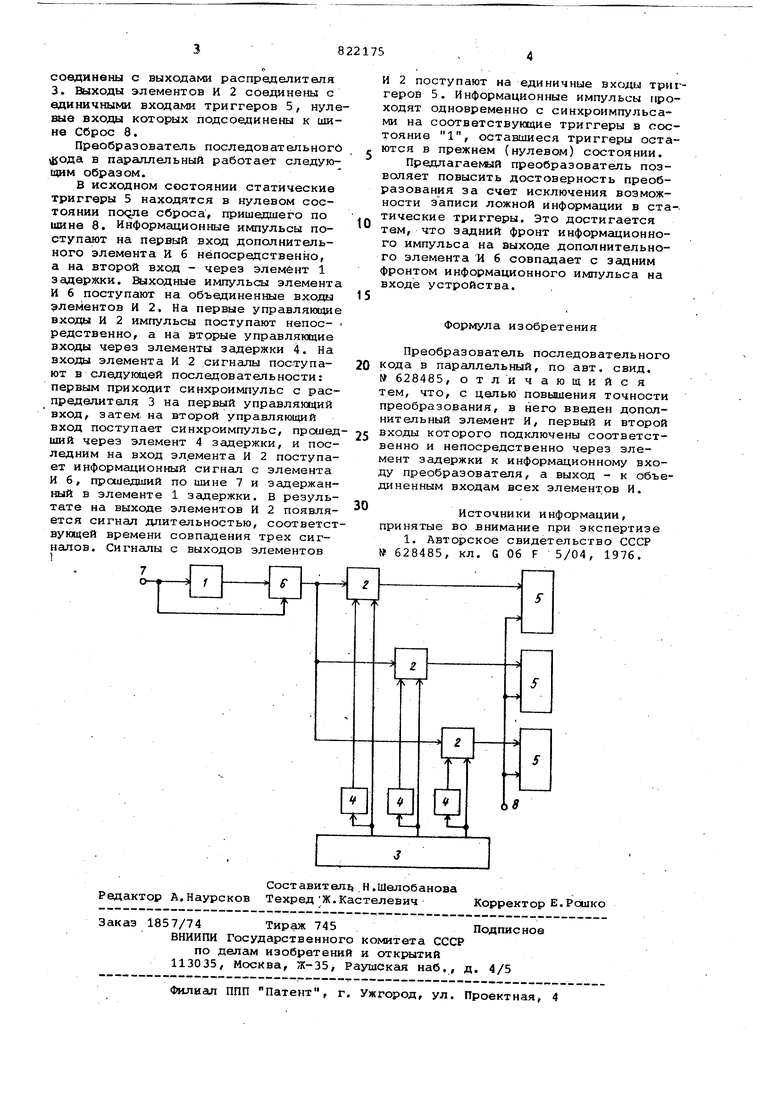

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной и измерительной техники. По основному авт. св. № 628485 известен преобразователь последовательного кода в параллельный,содержа щий элементы И, первые и вторые управляющие входы которых соединены со ответственно непосредственно и через дополнительные элементы задержки с выходами распределителя импульсов, а выходы - с единичными входами статических триггеров, нулевые входы которых подключены к шине Сброс, инфор мационный вход преобразователя сое-. динен со входом элемента задержки flJ Недостатком данного преобразовате ля является недостаточная достоверность преобразования, обусловленная возможностью записи ложной информации в статические триггеры устройства. Ложная информация может записываться вследствиевозможного перекры вания во времени сигналов, действующих на двух управляющих входах N-ro элемента И с (N-l)-M задержанным информационным импульсом, поступаиоадим на объединенные входы всех элементов И. Целью изобретения является повышение точности преобразования. Поставленная цель достигается тем, что в преобразователь последовательного кода в параллельный, по авт. свид. 628485, введен дополнительный элемент И, первый и второй входы которого подключевлл соответственно непосредственно- и через элемент задержки к информационному входу преобразователя, а выход - к объединенным входам всех .элементов И. На чертеже приведена блок-схема предлагаемого преобразователя. Преобразователь последовательного кода в параллельный содержит элемент 1 задержки, элементы И 2, распределитель 3 импульсов, элементы 4 задержки,- статические триггеры 5,.дополнительный элемент И 6, информационный вход 7, шину Сброс 8. Информационный вход 7 соединен с первым входом дополнительной схемы непосредственно, а со вторым входом - через элемент 1 задержки. Выход дополнительного элемента И 6 соединен с объединенными входами элементов И 2. Первые управляющие входы элементов И 2 непосредственно, а вторые управляющие входы через элемент задержки 4

Авторы

Даты

1981-04-15—Публикация

1979-07-10—Подача