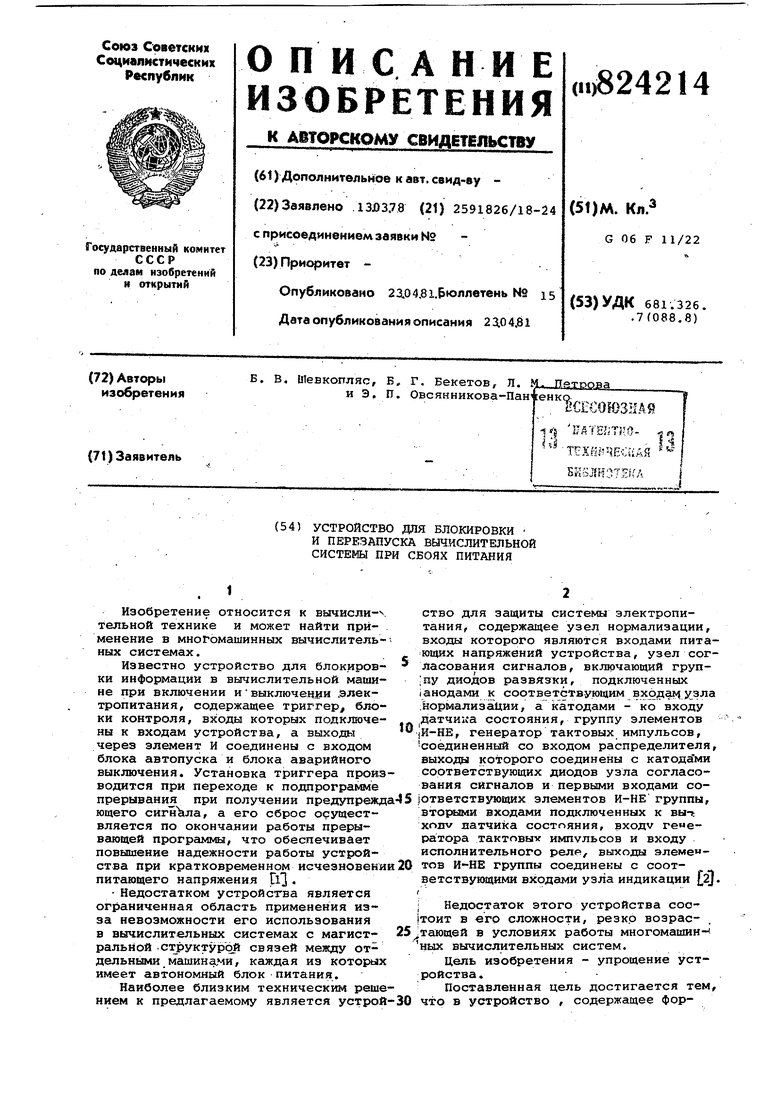

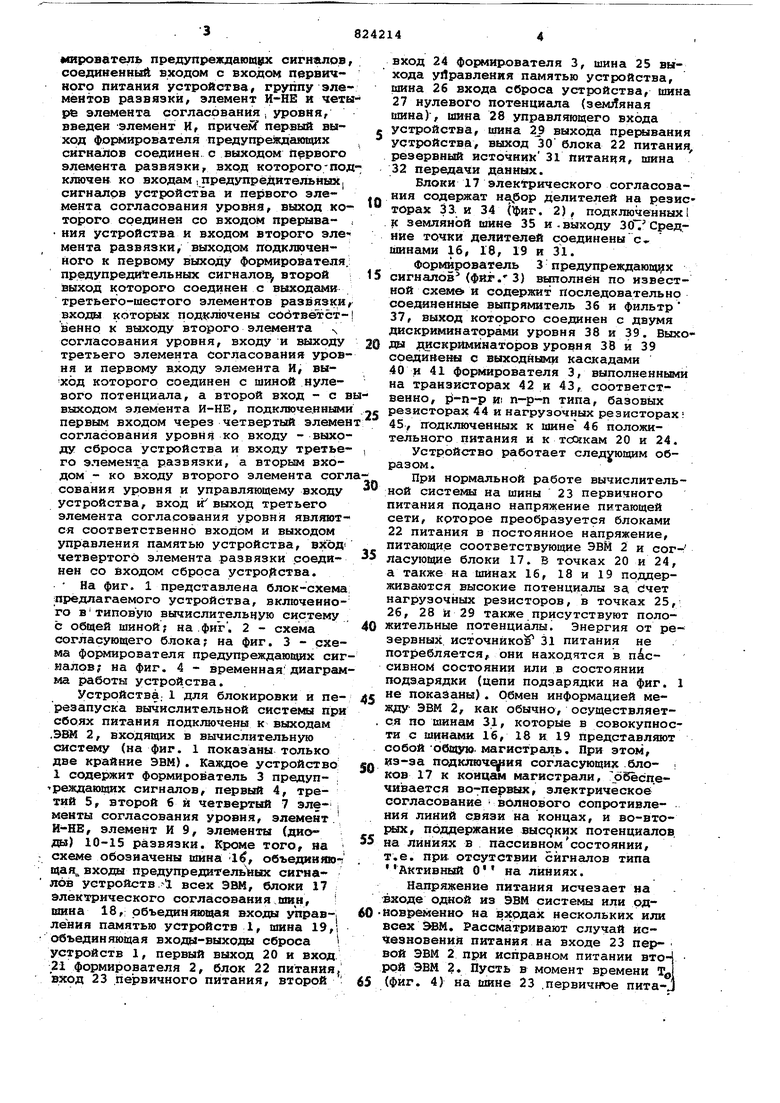

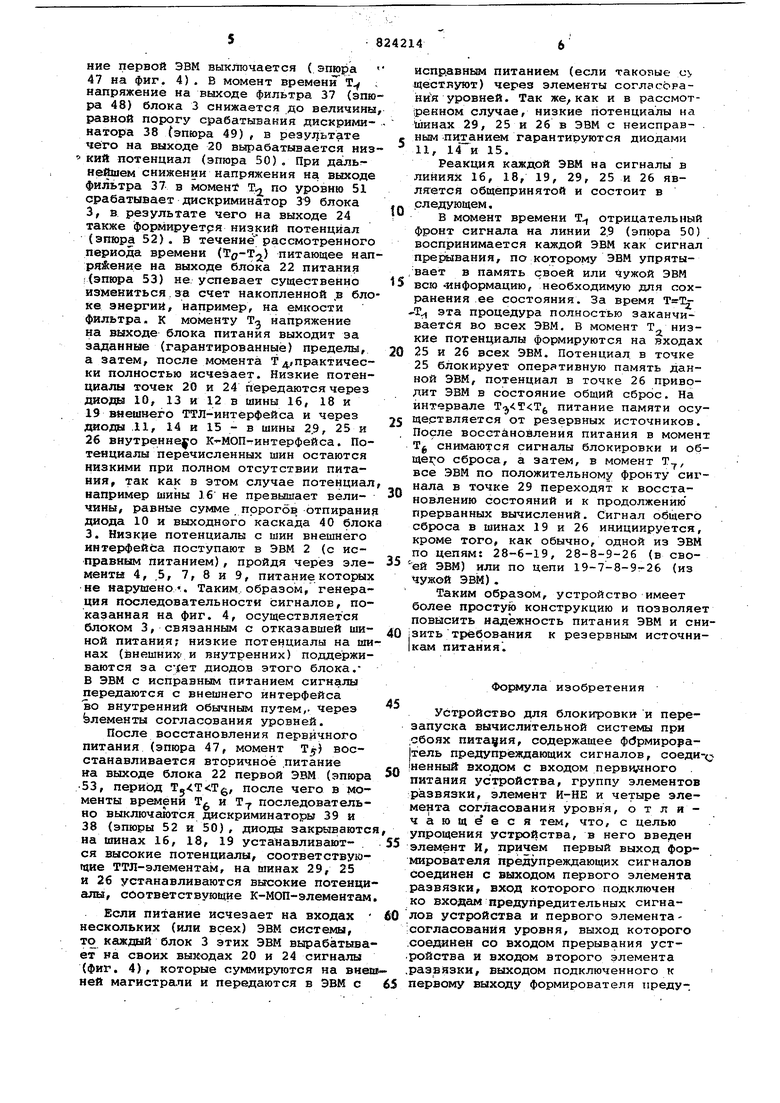

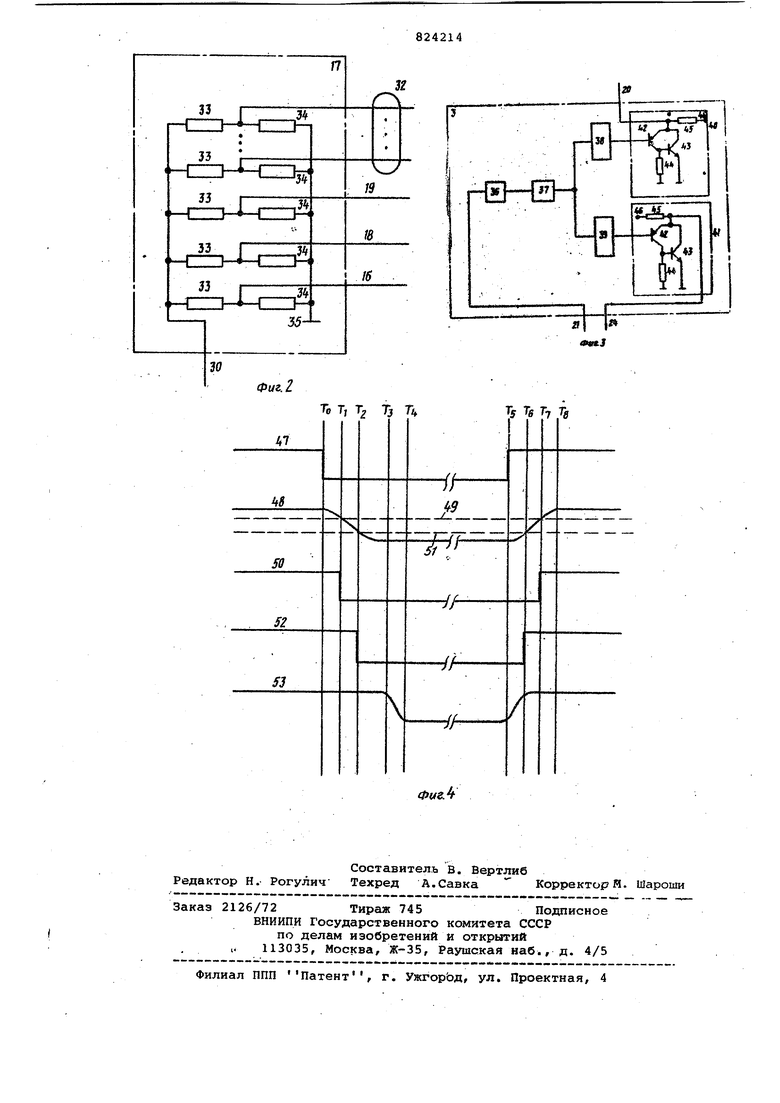

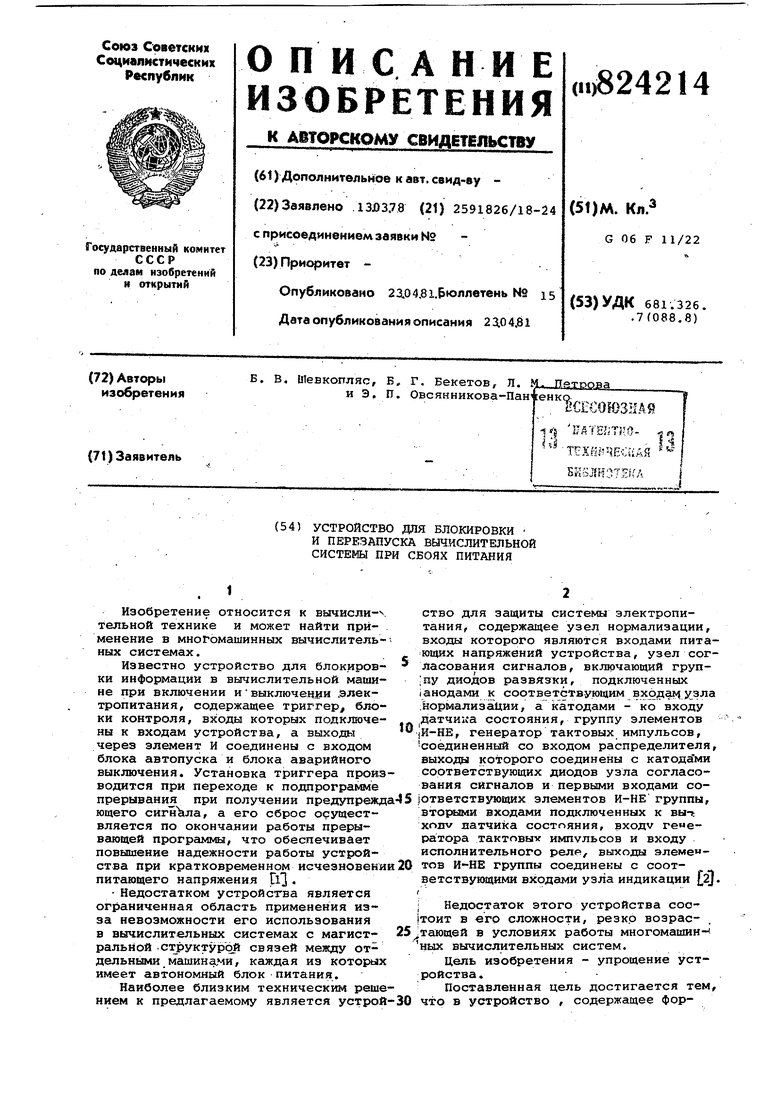

(54) УСТРОЙСТВО ДЛЯ БЛОКИРОВКИ И ПЕРЕЗАПУСКА ВЬИНСЛИТЕЛЬНОЙ СИСТЕМЫ ПРИ СБОЯХ ПИТАНИЯ мирователь предупреждают ; сигналов, соединенный входом с входом первичного питания устройства, группу элементов развязки, элемент И-НЕ и четы ре элемента согласования, уровня, введен элемент И, причейГ первый выход формирователя предупреждающих сигналов соединен, с выходом первого элемента развязки, вход которого;под ключен ко входам,предупредительных, сигналов устройства и первого элемента согласования уровня, выход которого соединен со входом прерыва- . НИН устройства и входом второго элемента развязки, выходом подключенного к первому выходу формирователя, предупредительных сигнало второй : выход которого соединен с выходами третьего-шестого элементов развяэки, входы которых подключены собтветственно к выходу второго элемента согласования уровня, входу и выходу третьего элемента согласования уровня и первому входу элемента И, вы-ход которого соединен с шиной нулевого потенциала, а второй вход - с в выходом элемента И-НЕ, подключенными первым входом через четвертый элемен согласования уровня ко входу - выходу сброса устройства и входу третьего элемента развязки, а вторым входом - ко входу второго элемента согл сования уровня и управляющему входу устройства, вход и выход третьего элемента согласования уровня явлдаотся соответственно входом и выходом управления памятью устройства, вход четвертого элемента развязки соединен со входом сброса устройства. На фиг. 1 представлена блок-схема предлагаемого устройства, включенного втиповую вычислительную систему , с общей шиной; на .фиг . 2 - схема согласующего блока на фиг. 3 - схема формирователя предупреждающих сиг налов на фиг. 4 - временная: диаграм ма работы устройства. Устройства.1 для блокировки и перезапуска вычислительной скстема при сбоях питания подключены к выходам .ЭВМ 2, входящих в вычислительную систему (на фиг. 1 показаны только две крайние ЭВМ). Каждое устройство 1 содержит формирователь 3 предуп- . реждающих сигналов, первый 4, третий 5, второй б и четвертый 7 эле- , менты согласования уровня, элемент. И-НЕ, элемент И 9, элементы (диоды) 10-15 развязки. Кроме того, йа схеме обозначены шина 1, объединяющая входы предупредительных сигналов устройств 1 всех ЭВМ, блоки 17 электрического согласования., I шина 18, объединяющая входы yinpaB-i Ленин памятью устройств 1, шина 19,1 объединяющая вход л-выходы сброса устройств 1, первый выход 20 и вход. 21 формирователя 2, блок 22 питания, вход 23 первичного питания, второй : вход 24 формирователя 3, шина 25 выхода управления памятью устройства, шина 26 входа сброса устройства, шина 27 нулевого потенцигша (земЛяная шина), шина 28 управляюгцего входа устройства, шина выхода прерывания устройства, выход 30 блока 22 питания, резервный источник 31 питания, шина 32 передачи данных. Блоки 17 электрического согласования содержат делителей на резисторах 33. и 34 (ТЬиг. 2), подклю 1енныхI к земляной шине 35 и.выходу 30.Средние точки делителей соединены с.. шинами 16, 18, 19 и 31. Формирователь 3 предупреждающих сигналов (фиг.3) вьшолнён по известной схем& и содержит последовательно соединенные выпрямитель 36 и фильтр 37, выход которого соединен с двумя дискриминаторами уровня 38 и 39. Выхоj дискриминаторов уровня 38 и 39 соединены с выходными каскадами 40 и 41 формирователя 3, выполненными на транзисторах 42 и 43, соответственно, 1)-п-р И1 п-р-п типа, базовых резисторах 44 и нагрузочных резисторах; 45, подключенных к шине 46 положительного питания и к 20 и 24. Устройство работает следующим образом. При нормальной работе вычислительной системы на шины 23 первичного питания подано напряжение питающей сети, которое преобразуется блоками 22 питания в постоянное напряжение, питающие соответствующие ЭВМ 2 и согЛасующие блоки 17. В точках 20 и 24, а также на шинах 16, 18 и 19 поддерживаются высокие потенциалы за, Счет нагрузочных резисторов, в точках 25, 26, 28 И 29 также присутствуют положительные потенциалы. Энергия от резервных источником 31 питания не потребляется,, они находятся в пАссивном состоянии или в состоянии подзарядки (цепи подзарядки на фиг. 1 не показаны). Обмен информацией между ЭВМ 2, как обычно, осуществляется по шинам 31, которые в совокупности с шинами 16, 18 и 19 Представляют собойОбщую, магистраль. При этом, из-за подключ ия согласующих блоков 17 к концам магистрали, рбёсдечи:вается во-первых, электрическое согласование вблнового сопротивления линий связи на концах, и во-втоptisx., поддержание высоких потенциалов, на линиях в пассивномсостоянии, т.е. при отсутствии сигналов типа АКТИВНЫЙ О на линиях. Напряжение питания исчезает на входе одной из ЭВМ системы или ofl новреМенно на заходах нескольких или всех ЭВМ. Рассматривают случай исчезновения питания на входе 23 пер- вой ЭВМ 2 при исправном питании вто-j ррй ЭВМ . Пусть в момент времени Тд (фиг. 4) на шине 23 .первичтэе пита-J

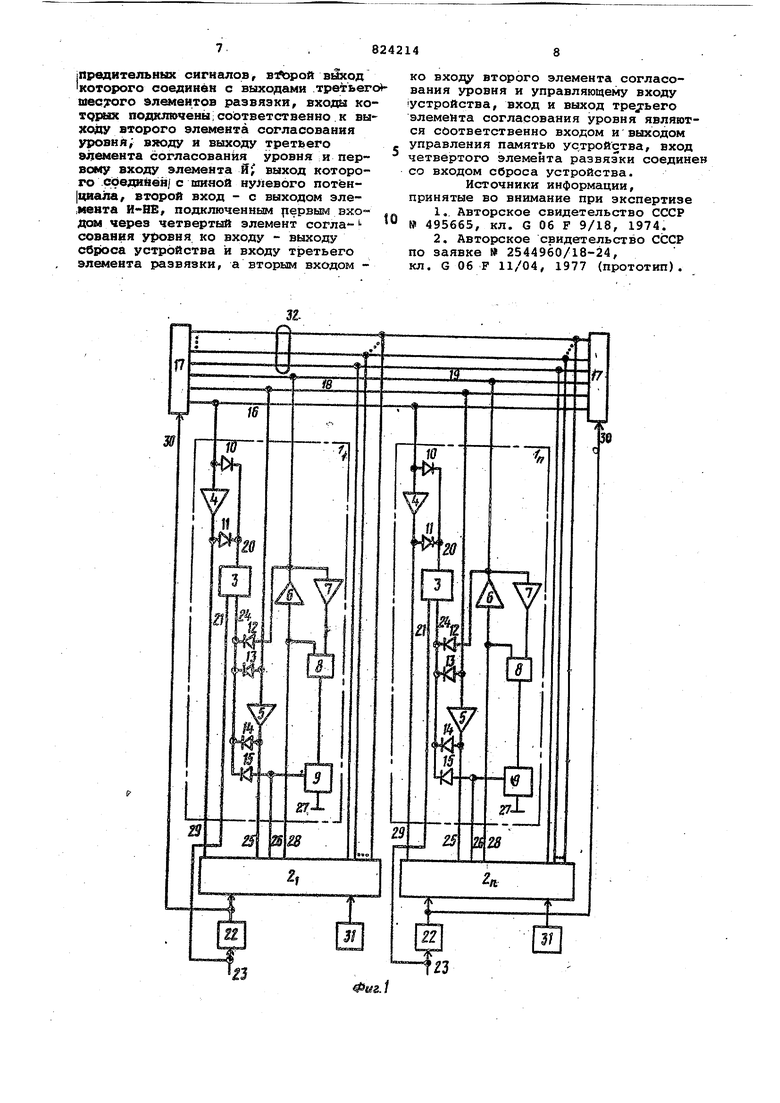

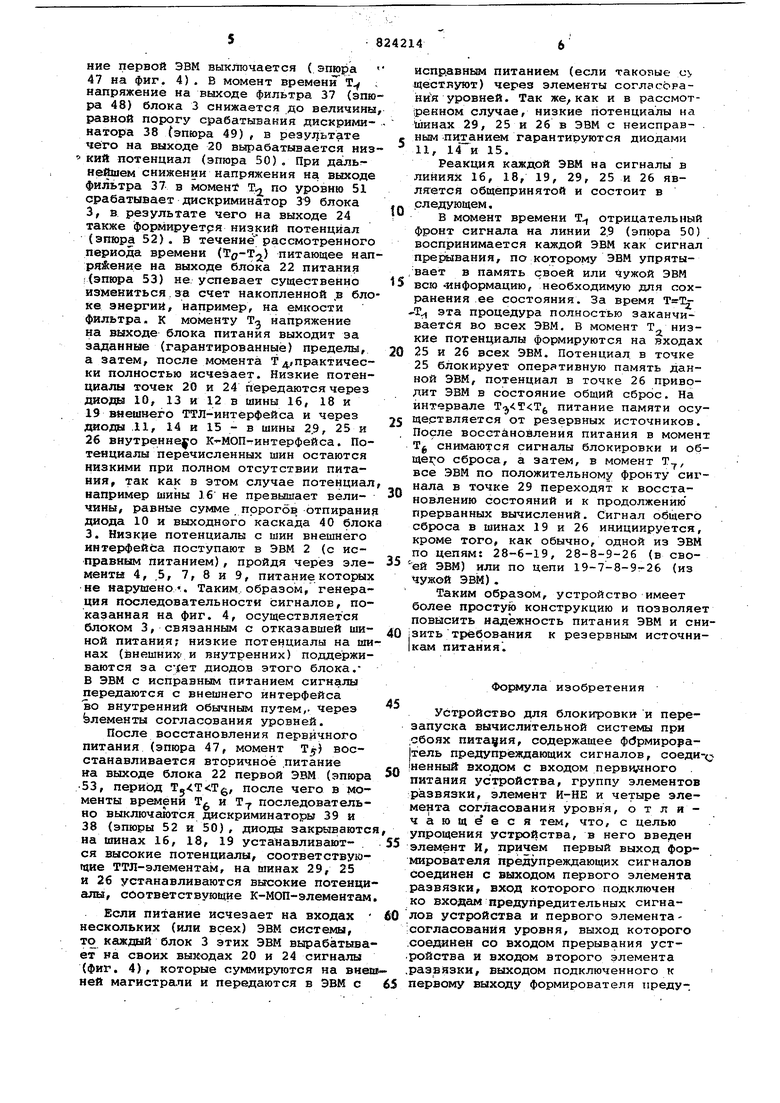

ние первой ЭВМ выключается (эпюра 47 на фиг. 4). В момент времени Т ; напряжение на выходе фильтра 37 (эпюра 48) блока 3 снижается до величины, равной порогу срабатывания дискрими- . натора 38 (эпюра 49), в результате , чего на выходе 20 вырабатывается низкий потенциал (эпюра 50), При дальнейшем снижении напряжения на выходе фильтра 37 в момент Т;. уровню 51 срабатывает дискриминатор 39 блока 3, в результате чего на выходе 24 также формируетря низкий потенциал (эпюра 52). В течениерассмотренного периода времени () питающее напря&ение на выходе блока 22 питания I (эпюра 53) не успевает существенно 15 измениться.за счет накопленной в блоке энергий, например, на емкости фильтра. К моменту Т напряжение на выходе блока питания выходит за заданные (гарантированные) пределы, 20 а затем, после момента Т д,практически полностью исчезает. Низкие потенциалы точек 20 и 24 передаются через диоды 10, 13 и 12 в шины 16, 18 и 19 вяешвего ТТЛ-интерфейса и через диоды .11, 14 и 15 - в шины 2.9, 25 и 26 внутреннего К«-МОП-гинтерфейса. Потенциалы перечисленных шин остаются низкими при полном отсутствии питания, так как в этом случае потенциал, например шины 16 не превышает вели- 30 чины, равные сумме порогов отпирания диода 10 и выходного каскада 40 блока 3. Низкре потенциалы с шин внешнего интерфейса поступают в ЭВМ 2 (с исправным питанием), пройдя через эле- 35 менты 4, .5, 7, 8 и 9, питание которых не нарушено. Таким, образом, генерация последовательности сигналов, показанная на фиг. 4, осуществляется блоком 3, связанным с отказавшей ши- 0 ной питания; низкие потенциалы на шинах (внешник и внутренних) поддерживаются за cjeT диодов этого блока. В ЭВМ с исправным питанием сигналы передаются с внешнего интерфейса во внутренний обычным путем,- 1ереэ Элементы согласования уровней.

После восстановления первичного питания (эпюра 47, момент Т5) восстанавливается вторичное питание на выходе блока 22 первой ЭВМ (эпюра 50 53, период , после чего в моменты времени Т и Т последовательно выключаются дискриминаторы 39 и 38 (эпюры 52 и 50), диоды закрываются, на шинах 16, 18, 19 устанавливают- 55 ся высокие потенциалы, соответствующие ТТЛ-элементам, на шинах 29, 25 и 26 устанавливаются выгсокне потенциалы, соответствующие К-МОП-элементам.

Если питание исчезает на входах 60 нескольких (или всех) ЭВМ системы, то каждый блок 3 этих ЭВМ вырабатывает на своих выходах 20 и 24 сигналы (фиг. 4), которые суммируются на внешиней магистрали и передаются в ЭВМ с 65

исправным питанием (если таковые с ществуют) через элементы соглэсорания уровней. Так же, как и в рассмотipeHHOM случае, низкие потенциалы на шинах 29, 25 и 26 в ЭВМ с неисправным писанием гарантируются диодами 11, 14 и 15.

Реакция каждой ЭВМ на сигналы в линиях 16, 18, 19, 29, 25 и 26 является общепринятой и состоит в следующем.

В момент времени Т-, отрицательный фронт сигнала на линии 2.9 (эпюра 50) воспринимается каждой ЭВМ как сигнал прерывания, по которому ЭВМ упряты,вает в память своей или Чужой ЭВМ всю 41Нформацию, необходимую для сохранения .ее состояния. За время эта процедура пол.ностью заканчивается во всех ЭВМ. в момент Т, низкие потенциалы формируются на входах 25 и 26 всех ЭВМ. Потенциал в точке 25 блокирует оперативную память данной ЭВМ, потенциал в точке 26 приводит ЭВМ в состояние общий сброс. На интервале питание памяти осуществляется от резервных источников. После восстановления питания в момент Tg снимаются сигналы блокировки и общег о сброса, а затем, в момент Т, все ЭВМ по положительному фронту сигнала в точке 29 переходят к восстановлению состояний и к продолжению прерванных вычислений. Сигнал общего сброса в шинах 19 и 26 инициируется, кроме того, как обычно, одной из ЭВМ по цепям: 28-6-19, 28-8-9-26 (в своей ЭВМ) или по цепи 19-7-8-9-26 (из чужой ЭВМ).

Таким образом, устройство имеет более простую конструкцию и позволяет повысить надежность питания ЭВМ и сниiвить требования к резервным источни|кам питания .

Формула изобретения

Устройство для блокировки и перезапуска вычислительной системы при ;Сбоях питания, содержащее ф(3рмирора1тель предупреждающих сигналов, соеди ненный входом с входом перви.чного . питания устройства, группу элементов развязки, элемент И-НЕ и четыре элемента согласования уровня, о т л и чающееся тем, что, с целью упрощения устройства, в него введен элемент И, причем первый выход формирователя предупреждающих сигналов соединен с выходом первого элемента развязки, вход которого подключен ко вхояам предупредительных сигналов устройства и первого элемента;согласованяя уровня, выход которого .соединен со входом прерывания уст.ройства и входом второго элемента .развяэки, выходом подключенного к первому выходу формирователя преду-. {Предительмых сигналов, в1&сод которого соединён с выходами трвтьег элементов развязки, входы ко подключены; соответственно к вы ходу второго элемента согласования уровня; вяоду и выходу третьего элемента согласования уровня и первому входу элемента Й выход которого соединён/ с шияой ну|1евого потён|циала/ второй вход - с выходом элемента И-НЕ, подключенным рервым вхо дом через четвертый элемент согласования уровня ко входу - выходу сброса устройства и входу третьего элемента развязки, а вторым входом ко зходу второго элемента согласования уровня и управляющему входу устройства, вход и выход Tpejbero элемента согласования уровня являются соответственно входом и выходом управления памятью устройства, вход четвертого элемента развязки соединен со входом сброса устройства. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № 495665, кл. G 06 F 9/18, 1974. 2.Авторское свидетельство СССР по заявке 2544960/18-24, кл. G 06 F 11/04, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля данных электронной вычислительной машины при прерываниях питания | 1983 |

|

SU1129615A1 |

| Устройство для сопряжения абонентов с электронной вычислительной машиной | 1983 |

|

SU1132283A1 |

| Устройство для блокировки и перезапуска ЭВМ при сбоях питания | 1981 |

|

SU993267A1 |

| Устройство для сопряжения абонентов с электронной вычислительной машиной | 1982 |

|

SU1076895A1 |

| Устройство для сопряжения с общей магистралью вычислительной системы | 1982 |

|

SU1100614A1 |

| Устройство для сопряжения источника информации с эвм | 1984 |

|

SU1229768A1 |

| Устройство для сопряжения источника информации с ЭВМ | 1986 |

|

SU1381528A1 |

| Устройство для контроля электронной вычислительной машины | 1981 |

|

SU1019451A1 |

| Устройство для сопряжения процессора с абонентами | 1984 |

|

SU1244669A1 |

| Устройство для подключения абонентов к магистрали передачи данных | 1984 |

|

SU1254499A1 |

Фиг. 2

«Ml

Авторы

Даты

1981-04-23—Публикация

1978-03-13—Подача