Изобретение относится к вычислительной технике и может быть использовано для построения высоконадежных вычислительных систем, построенных на базе локальной магистрали с последовательной передачей данных.

Цель изобретения - расширение класса решаемых задач устройства путем обеспечения возможности обцару- жения и отключения неисправных устройств в магистрали передачи данньк.

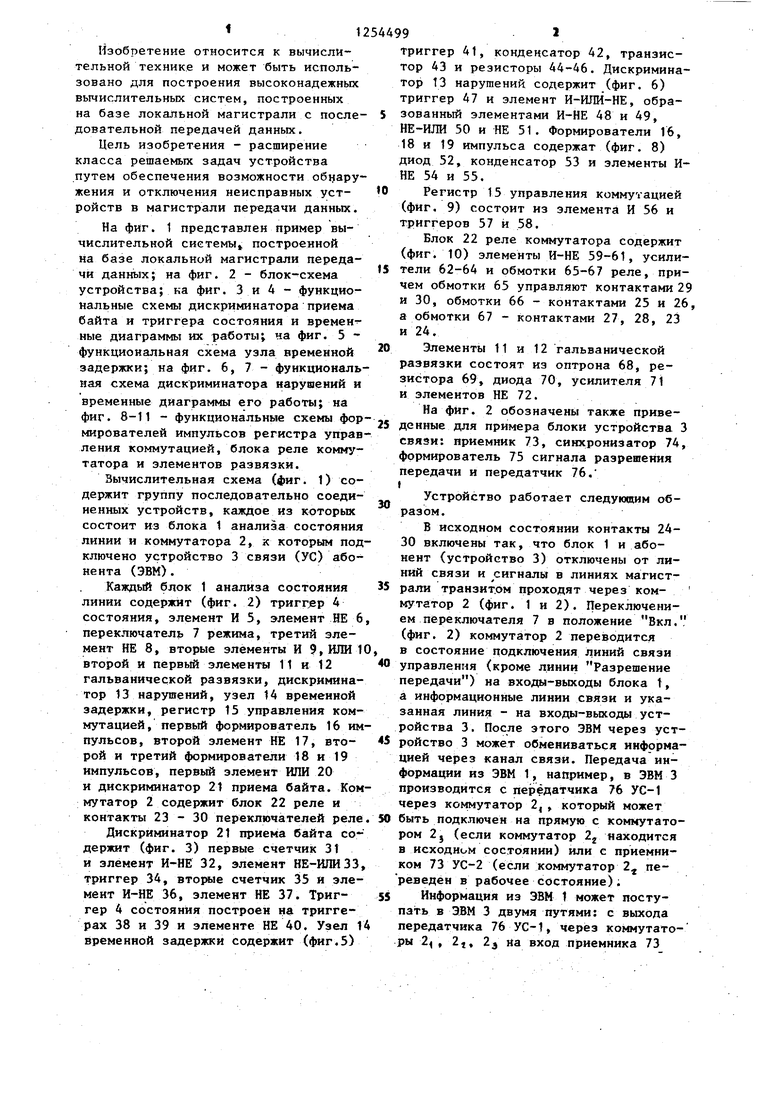

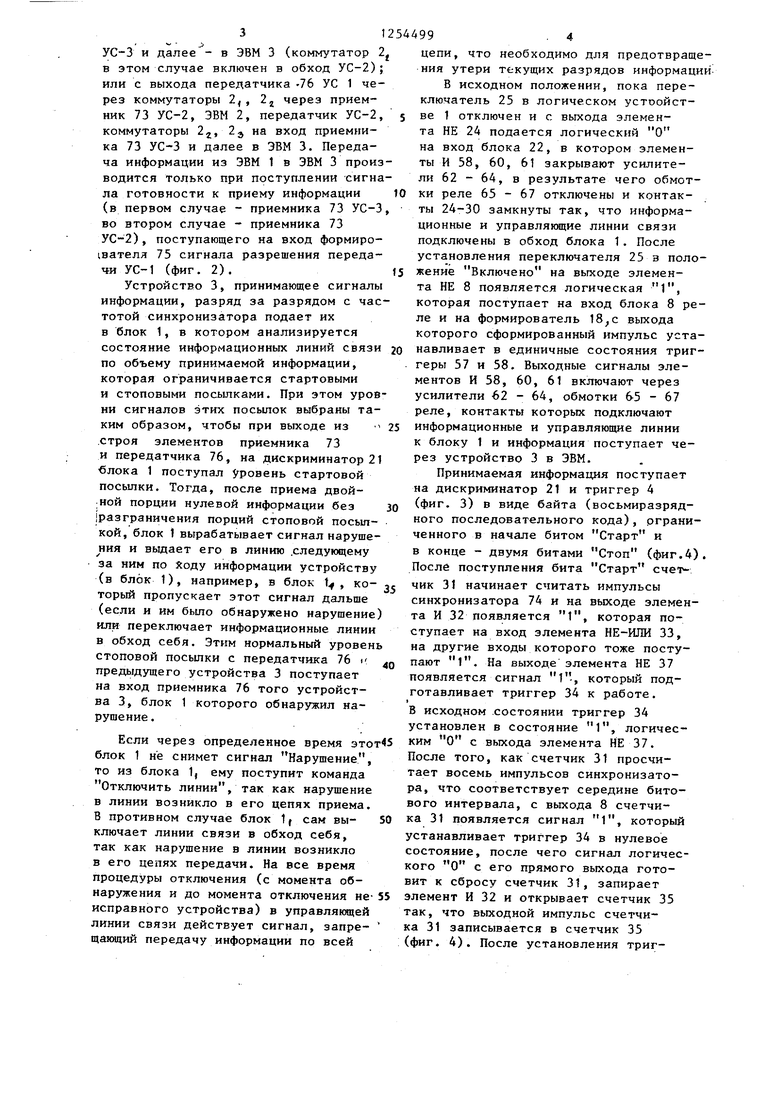

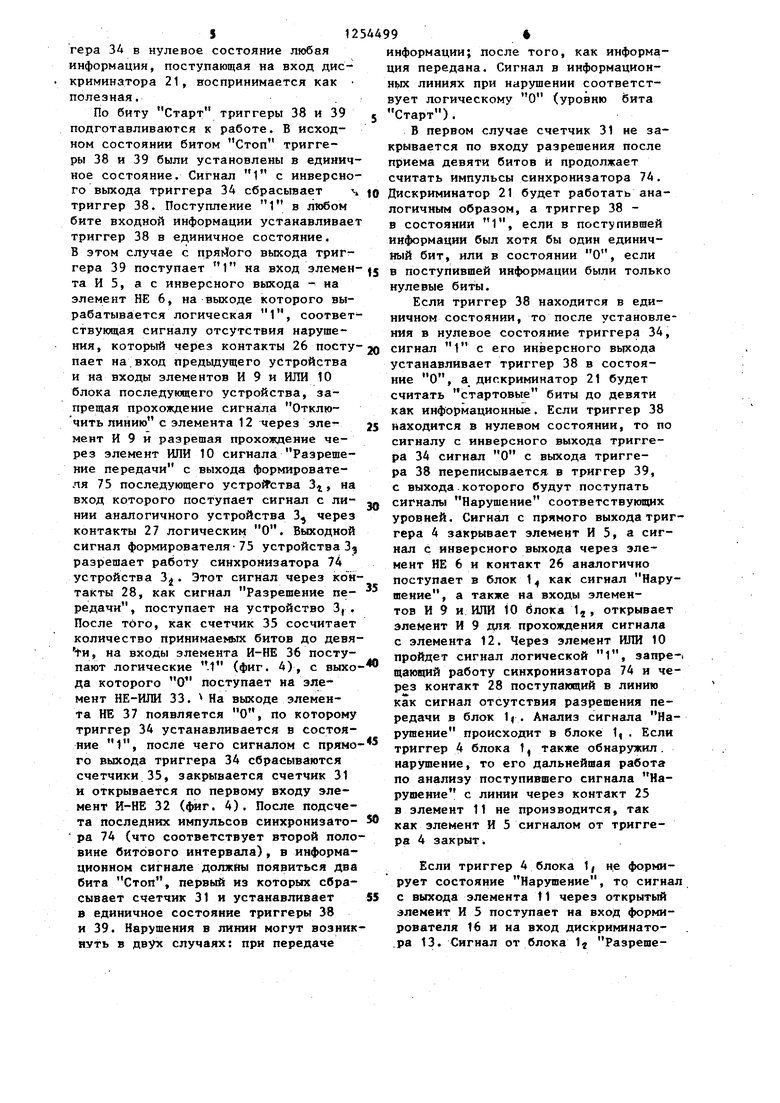

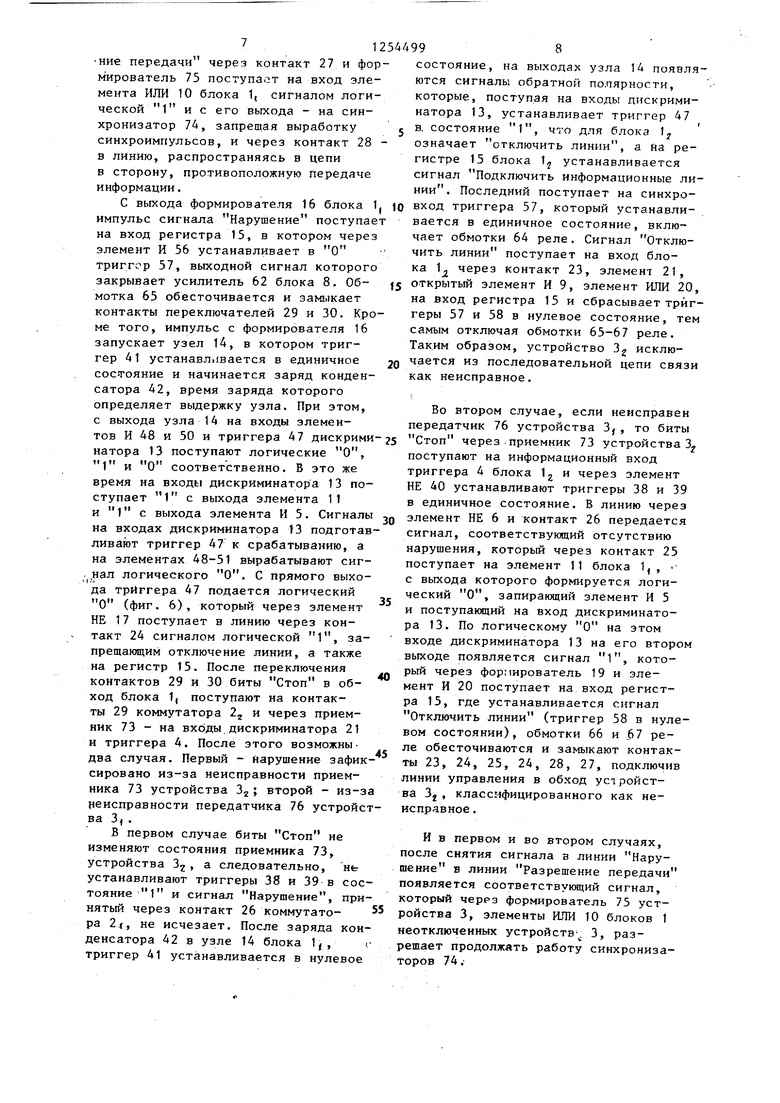

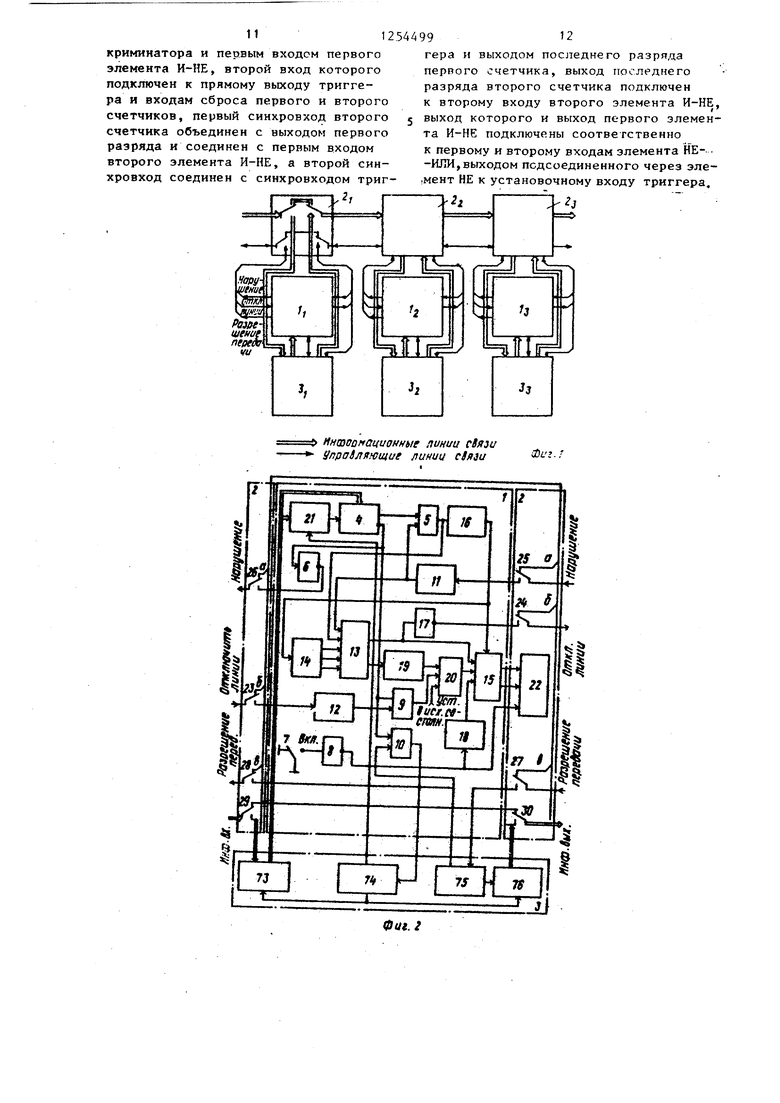

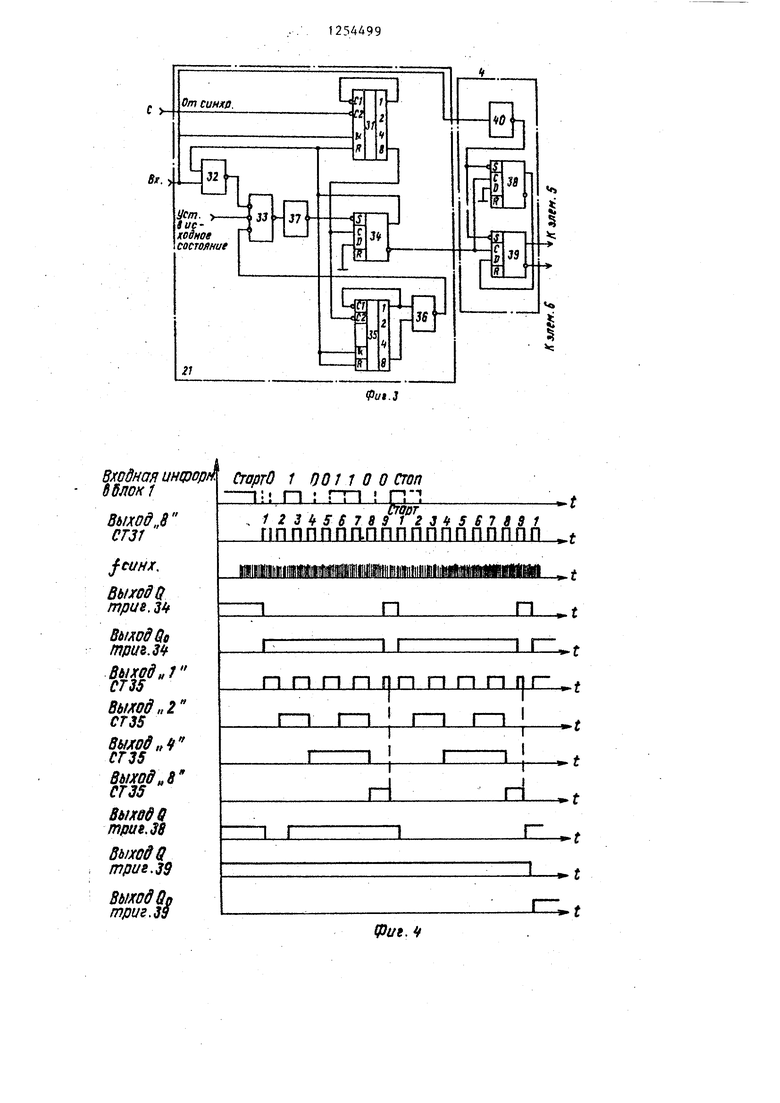

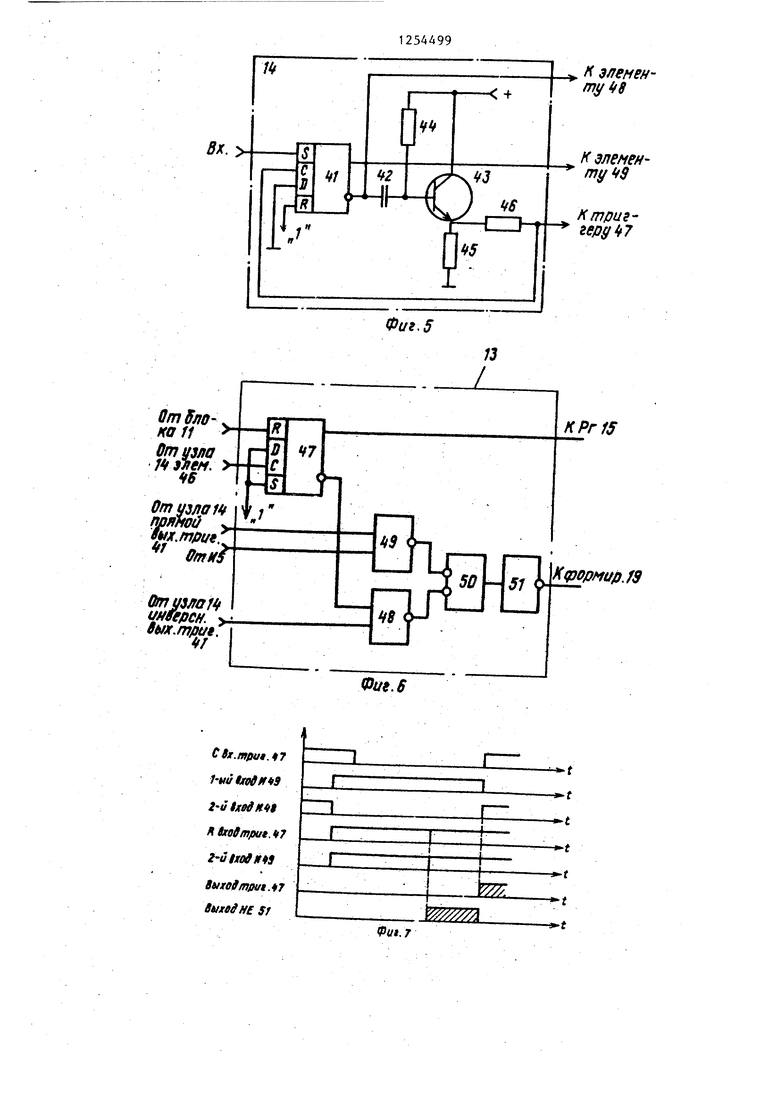

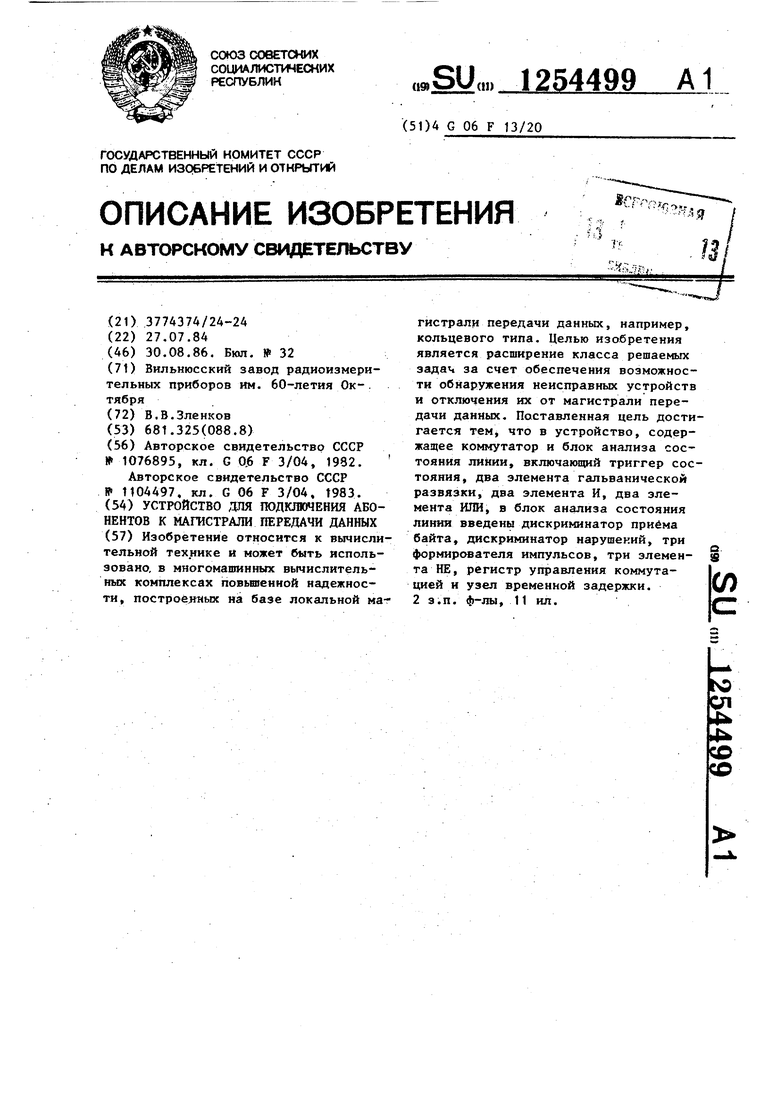

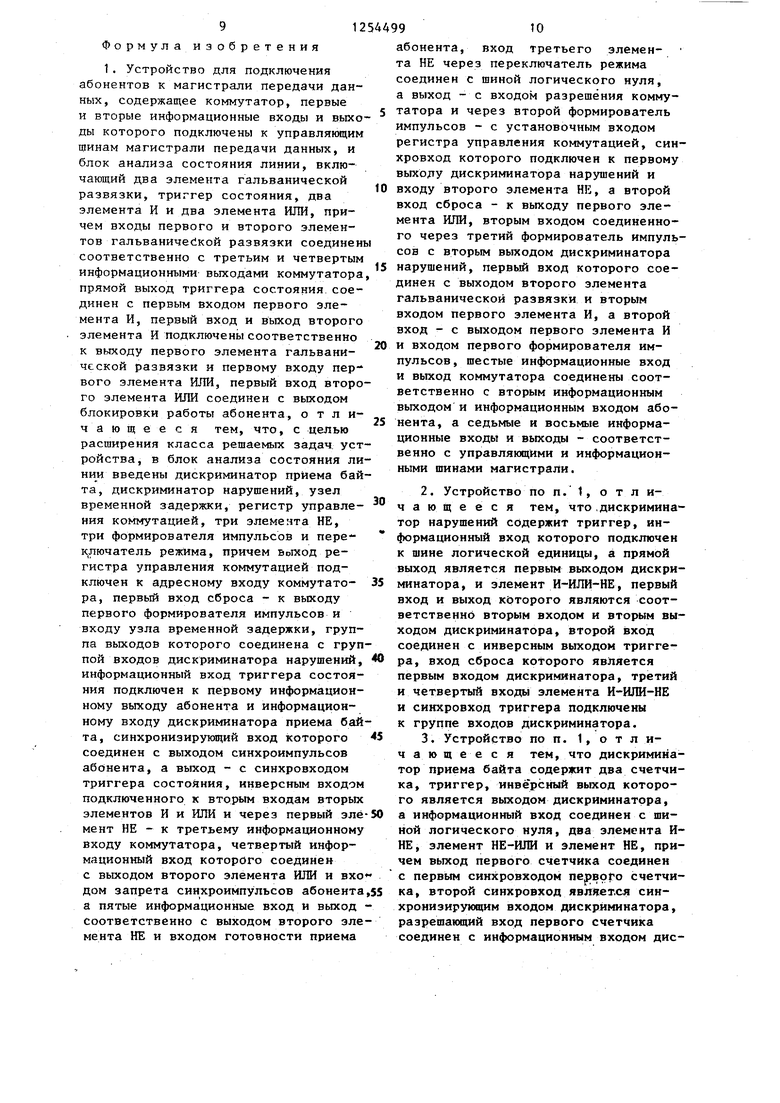

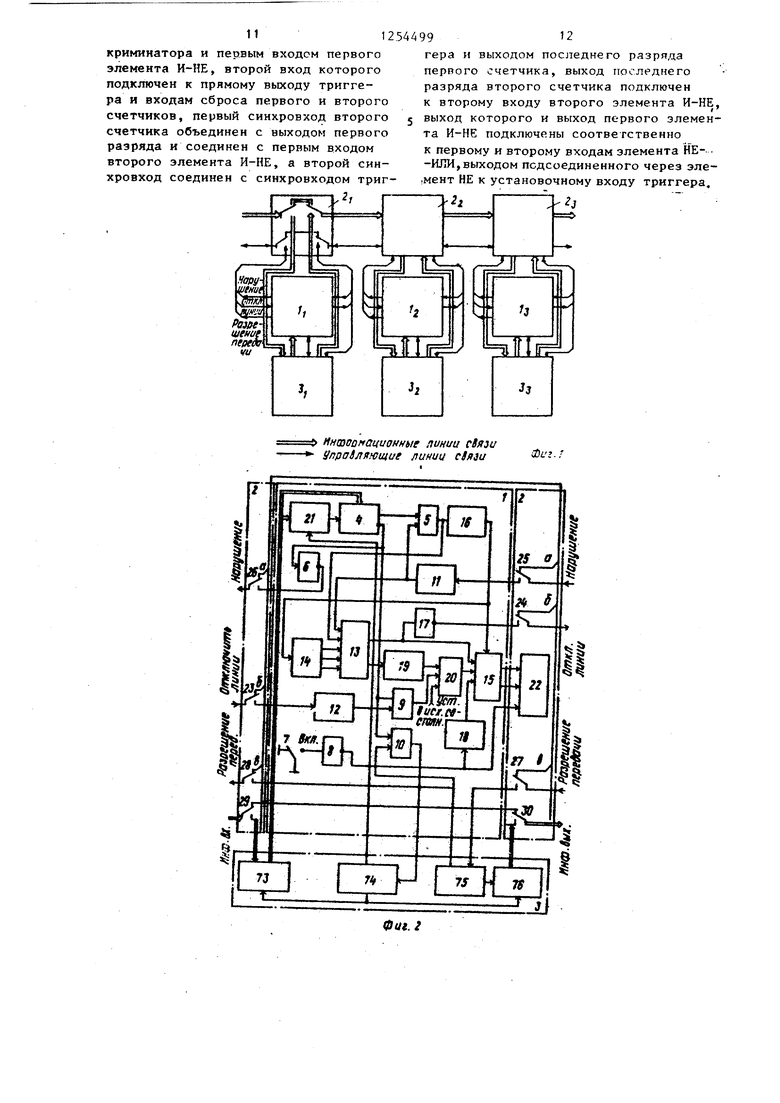

На фиг. 1 представлен пример вычислительной системы построенной на базе локальной магистрали передачи данных; на фиг. 2 - блок-схема устройства; на фиг. 3 и А - функциональные схемы дискриминатора приема байта и триггера состояния и времен ные диаграммы их работы; на фиг. 5 - функциональная схема узла временной задержки; на фиг. 6, 7 - функциональная схема дискриминатора нарушений и временные диаграммы его работы; на

На фиг. 2 обозначены также приве30

35

фиг. 8-11 - функциональные схемы фор- 5 денные для примера блоки устройства 3 мирователей импульсов регистра управ- . приемник 73, синхронизатор 74, ления коммутацией, блока реле коммутатора и элементов развязки.

Вычислительная схема (фиг. 1) содержит группу последовательно соединенных устройств, каждое из которых состоит из блока t анализа состояния линии и коммутатора 2, х которым подключено устройство 3 связи (УС) абонента (ЭВМ).

Каждый блок 1 анализа состояния линии содержит (фиг. 2) TpHrrjep 4 состояния, элемент И 5, элемент НЕ 6, переключатель 7 режима, третий элемент НЕ 8, вторые элементы И 9, ИЛИ 10, второй и первый элементы 11 и 12 гальванической развязки, дискриминатор 13 нарушений, узел 14 временной задержки, регистр 15 управления коммутацией , первый формирователь 16 импульсов, второй элемент НЕ 17, второй и третий формирователи 18 и 19 импульсов, первый элемент ИЛИ 20 и дискриминатор 21 приема байта. Коммутатор 2 содержит блок 22 реле и

связи: приемник

формирователь 75 сигнала разрешения

передачи и передатчик 76. I

Устройство работает следующим образом.

В исходном состоянии контакты 24- 30 включены так, что блок 1 и абонент (устройство 3) отключены от линий связи и сигналы в линиях магистf

рали транзитом проходят через ком- мутатор 2 (фиг. 1 и 2). Переключением переключателя 7 в положение Вкл. (фиг. 2) коммутатор 2 переводится в состояние подключения линий связи

управления (кроме линии Разрешение передачи) на входы-выходы блока t, а информационные линии связи и указанная линия - на входы-выходы устройства 3. После этого ЭВМ через уст45 ррйство 3 может обмениваться информацией через канал связи. Передача информации из ЭВМ 1, например, в ЭВМ 3 производится с передатчика 76 УС-1 через коммутатор 2, , который может

контакты 23 - 30 переключателей реле. 50 быть подключен на прямую с коммутатоДискриминатор 21 приема байта содержит (фиг. 3) первые счетчик 31 и элемент И-НЕ 32, элемент НЕ-ИЛИЗЗ, триггер 34, счетчик 3i5 и элемент И-НЕ 36, элемент НЕ 37. Триггер 4 состояния построен на триггерах 38 и 39 и элементе НЕ 40. Узел 14 временной задержки содержит (фиг.5)

триггер 41, конденсатор 42, транзистор 43 и резисторы 44-46. Дискриминатор 3 нарушений содержит (фиг. 6) триггер 47 и элемент И-ИЛИ-НЕ, образованный элементами И-НЕ 48 и 49, НЕ-ИЛИ 50 и НЕ 51. Формирователи 16, 18 и 19 импульса содержат (фиг. 8) диод 52, конденсатор 53 и элементы И- НЕ 54 и 55.

Регистр 15 управления коммутацией (фиг. 9) состоит из элемента И 56 и триггеров 57 и 58.

Блок 22 реле коммутатора содержит (фиг. 10) элементы И-НЕ 59-61, усилители 62-64 и обмотки 65-67 реле, причем обмотки 65 управляют контактами 29 и 30, обмотки 66 - контактами 25 и 26, а обмотки 67 - контактами 27, 28, 23 и 24.

Элементы 11 и 12 гальванической развязки состоят из оптрона 68, резистора 69, диода 70, усилителя 71 и элементов НЕ 72.

На фиг. 2 обозначены также приведенные для примера блоки устройства 3 . приемник 73, синхронизатор 74,

денные для примера блоки устройства 3 . приемник 73, синхронизатор 74,

связи: приемник

формирователь 75 сигнала разрешения

передачи и передатчик 76. I

Устройство работает следующим образом.

В исходном состоянии контакты 24- 30 включены так, что блок 1 и абонент (устройство 3) отключены от линий связи и сигналы в линиях магистf

рали транзитом проходят через ком- мутатор 2 (фиг. 1 и 2). Переключением переключателя 7 в положение Вкл. (фиг. 2) коммутатор 2 переводится в состояние подключения линий связи

управления (кроме линии Разрешение передачи) на входы-выходы блока t, а информационные линии связи и указанная линия - на входы-выходы устройства 3. После этого ЭВМ через устррйство 3 может обмениваться информацией через канал связи. Передача информации из ЭВМ 1, например, в ЭВМ 3 производится с передатчика 76 УС-1 через коммутатор 2, , который может

55

ром 2j (если коммутатор 2 находится в исходном состоянии) или с приемником 73 УС-2 (если коммутатор 2 пе- реведен в рабочее состояние);

Информация из ЭВМ 1 может поступать в ЭВМ 3 двумя путями: с выхода передатчика 76 УС-1, через коммутаторы 2, 2}, 2j на вход приемника 73

УС-3 и далее - в ЭВМ 3 (коммутатор 2 в этом случае включен в обход УС-2); или с выхода передатчика -76 УС 1 через коммутаторы 2 , 2,j через приемник 73 УС-2, ЭВМ 2, передатчик УС-2, коммутаторы 2, 2, на вход приемника 73 УС-3 и далее в ЭВМ 3. Передача информации из ЭВМ 1 в ЭВМ 3 производится только при поступлении сигнала готовности к приему информации (в первом случае - приемника 73 УС-3, во втором случае - приемника 73 УС-2), поступающего на вход формиро- 1вателл 75 сигнала разрешения передачи УС-1 (фиг, 2).

Устройство 3, принимающее сигналы информации, разряд за разрядом с частотой синхронизатора подает их в блок 1, в котором анализируется состояние информационных линий связи по объему принимаемой информации, которая ограничивается стартовыми и стоповыми посьшками. При этом уровни сигналов этих посылок выбраны таким образом, чтобы при выходе из .строя элементов приемника 73 и передатчика 76, на дискриминатор 21 блока 1 поступал уровень стартовой посылки. Тогда, после приема двой- ;Ной порции нулевой информации без разграничения порций стоповой посьш- кой, блок 1 вырабатывает сигнал наруше- 1ия и вьщает его в линию .следующему за ним по Ходу информации устройству (в блок 1), например, в блок t , ко- торый пропускает этот сигнал дальше (если и им было обнаружено нарушение) или переключает информационные линии в обход себя. Этим нормальньп уровень стоповой посьшки с передатчика 76 « предыдущего устройства 3 поступает на вход приемника 76 того устройства 3, блок 1 которого обнаружил нарушение .

Если через определенное время этот4 блок 1 не снимет сигнал Нарушение, то из блока 1, ему поступит команда Отключить линии, так как нарушение в линии возникло в его цепях приема. В противном случае блок If сам вы- 5 ключает линии связи в обход себя, так как нарушение в линии возникло в его цепях передачи. На все время процедуры отключения (с момента об

наружения и до момента отключения не- 55 элемент И 32 и открывает счетчик 35

исправного устройства) в управляющей линии связи действует сигнал, запрещающий передачу информации по всей

так, что выходной импульс счетчика 31 записывается в счетчик 35 ;(фиг. 4). После установления триг

s 0

цепи, что необходимо для предотвращения утери текущих разрядов информацииВ исходном положении, пока переключатель 25 в логическом устоойст- ве 1 отключен и с выхода элемента НЕ 24 подается логический О на вход блока 22, в котором элементы И 38, 60, 61 закрывают усилители 62-64, в результате чего обмотки реле 65-67 отключены и контакты 24-30 замкнуты так, что информационные и управлякнцие линии связи подключены в обход блока 1. После установления переключателя 25 в поло- 5 жение Включено на выходе элемента НЕ 8 появляется логическая 1, которая поступает на вход блока 8 реле и на формирователь выхода которого сформированный импульс устанавливает в единичные состояния триггеры 57 и 58. Выходные сигналы элементов И 58, 60, 61 включают через усилители 62 - 64, обмотки 65-67 реле, контакты которых подключают информационные и управляющие линии к блоку 1 и информация поступает через устройство 3 в ЭВМ.

Принимаемая информация поступает на дискриминатор 21 и триггер 4 (фиг. 3) в виде байта (восьмиразрядного последовательного кода), ограниченного в начале битом Старт и в конце - двумя битами Стоп (фиг.4). После поступления бита Старт счетчик 31 начинает считать импульсы синхронизатора 74 и на выходе элемента И 32 появляется 1, которая поступает на вход элемента НЕ-ИЛИ 33, на другие входы которого тоже поступают l. На выходе элемента НЕ 37

появляется сигнал , который подготавливает триггер 34 к работе.

В исходном .состоянии триггер 34 установлен в состояние 1, логическим О с выхода элемента НЕ 37. После того, как счетчик 31 просчитает восемь импульсов синхронизатора, что соответствует середине битового интервала, с вьпсода 8 счетчика 31 появляется сигнал 1, который устанавливает триггер 34 в нулевое состояние, после чего сигнал логического О с его прямого выхода готовит к сбросу счетчик 31, запирает

так, что выходной импульс счетчика 31 записывается в счетчик 35 ;(фиг. 4). После установления триггера ЗА в нулевое состояние любая информация, поступающая на вход дискриминатора 21, воспринимается как полезная.

По биту Старт триггеры 38 и 39 подготавливаются к работе. В исходном состоянии битом Стоп триггеры 38 и 39 были установлены в единичное состояние. Сигнал 1

1254499«

информации; после того, как информация передана. Сигнал в информацион- ньпс линиях при нарушении соответст- 0 (уровню бита

с инверсНовует логическому Старт).

В первом случае счетчик 31 не закрывается по входу разрешения после приема девяти битов к продолжает считать импульсы синхронизатора 74. го выхода триггера 34 сбрасывает ч ю Дискриминатор 21 будет работать ана- триггер 38. Поступление 1 в любом логичным образом, а триггер 38 - бите входной информации устанавливает триггер 38 в единичное состояние. В этом случае с выхода триггера 39 поступает 1 на вход элемен-15 в поступившей информации были только та И 5, ас инверсного выхода - на нулевые биты, элемент НЕ 6, на выходе которого выв состоянии 1, если в поступившей информации был хотя бы один единичный бит, или в состоянии о, если

Если триггер 38 находится в единичном состоянии, то после установления в нулевое состояние триггера 34,

рабатывается логическая 1, соответствующая сигналу отсутствия наруше25

устанавливает триггер 38 в состояние О, а дискриминатор 21 будет считать стартовые биты до девяти как информационные. Если триггер 38 находится в нулевом состоянии, то п сигналу с инверсного выхода триггера 34 сигнал О с выхода триггения, который через контакты 26 посту-2о сигнал 1 с его инверсного вьрсода пает на вход предыдущего устройства и на входы элементов И 9 и ИЛИ 10 блока последующего устройства, запрещая прохоясдение сигнала Отключить линию с элемента 12 через эле мент И 9 и разрешая прохождение через элемент ИЛИ 10 сигнала Разрешение передачи с выхода формирователя 75 последующего ycTpoitcTBa 3, на вход которого поступает сигнал с линии аналогичного устройства 3, через контакты 27 логическим О. Выходной сигнал формирователя-75 устройства 3 разрешает работу синхронизатора 74 устройства 3j|. Этот сигнал через такты 28, как сигнал Разрешение пе- редачи, поступает на устройство 3, . После того, как счетчик 35 сосчитает количество принимаемых битов до девя- tH, на входы элемента И-НЕ 36 поступают логические .1 (фиг. 4), с выхо- да которого О поступает на элемент НЕ-ИПИ 33. На выходе элемента НЕ 37 появляется О, по которому триггер 34 устанавливается в состояние 1, после чего сигналом с прямо- го выхода триггера 34 сбрасываются счетчики 35, закрывается счетчик 31 и открывается по первому входу элемент И-НЕ 32 (фиг. 4). После подсчета последних импульсов синхронизато- ра 74 (что соответствует второй половине битового интервала), в информационном сигнале должны появиться два бита Стоп, первый из которых сбрасывает счетчик 31 и устанавливает 55 в единичное состояние триггеры 38 и 39. Нарушения в линии могут ВОЗНИКНУТЬ в двух случаях: при передаче

ра 38 переписывается в триггер 39, с выхода.которого будут поступать 30 сигналы Нарушение соответствующих уровней. Сигнал с прямого выхода тр гера 4 закрывает элемент И 5, а сиг кал с инверсного выхода через элемент НЕ 6 и контакт 26 аналогично поступает в блок 1 как сигнал Нар шение, а также на входы элементов И 9 и ИЛИ 10 блока 1,, открывае элемент И 9 для прохождения сигнала с элемента 12. Через элемент ИЛИ 10 пройдет сигнал логической 1, sanp щаюций работу синхронизатора 74 и ч рез контакт 28 поступающий в линию как сигнал отсутствия разрешения пе редачи в блок 1| . Анализ сигнала Н рушение происходит в блоке 1, . Есл триггер 4 блока 1, также обнаружил нарушение, то его дальнейшая работа по анализу поступившего сигнала На рушение с линии через контакт 25 в элемент 11 не производится, так как элемент И 5 сигналом от триггера 4 закрыт

Если триггер 4 блока 1, не форми рует состояние Нарушение, то сиг С выхода элемента t1 через открытый элемент И 5 поступает на вход форми рователя 16 и на вход дискриминато .ра 13. Сигнал от блока 1j Разреше50

В первом случае счетчик 31 не закрывается по входу разрешения после приема девяти битов к продолжает считать импульсы синхронизатора 74. Дискриминатор 21 будет работать ана- логичным образом, а триггер 38 - в поступившей информации были только нулевые биты,

в состоянии 1, если в поступившей информации был хотя бы один единичный бит, или в состоянии о, если

В первом случае счетчик 31 не зарывается по входу разрешения после риема девяти битов к продолжает считать импульсы синхронизатора 74. искриминатор 21 будет работать ана- логичным образом, а триггер 38 - в поступившей информации были только нулевые биты,

Если триггер 38 находится в единичном состоянии, то после установления в нулевое состояние триггера 34,

устанавливает триггер 38 в состояние О, а дискриминатор 21 будет считать стартовые биты до девяти как информационные. Если триггер 38 находится в нулевом состоянии, то по сигналу с инверсного выхода триггера 34 сигнал О с выхода триггесигнал 1 с его инверсного вьрсода

сигнал 1 с его инверсного вьрсода

ра 38 переписывается в триггер 39, с выхода.которого будут поступать сигналы Нарушение соответствующих уровней. Сигнал с прямого выхода триггера 4 закрывает элемент И 5, а сиг- кал с инверсного выхода через элемент НЕ 6 и контакт 26 аналогично поступает в блок 1 как сигнал Нарушение, а также на входы элементов И 9 и ИЛИ 10 блока 1,, открывает элемент И 9 для прохождения сигнала с элемента 12. Через элемент ИЛИ 10 пройдет сигнал логической 1, sanpe-i щаюций работу синхронизатора 74 и через контакт 28 поступающий в линию как сигнал отсутствия разрешения передачи в блок 1| . Анализ сигнала Нарушение происходит в блоке 1, . Если триггер 4 блока 1, также обнаружил, нарушение, то его дальнейшая работа по анализу поступившего сигнала Нарушение с линии через контакт 25 в элемент 11 не производится, так как элемент И 5 сигналом от триггера 4 закрыт

Если триггер 4 блока 1, не формирует состояние Нарушение, то сигнал С выхода элемента t1 через открытый элемент И 5 поступает на вход формирователя 16 и на вход дискриминато- .ра 13. Сигнал от блока 1j Разреше

ние передачи через контакт 27 и формирователь 75 поступает на вход элемента ИЛИ 10 блока 1, сигналом логической 1 и с его выхода - на синхронизатор 74, запрещая выработку синхроимпульсов, и через контакт 28 - в линию, распространяясь в цепи в сторону, противоположную передаче информации.

С выхода формирователя 16 блока 1| импульс сигнала Нарушение поступает на вход регистра 15, в котором через элемент И 56 устанавливает в О триггер 57, выходной сигнал которого закрывает усилитель 62 блока 8. Обмотка 65 обесточивается и замыкает контакты переключателей 29 и 30. Кроме того, импульс с формирователя 16 запускает узел 14, в котором триггер 41 устанавливается в единичное состояние и начинается заряд конденсатора 42, время заряда которого определяет выдержку узла. При этом, с выхода узла 14 на входы злемен

Во втором случае, если неисправен передатчик 76 устройства 3, то биты

тов и 48 и 50 и триггера А7 дискрими-гз Стоп через приемник 73 устройства 3,

А1lj lt

натора 13 поступают логические О, 1 и О соответственно. В это же время на входы дискриминатора 13 поступает 1 с выхода элемента 11 и 1 с выхода элемента И 5. Сигналы на входах дискриминатора 13 подготавливают триггер 47 к срабатыванию, а на элементах 48-51 вырабатывают сигнал логического О. С прямого выхода триггера 47 подается логический О (фиг. 6), который через элемент НЕ 17 поступает в линию через контакт 24 сигналом логической 1, запрещающим отключение линии, а также на регистр 15. После переключения контактов 29 и 30 биты Стоп в обход блока 1, поступают на контакты 29 коммутатора 2, и через приемник 73 - на входы дискриминатора 21 и триггера А. После этого возможны- два случая. Первый - Нарушение зафик- сировано из-за неисправности прием30

35

40

45

поступают на информационный вход триггера 4 блока Ц и через элемент НЕ 40 устанавливают триггеры 38 и 39 в единичное состояние. В линию через элемент НЕ 6 и контакт 26 передается сигнал, соответствующий отсутствию нарушения, который через контакт 25 поступает на элемент 11 блока 1,, с выхода которого формируется логический О, запиракяций элемент И 5 и поступающий на вход дискриминатора 13. По логическому О на этом входе дискриминатора 13 на его втором выходе появляется сигнал 1, который через формирователь 19 и элемент И 20 поступает на вход регистра 15, где устанавливается сигнал Отключить линии (триггер 58 в нулевом состоянии), обмотки 66 и 67 реле обесточиваются и замыкают контакты 23, 24, 25, 24, 28, 27, подключив линии управления в обход уст ройстника 73 устройства второй - из-за ва 3j , классифицированного как не- неисправности передатчика 76 устройства 3 .

В первом случае биты Стоп не изменяют состояния приемника 73,

устройства 3, а следовательно, не устанавливают триггеры 38 и 39 в состояние 1 и сигнал Нарушение, при- нятьй через контакт 26 коммутато- 55 ра 2.(, не исчезает. После заряда конденсатора 42 в узле 14 блока 1,, г триггер 41 устанавливается в нулевое

исправное.

И в первом и во втором случаях, после снятия сигнала в линии Нарушение в линии Разрешение передачи появляется соответствующий сигнал, который черрз формирователь 75 устройства 3, элементы ИЛИ 10 блоков 1 неотключенных устройств- 3, разрешает продолжать работу синхрониза торов 74 .

j

o

состояние, на выходах узла 14 появляются сигналы обратной полярности, которые, поступая на входы дискриминатора 13, устанавливает триггер 47 в. состояние 1, что для блока 1 означает отключить линии, а На регистре 15 блока 1j устанавливается сигнал Подключить информационные линии. Последний поступает на синхро- вход триггера 57, который устанавливается в единичное состояние, включает обмотки 64 реле. Сигнал Отключить линии поступает на вход блока 1д через контакт 23, элемент 21, 5 открытый элемент И 9, элемент ИЛИ 20, на вход регистра 15 и сбрасывает трйг- геры 57 и 58 в нулевое состояние, тем самым отключая обмотки 65-67 реле. Таким образом, устройство 3 исключается из последовательной цепи связи как неисправное.

Во втором случае, если неисправен передатчик 76 устройства 3, то биты

0

з Стоп через приемник 73 устройства 3,

0

5

0

5

поступают на информационный вход триггера 4 блока Ц и через элемент НЕ 40 устанавливают триггеры 38 и 39 в единичное состояние. В линию через элемент НЕ 6 и контакт 26 передается сигнал, соответствующий отсутствию нарушения, который через контакт 25 поступает на элемент 11 блока 1,, с выхода которого формируется логический О, запиракяций элемент И 5 и поступающий на вход дискриминатора 13. По логическому О на этом входе дискриминатора 13 на его втором выходе появляется сигнал 1, который через формирователь 19 и элемент И 20 поступает на вход регистра 15, где устанавливается сигнал Отключить линии (триггер 58 в нулевом состоянии), обмотки 66 и 67 реле обесточиваются и замыкают контакты 23, 24, 25, 24, 28, 27, подключив линии управления в обход уст ройства 3j , классифицированного как не-

исправное.

И в первом и во втором случаях, после снятия сигнала в линии Нарушение в линии Разрешение передачи появляется соответствующий сигнал, который черрз формирователь 75 устройства 3, элементы ИЛИ 10 блоков 1 неотключенных устройств- 3, разрешает продолжать работу синхронизаторов 74 .

Формула изобретения

1 . Устройство для подключения абонентов к магистрали передачи данных, содержащее коммутатор, первые и вторые информационные входы и выхо- ды которого подключены к управляющим шинам магистрали передачи данных, и блок анализа состояния линии, вклю

чающий два элемента гальванической развязки, триггер состояния, два элемента И и два элемента ИЛИ, причем входы первого и второго элементов галъваничейкой развязки соединены соответственно с третьим и четвертым информационными выходами коммутатора, прямой выход триггера состояния.соединен с первым входом первого элемента И, первый вход и выход второго элемента И подключены соответственно к выходу первого элемента гальванической развязки и первому входу пер вого элемента ИЛИ, первый вход второго элемента ИЛИ соединен с выходом блокировки работы абонента, отличающееся тем, что, с целью расширения класса решаемых задач, устройства, в блок анализа состояния линии введены дискриминатор приема байта, дискриминатор нарушений, узел временной задержки, регистр управления коммутацией, три элемента НЕ, три формирователя импульсов и переключатель режима, причем Вокод регистра управления коммутацией подключен к адресному входу коммутатора, первый вход сброса - к выходу первого формирователя импульсов и входу узла временной задержки, группа выходов которого соединена с группой входов дискриминатора нарушений, информационный вход триггера состояния подключен к первому информационному выходу абонента и информационному входу дискриминатора приема байта, синхронизирующий вход которого соединен с выходом синхроимпульсов абонента, а выход - с синхровходом триггера состойния, инверсным входом подключенного к вторым входам вторых элементов И и ИЛИ и через первый эле мент НЕ - к третьему информационному входу коммутатора, четвертый информационный вход которого соединен с выходом второго элемента ИЛИ и вхо дом запрета синхроимпульсов абонента а пятые информационные вход и выход Соответственно с выходом второго элемента НЕ и входом готовности приема

10

15

25

04550 55

449910

абонента, вход третьего элемента НЕ через переключатель режима соединен с шиной логического нуля, а выход - с входом разрешения коммутатора и через второй формирователь импульсов - с установочным входом регистра управления коммутацией, син- хровход которого подключен к первому выходу дискриминатора нарушений и входу второго элемента НЕ, а второй вход сброса - к выходу первого элемента ИЛИ, вторым входом соединенного через третий формирователь импульсов с вторым выходом дискриминатора нарушений, первый вход которого соединен с выходом второго элемента гальванической развязки и вторым входом первого элемента И, а второй вход - с выходом первого элемента И 20 и входом первого формирователя импульсов, шестые информационные вход и выход коммутатора соединены соответственно с вторым информационным выходом и информационным входом абонента, а седьмые и восьмые информационные входы и выходы - соответственно с управляющими и информационными шинами магистрали.

2.Устройство по п. 1, о т л и- чающееся тем, что.дискриминатор нарушений содержит триггер, информационный вход которого подключен к шине логической единицы, а прямой выход является первым выходом дискриминатора, и элемент И-ИЛИ-НЕ, первый вход и выход которого являются соответственно вторым входом и вторым выходом дискриминатора, второй вход соединен с инверсным выходом триггера, вход сброса которого является первым входом дискриминатора, третий и четвертый входы элемента И-ШШ-НЕ

и сикхровход триггера подключены к группе входов дискриминатора.

3.Устройство по п. 1, отличающееся тем, что дискриминатор приема байта содержит два счетчика, триггер, инвё рсный выход которого является выходом дискриминатора,

а информационный вход соединен с шиной логического нуля, два элемента И- НЕ, элемент НЕ-ШШ и элемент НЕ, причем выход первого счетчика соединен с первым синхровходом первого счетчика, второй синхровход является синхронизирующим входом дискриминатора, разрешающий вход первого счетчика соединен с информационным входом дис11

криминатора и первым входом первого элемента И-НЕ, второй вход которого подключен к прямому выходу триггера и входам сброса первого и второго счетчиков, первый синхровход второго счетчика объединен с выходом первого разряда и соединен с первым входом второго элемента И-НЕ, а второй синхровход соединен с синхровходом тригЪ2г

4499

12

гера и выходом последнего разряда первого счетчика, выход последнего разряда второго счетчика подключен к второму входу второго элемента И-НЕ, выход которого и выход пс-рвого элемента И-НЕ подключены соответственно к первому и второму входам элемента НЕ- -ИЛИ,выходом подсоединенного через эле- ,мент НЕ к установочному входу триггера.

2i

Ннфоог оционные линии сВязи

SnpaSjiamutue линии с1язи

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

| Устройство для сопряжения электронной вычислительной машины с дискретными датчиками | 1985 |

|

SU1277126A1 |

| Устройство для сопряжения вычислительной машины с датчиками | 1988 |

|

SU1605245A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| ИНФОРМАЦИОННАЯ СИСТЕМА СВЯЗИ | 1991 |

|

RU2019851C1 |

| Устройство для сопряжения ЭВМ с абонентом по последовательному каналу связи | 1987 |

|

SU1442997A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для контроля субблока логического блока | 1986 |

|

SU1327111A1 |

Изобретение относится к вычислительной технике и может быть использовано, в многомашинных вычислительных комплексах повьшенной надежности, построеляых на базе локальной маг гистрали передачи данных, например, кольцевого типа. Целью изобретения является расширение класса решаемых задач за счет обеспечения возможности обнаружения неисправных устройств и отключения их от магистрали передачи данных. Поставленная цель достигается TeMj что в устройство, содержащее коммутатор и блок анализа состояния линии, включающий триггер состояния, два элемента гальванической развязки, два элемента И, два элемента ИЛИ, в блок анализа состояния линии введены дискриминатор приёма байта, дискриминатор нарушений, три формирователя импульсов, три элемента НЕ, регистр управления коммутацией и узел временной задержки. 2 з.п. ф-лы, 11 ил. (Л

Входная инфорн. бблок 1

СтортО 1 f)OJ 1 О О стоп

Выход „8 СГЗГ

ffUHX,

ВьигодО трае. j«

Вшодйо fnpuz.3f

Вы ход „J CT3S

Выход п 2 СТ35

Вылодп

СГ35

Выход б

СТ35

Выхода траб,38

Bb/xoffS три е. 39

Выход QS трцг.ЗЭ

Фт. t

Составитель В.Вертлиб Редактор И.Касарда Техред И.Попович Корректор Л.Пилипенко

4722/53

Тираж 671 . Подписное ВНИППИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| Устройство для сопряжения абонентов с электронной вычислительной машиной | 1982 |

|

SU1076895A1 |

| Многоканальное устройство для подключения абонентов к магистрали | 1983 |

|

SU1104497A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Регистрационный ящик | 1918 |

|

SU983A1 |

Авторы

Даты

1986-08-30—Публикация

1984-07-27—Подача