информационных входов второго регист. вторые входы которых соединены с пыра соединена с выходами элементов ходами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ .ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы,второй группы.

1129615

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электронной вычислительной машины | 1981 |

|

SU1019451A1 |

| Система для контроля микропроцессорных устройств | 1983 |

|

SU1228108A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Устройство для контроля магистралей в ЭВМ | 1981 |

|

SU970376A1 |

| Устройство для сопряжения процессора с группой устройств памяти | 1986 |

|

SU1348843A1 |

| Устройство для отладки микропроцессорной системы | 1987 |

|

SU1453408A1 |

| Логический анализатор | 1983 |

|

SU1170458A1 |

| Запоминающее устройство с исправлением ошибок | 1980 |

|

SU955207A1 |

| Устройство для контроля электромонтажа | 1989 |

|

SU1688263A1 |

| Устройство для контроля управляющей ЭВМ | 1988 |

|

SU1619280A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДАННЫХ ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ ПРИПРЕРЬВАНИЯХ ПИТАНИЯ, содержащее оперативный запоминающий блок, блок основного питания,, блок резервного питания, ключевой элемент и конденсатор, причем первый и второй входы ключевого элемента соединены соответственно с первыми выходами питания блоков основного и резервного питания, вторые выходы питания которых соединены с шиной нулевого потендаала, выход ключевого элемента соединён с входом питания оперативного запоминающего блока и черезконденсатор - с шиной нулевого потенциал.а, группа адресных входов оперативного запоминающего блока является группой адресных входов устройства, группа входов-выходов данных - группой входов-выходов данных устройства, группа управляющих входов-выходов оперативного запо1 1инающего блока и первый и второй выходы предупредительных сигналов блока основного питания образуют группу управляющих входов-выходов устройства, отличающееся тем, что, с целью повьпиения достоверности контроля сохранности информации, в устройство введен блок контроля, содержащий дешифратор, элемент задержки, элемент ИЛИ-НЕ, два элемента НЕ, два элемента И, два регистра, группу элементов И и две группы элементов ИСКЛЮЧАЩЕЕ ИЛИ, причем группа информационных входов дешифратора соединена с группой адресных входов устройства, а управляющий вход - с шиной строба адреса устройства, выходы элементов И группы, информационные входы первого регистра и первая группа входов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы подключены к группе входоввыходов данных устройства, первый . i вход первого элемента И соединен с шиной режима устройства и через пер(Л вый элемент НЕ - с первым входом второго элемента И, выход элемента ... ИЛИ-НЕ соединен с шиной строба данных устройства и через второй элемент НЕ с вторьм входом первого элемента И, второйвход второго элемента И сое.- динен с первым выходом дешифратора и с третьим входом первого элемента И, выход которого соединен с синхрониto зирующим входом первого регистра, со О) группа выходов которого соединена с первыми входами элементов ИСКПКНАЮЩЕЕ ИЛИ второй группы, вторые входы :д которых соединены с группой выходов второго регистра и с первыми входами элементов И группы, вторые входы которых сЬединены с вторым выходом дешифратора и через элемент задержки - с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с третьим выходом дешифратора и с входом сброса второго регистра, синхронизирующий вход которого соединен с выходом второго элемента И, группа

Изобретение относится к цифровой вычислительной технике и может быть использовано в системах, сохраняющих оперативную информацию при отключе,НИИ основного питания электронной

вычислительной машины (ЭВМ), являющейся ядром системы.

Известно устройство для обеспечения сохранности и контроля данных ЭВМ содержащее блок питания, подключеннью к оперативному запоминающему устройству (ОЗУ) и через ключ - к процессору, соединенному с ОЗУ посреством группы однонаправленных и днунаправленных связей L1J,

При включении питания процессор этого устройства сравнивает содержи- мое определенной (тестовой) зоны оперативной памяти с содержимым определенной зоны постоянного запомина щего устройства ЭВМ При положительных результатах сравнения предполагается, что информация в остальных зонах ОЗУ не исказилась в период отключения питания процессора. Однако это предположение не дает полной гарантии сохранности данных. Кроме того, часть ОЗУ, тем большая, чем выше требуемая достоверность данных, тратится на хранение тестовой информации и не может быть использована потребителем.

Наиболее близким по технической сущности к предлагаемому является устройство для обеспечения сохранности и контроля данных ЭВМ при ; прерываниях питания, содержащее ОЗУ блок основного питания, блок резервного питания ключевой элемент, конденсатор, генератор случайного числа, блок обработки и терминал, причем входы ключевого элемента соединены с первым, выходом блока основног питания и с первым полюсом блока резервного питания, второй полюс которого заземлен, выход ключевого элемента, соединен с входом питания ОЗУ через конденсатор - с. шиной земли.

группа адресных входов ОЗУ является группой адресных входов устройства, . группа входов-выходов данных ОЗУ является группой входов-вькодов данных устройства, группа управляющих входов-выходов ОЗУ - группой управляющих входов-выходов устройства, второй и третий выходы блока основного питания соединены с первым и вторым управляющими входами-выходами устройства, четвертый выход блока основного питания является выходом основного питания устройства, пятый выход блока основного питания зазем.лен, выход генератора случайного числа подключен к входу блока обработки выход которого соед1 нен с входом терм-инала, адресные, информационные и управляющие входы блока обработки соединены с соответствующими входамивыходами ОЗУ С2;.

Недостатком этого устройства является низкая достоверность контроля, так как признаком сохранности данных является наличие в двух определенных ячейках ОЗУ кодов, взаимно дополняющих друг друга.Информация в остальных ячейках не контролируется. Вследствие этого устройство позволяет установить лишь факт полной потери информации, например, при разряде резервной батареи питания ОЗУ;

Цель изобретения - повышение достоверности контроля сохранности информации.

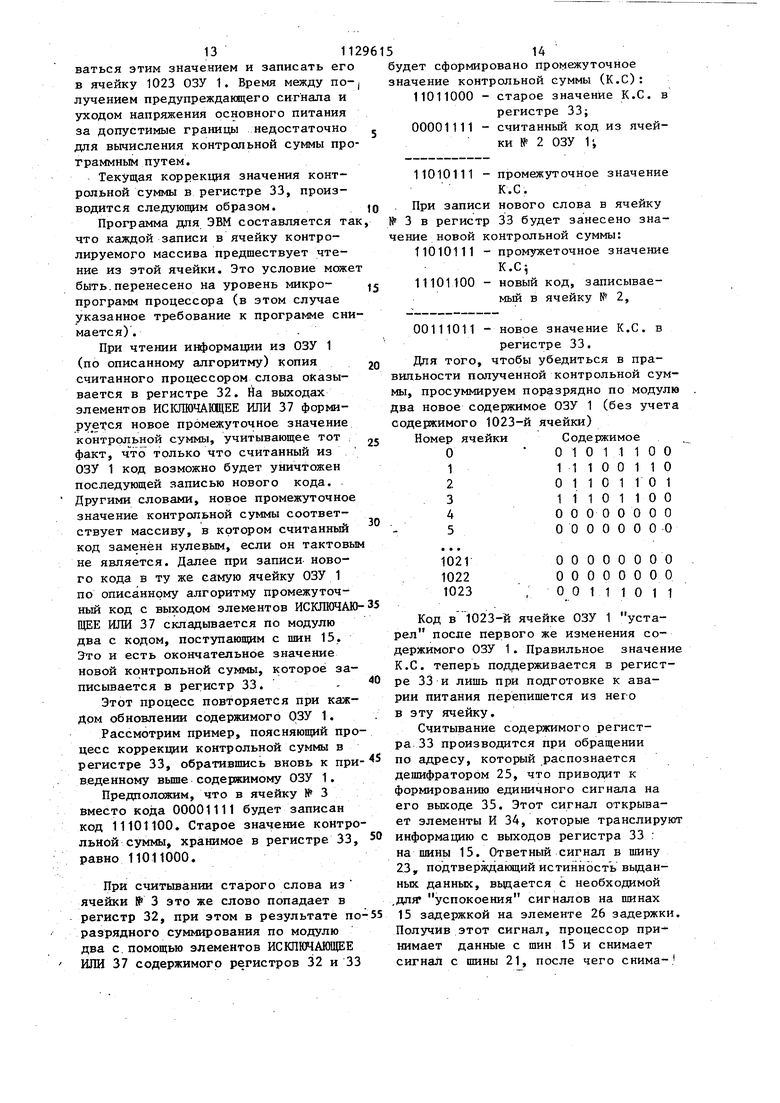

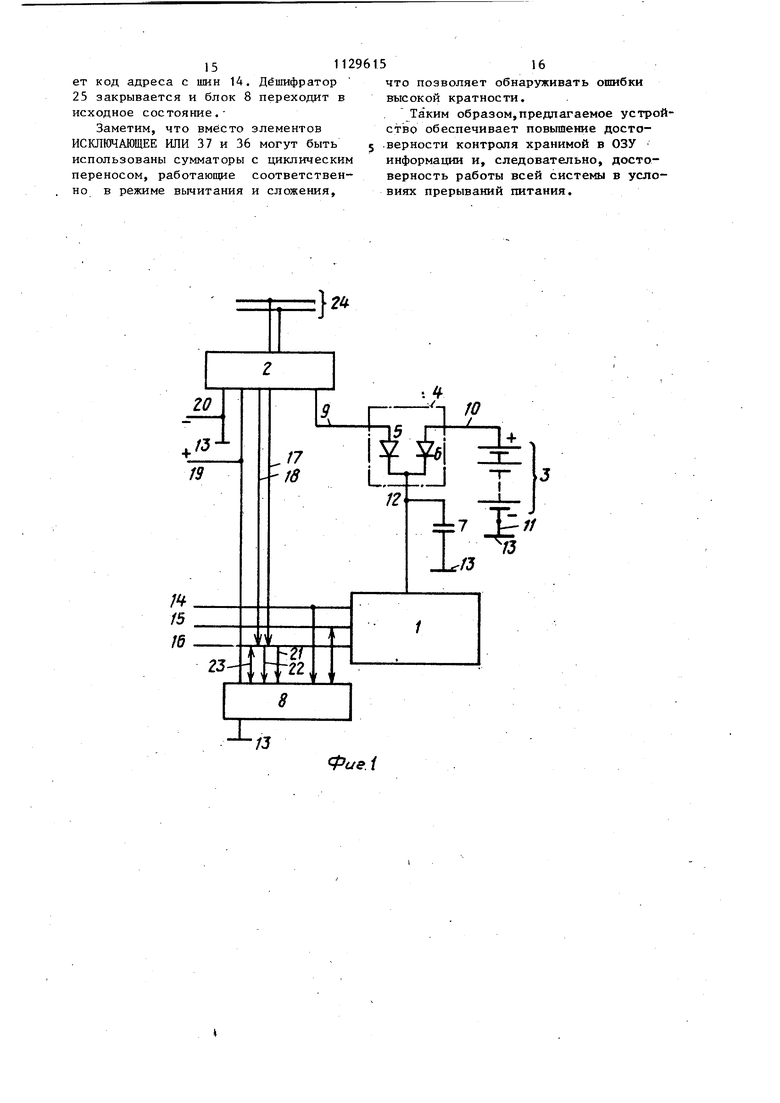

Поставленная цель достигается тем, что в устройство, содержащее оперативньй запоминающий блок, блок основного питания, блок резервного питанин, ключевой элемент и конденсатор, причей первый и второй входы ключевого элемента соединены соответственно с первыми выходами питания блоков основного и резервного питания, вторые выходы питания которых соединены с шиной нулевого потенциала, выход ключевого элемента соеданен с входом питания оперативного запо311минающего блока и через конденсатор с шиной нулевого потенциала, группа адресных входов оперативного запоминающего блока является группой адрес ных входов устройства, группа входов выходов данных - группой входов-выхо дов данных устройства, группа управляющих входов-выходов оперативного запоминающего блока и первый и второй выходы предупредительных сигнало блока основного питания образуют группу управляющих входов-выходов устройства, введен блок контроля, содержащий дешифратор, элемент задержки, элемент ИЛИ-НЕ, два элемента НЕ, два элемента И, два регистра, группу элементов И и две группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем группа информационных входов дешифратора соединена с группой адресных входов устройства, а управляющий вход - с шиной строба адреса уст ройства, выходы элементов И группы, информационные входы первого регистра и первая группа входов элементов ИСКЛЮЧАЩЕЕ ИЛИ первой группы подключены к группе входов-выходов данных устройства, первый вход первого элемента И соединен с шиной режима устройства и через первый элемент НЕ с первым входом второго элемента И, выход элемента ИЛИ-НЕ соединен с шиной строба даннькустройства и через второй элемент НЕ - с вторым входом первого элемента И, второй вход второ го элемента И соединен с первым выхо дом дешифратора и с третьим входом первого элемента И, выход которого соединен с синхронизирующим входом первого регистра, группа выходов которого соединена с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй руппы, вторые входы которых соединены с группой выходов второго регист ра и с первыми входами элементов И группы, вторые входы которых соединены с вторым выходом дешифратора и через элемент задержки - с первым вх дом элемента ИЛИ-НЕ, второй вход которого соединен с третьим выходом, дешифратора и с входом сброса второго регистра, синхронизирующий вход которого соединен с выходом в гррого элемента И, группа информационных вх дов второго регистра соединена с выходами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, вторые входы которых соединены с выходами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы. 5 На фиг. 1 приведена функциональная схема предлагаемого устройств.а на фиг. 2 - функциональная .схема блока контроля; на фиг., 3 - структура адресных, информационных, и управляющих входов-выходов устройства на фиг. 4 - функциональная схема узла формирования предупреждающих сигналов; на фиг. 5 - временные диаграммы сигналов на входах и выходах блока питания при выключении и вклю- чении первичного питания на фиг, 6 (а, б) - алгоритмы работы ЭВМ, использующей предлагаемое устройство, при выключении (а) и включении (б) первичного питания, Устройство (фиг, 1) содержит оперативный запоминаюш;ий блок (ОЗУ) 1, Ьлок 2 основного питания, бл.ок зервного питания,ключевой элемент 4, который может состоять, например, из диодов 5 и 6, конденсатор 7, блок 8 контроля и шины 9-13, Шины 9 и 10 соединяют входы ключевого элемента 4 с первыми выходами питания (например, выходами положительной полярности) блоков 2 и 3 для питания ОЗУ 1, шина 11 соединяет второй выход (выход отрицательной полярности) блока 3 с шиной 13 нулевого потенциала. Шина 12 подключена к выходу ключевого элемента 4, входу питания ОЗУ. На фиг, 1 показаны также щины 14 группы адресных входов устройства, шины 15 группы входов-выходов данных устройства, щины 16-18 группы управляющих входов-выходов устройства, шина 19 положительной полярности блот ka 2, предназначенные дпя питания блока 8 устройства и всех других устройств системы, подключенных к шинам 14-18 и не показанных на фиг. 1, шина 20 отрицательной полярности блока 2, а также шина 21 строба адреса, шина 22 режима обращения.и шина 23 строба данных .которые входят в состав шин 16 группы управляющих входов-выходов устройства. Блок 2 соединен с шинами 24 первичного питания. Блок 8 контроля (фиг. 2) содержит дешифратор 25, элемент 26 задержки, элемент ИПИ-НЕ 27, элементы НЕ 28 и 29, элементы И 30 и 31, регистры 32 и 33, элементы И 34 группы, соединенные шиной 35 с вторым выходом дешифратора 25, элементы ИСКПЮЧАНЩЕЕ ИЛИ 36 и 37 первой и второй групп. На фиг. 2 обозначены также шины 38 первого выхода дешифратора 25, шина

S1

39 выхода первого элемента И 30 и ши на 40 третьего выхода дешифратора 25

Структура адресных, информационных и управляюпщх входов-выходов устройства в развернутом виде показана на фиг. 3,

Шины 14 адресных входов устройства предназначены для передач двоичных кодов, определяющих адреса чеек памяти ОЗУ 1, а также адреса,

на которые настроен дешифратор 25 блока 8. Линии группы 14 подключены к адресным входам блоков 1 и 8.

Шина 15 входов-выходов данных преназначена для передачи информащшнны сигналов в ту или другую сторону в зависимости от конкретной ситуации. Эта группа может включать в себя, например, 8 линий. Линии группы 15 подключены к информационным входамвыходам блоков 1 и 8.

Шина 16 управляющих входов-выхошов устройства содержит пять линий: 17, 18, 21, 22 и 23, Шина 17 предназначена для передачи сигнала предупреждения об аварии питания от блока 2 питания в процессор или в любое другое устройство, заинтересованное в спасении своего состояния в ОЗУ 1 для последующего его воестановления после восстановления питания. Шина 18 предназначена для передачи сигнала Последнее предупреждение об аварии питания от блока 2 питания ко-всем заинтересованным устройствам,.которые расценивают его как сигнал общего сброса. Шина 18 подключена к управляющему входу разрешения работы ОЗУ 1.

.

Шина 21 предназначена для передачи сигнала подтверждения истинности адреса, установленного процессором или каким-либо другим устройством на шинах 14. Шина 22 предназначена ,цля передачи управляющего сигнала Запись-чтение, который задается извне и определяет один из двух возможньк режимов обмена. Шина 23 предназначена для передачи ответного сигнала, который говорит о выполнении предписанной операции. При чтении этот сигнал подтверждает истинность данных, установленных на шинах 13, а при записи уведомпяет процессор Ш1И другое устройство в том, что код шин 15 принят в ячейку памяти или регистр.

На фиг. 4 фрагмент схемы блока 2 питания в части, которая обеспечивает формирование предупреждающих сигналов. Этот формирователь содержит выпрямитель 41, фильтр 42, дискриминаторы 43 и 44 уровня и выходные каскады 45 и 46. Входы выпрямителя 41 подключены, к шинам 24 первичного питания, а его выход через фильтр 42 - к входам параллельно включенных дискриминаторов 43 и 44. Вход выходного каскада 45 соединен с выходом дискриминатора 43, а вход выходного каскада 46 - с выходом дискриминатора 44. Выходы выходных каскадов 45 и 46 подключены соответственно к шинам 18 и 17.

Выходной каскад 45 (46) содержит р-ц-р транзистор 47,Г)-р-п транзистор 48, базовый резистор 49 и нагрузочны резистор 50..

База транзистора 47 является входом выходного каскада 45 (46), а его эмиттер, объединенный с коллектором транзистора 48 и через резистор 50 подключенный к шине 51 положительного питания,- выходом выходного каскада. Коллектор транзистора 47 соединен с базой транзистора 48 и через резистор 49 - с эмиттером транзистЪр 48 и с шиной 13 нулевого потенциала (земпи).

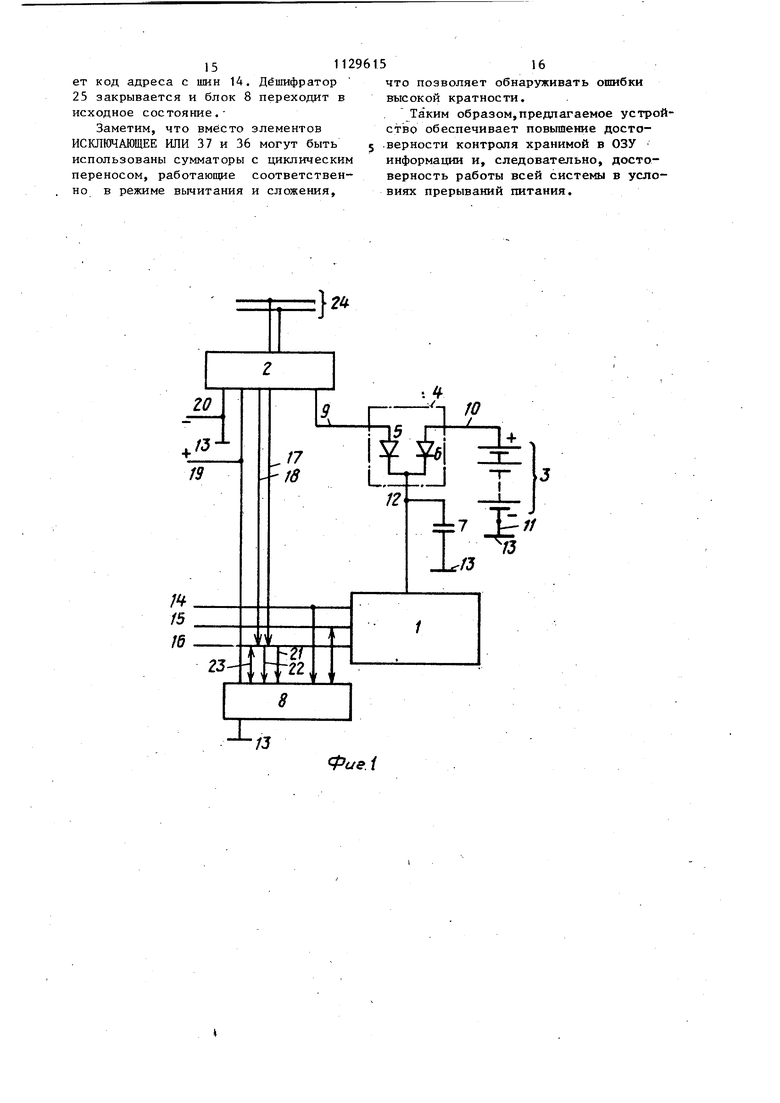

На фиг. 5 показаны временные диаграммы сигналов на входах и выходах блока 2 питания. Эпюра 52 отображает лроцесс выклюйочия и включения пер- вичной питающей сети (например, 220 В, 50 Гц)i эпюра 53 - сигнал на выходе фильтра 42 эпюры 54 и 55 .сигналы на шинах 17 и 18; эпюра 56 потенциал на шине 9 (19) вторичного питания (например, +9В, +5В).

В момент времени Тд происходит выключение первичного питания (эпюра 52) , В моменты времени Т и потеяциал на выходе фильтра 42 (эпюра 53) уменьшается соответственно до порогов срабатывания дискриминаторов 43 и 44, в результате чего на шинах 17 и 18 (эпюры 54 и 55) последовательно формируются низкие потенциалы. В момент времени Т, потенциал шины 9(19) выходит за допустимую нижнюю границу и к моменту Т. снижается практически до нулевого значения (эпюра 56).

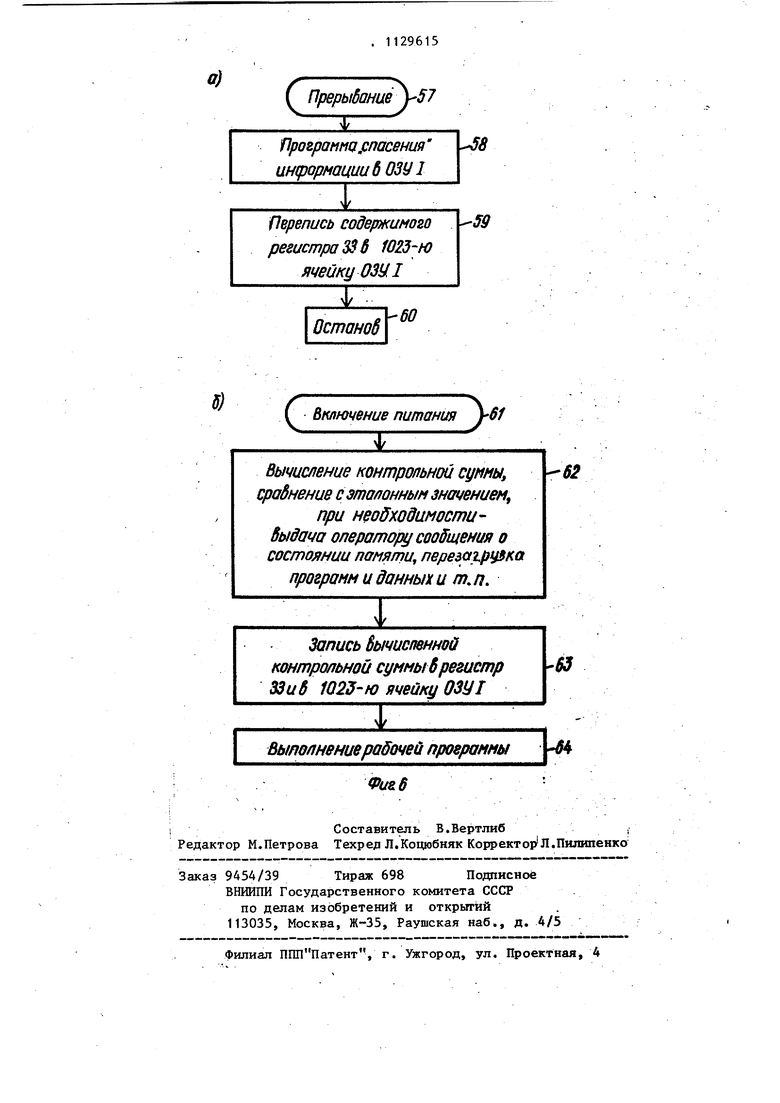

В момент времени Tj включается первичное пига1ше, в момент Т, вторичное питание достигает нужного уровня, после чего в моменты времен T-J и Тд срабатывают дискриминаторы 43 и 44, а затем к моменту времени Т„ потенциал на выходе фильтра 42 достигает исходного значения. Выход ные каскады 45 и 46 обеспечивают по держание на шинах 18 и 17 низких по тенциалов в период отсутствия первичного питания () нашего ус ройства даже при попытке чужого у ройства (питание которого осталось включенным) создать на этих шинах высокие потенциалы. В этом случае транзисторы 47 и 48 открываются и ток от чужого источника стекает через них на шину 13. На фиг. 6 показаны примеры укруп ненных блок-схем алгоритмов работы ЭВМ, использующей предпагаемое устройство, при выключении (а) и включении (б) первичного питания. При выключении первичного питания ЭВМ прекращает выполнение текущего задания и по сигналу прерывания (отрицательный перепад потенциала на шине 17) переходит к программе спасения необходимой информации в ОЗУ 1 (см. указатель 57 события и блок 58 на фиг. 6а). После этого содержимое регистра 33 бло ка 8 программно переписывается, например, в 1023-ю ячейку ОЗУ 1 (блок 59) и далее ЭВМ, встретив команду Останов (блок 60), прекращает работу, ожидая снятия вторичного пи тания . При включении питания (указатель 61 события) производится вычисление контрольной суммы содержимого ОЗУ 1 и сравнение полученной суммы с эталонным значением, хранимым в одной из ячеек (например, в ячейке 1023), этого же ОЗУ 1 (см. блок 62). При о сутствии искажений информации суммы должны совпасть, в противном слу чае требуется вмешательство оператора, перезагрузка или другие действия Далее (блок 63) выполняется запись вычисленной контрольной суммы в регистр 33 и в 1023-ю ячейку ОЗУ 1 После этого производится переход к выполнению рабочей программы .(блок 64 Устройство предназначено для обе печения сохранности данных в ОЗУ 1 при обесточивании блока 2 основного питания с возможностью последующей проверки сохранности данных при восстановлении основного питания. Работа устройства при обеспечении сохранности данных осуществляется следующим образом. При исчезновении питающего напряжения на шинах 24 первичного питания блок 2 в течение некоторого времени, например в течение времени, не меньшего 7 мс, поддерживает стабилизированные напряжения на шинах 9 и 19 за счет энергии, ранее накопленной на конденсаторах фильтра выпрямленного напряжения. При исчезновении питающего напряжения на шинах 24 первичного питания блок 2, кроме того, формирует на шине 17 сигнал в виде низкого потенциала, который поступает в шины 16. Этот сигнал поступает в процессор ЭВМ (точнее, в любое активное устройство, заинтересованное в спасении своего состояния в ОЗУ 1) и , предупреждает его о том, что питание исчезает через несколько (в нашем примере не менее чем через семь) миллисекунд.. Получив этот сигнал, процессор ЭВМ переходит в режим прерыван1 я при котором выполнение текущего заданий., прекращается и все параметры, необходимые для последующего возобновления вьшолнения этого задания /упрятываются в определенную зону ОЗУ 1. После этого управление передается в определенную ячейку памяти, т.е. совершается переход к прерьшакицей проrpai-iMe. Прерывающая программа в данном случае возможно продолжит подго;товку к выключению вторичного пита;ния.0на может опросить состояние таймера и зафиксировать в определенной ячейке ОЗУ 1 время исчезновения напряжения (в часах, минутах и секундах), подать иа управляемые объекты сигналы выключения и т.д. Эта программа должна завершиться командой Останов до истечения, например, 6 мс от начала ее работы. Через некоторое время после исчезновения питающего напряжения на шинах 24 первичного питания, наприер через 6,5 мс, блок 2 формирует низкий потенциал на линии 18 который поступает в шину 16 и является последним предупреждением перед уходом питающего напряжения на. шинах 9 и 19 за допустимые границы I (запас в нашем примере составляет 0,5 мс). К этому моменту времени ,все заинтересованные устройства спасли свою жизненно важную информацию в .соответствующих зонах ОЗ 1 и находятся в состоянии Останов Сигнал с шины 18 поддерживает все устройства ЭВМ в сброшенном состоянии и закрывает ОЗУ 1 по входам, та что хаотические сочетания сигналов на шинах 14, 15 и 16 после истечения 7 мс уже не смогут привести к и кажениям содержимого ОЗУ 1, питание которого производится от блока 3 через диод 6. Конденсатор 7 сглаживает переходный процесс переключения ОЗУ 1 с основного питания на ре зервное. В режиме хранения питание ОЗУ 1 может осуществляться от источ ника со значительно более низким напряжением, чем номинальное напряж ние питания в рабочем режиме (напри мер, 4В вместо 9В). Обе ;точенное состояние блока 2 может ,:у1иться достаточно дол г о, напре мер 5 сут, если емкость резервного блока 3 питания обеспечивает поддер жание приемлемого напряжения питани Ток, потребляемый от блока 3 при ис пол.:юваиии в ОЗУ 1 статических КМО БИС, составляет единицы миллиампер. Низкий потенциал на шине 18 обеспечивает при этом нечувствительность ОЗУ 1 к-разного рода помехам, которые могут возникать на шинах 14, 15 и 16 в период спада, отсутствия и последующего нарастания напряжений питания на выходах блока 2. После подачи напряжения на шины 24 первичного питания блок 2 выдает стабилизированные напряжения н шины 9 и 19, продолжая поддерживать низкие потенциалы на шинах 17 и 18 в течение, например, 1 с. Затем эти сигналы снимаются, что приводит к : разблокировке ОЗУ 1. Одновременно с этим пускается процессор ЭВМ с фиксированного адреса (если активных устройств несколько, то каждое из них пускается по своей программе). Процессор извлекает из ОЗУ 1 всю ранее упрятанную информацию и ис пользует ее для возобновления выпол нения задания, прерванного в связи с выключением питания. При наличии основного питания энергия от блока -3 не потребляется, поскольку диод б закрыт. 5|о Описанный механизм защиты ОЗУ 1 1 от разрушения информации при отключении основного питания не гарантирует, однако, отсутствия ошибок, возникших, например, из-за помех, наведенных извне чрезмерного, разряда блока 3, или по другим причинам. Поэтому возникает задача проверки правильности данных в ОЗУ 1 после восстановления основного питающего напряжения. Такая проверка вьшолняется путем вычисления контрольной суммы всех массива, хранившегося в ОЗУ 1, и сравнения полученной суммы с эталонным значением, которое хранится в одной из ячеек этого же ОЗУ. Эта процедура выполняется программным путем после включения основного питания и поэтому не требует специальных аппаратных средств. При обнаружении несовпадения контрольной суммы с эталонным значением в результате искажения информации (или при первоначальном включении питания) оператору ЭВМ может быть выдано соответствующее сообщение в виде, например, печатного текста. При совпадении контрольной суммы с эталоном программа оперирует с данными, предполагая их достоверность. Поскольку время, отведенное на подготовку к выключению питания, недостаточно для вычисления эталонного значения контрольной программным путем (это время в нашем примере составляет 6,5 мс), блок 8 хранит текущее значение контрольной суммы и вcяkий раз при изменении информации в ОЗУ 1 автоматически корректирует это значение. В дальнейшем для определенности (Предполагается, что контрольная сумма образуется путем поразрядного суммирования по модулю два всех кодов контролируемого массива. Пусть, например, контролируемая область ОЗУ 1 ссЗСтавляет 1024 8-разрядных яч€;ек, в которых записана следующая информация:Содержимое Номер ячейки О 1 2 3 4 5 010 1 1 11100 О 1. 1 О 1 00001 00000 00000 о о о о о о 11 о 1-1 00 о 111 В ячейке № 1023 ОЗУ 1 записан код представляющий собой поразрядною сум му по модулю два кодов, располфсенных в ячейках 0-1022. Как уже отмечалось, при включении питания процессор ЭВМ программным пу тем вычисляет значение контрольной суммы и сравнивает ее с кодом, запи- санным в ячейке 1023, При первом вкл чении устройства совпадения не будет (с большой вероятностью), поскольку предыстория отсутствует и инфор мация в ОЗУ 1 имеет случайный харак.тер. Полученное в результате суммиро вания значение контрольной суммы в л бом случае,т.е. независимо от резуль тата сравнения, заносится в регистр 33 блока 8. С целью экономии аппаратуры непо- средственный доступ с шин 15 в регистр 33 не предусмотрен, поэтому запись в регистр 33 вьтолняется в четьфе этапа. 1.Процессор ЭВМ записывает в ячейку 1023 ОЗУ 1 нулевой код. 2.Процессор ЭВМ считывает из ячейки 1023 ОЗУ 1 записанный нулевой код. При выполнении этой команды на шине 14 устанавливается код, соответствующий указанной ячейке ОЗУ 1. Истинность установленного на шине 14 адреса подтверждается нулевым сигналом на Ш1не 21, который разрешает работу дешифратора 25. Последний реагирует на обращение к любой ячейке ОЗУ 1 вьдачей единичного сигнала на шину .38. ОЗУ 1 в то же время опознает адрес на шине 14 и производит требуемую операцию вьщачи содержимого ячейки 1023 (нулевого кода) в шины 15. Истинность установленных на шинах 15 данных подтверждается нулевым сигналом, поступакнцим 1 на шину 23. Элемент ИЛИ-НЕ 27с открытым коллектором в данхождению ответного сигнала по шин(ё ,23 из ОЗУ 1 в процессор ЭШ. Этот же сигнал подслушивается элементом НЕ 29, в результате чего на входах элемента И 30 собираются три единичнЬк сигнала (сигнал на шине 22 при чтении рдвен единице). Срабатывание элемента И 30 вызывает появление положительного фронта сигнала на сиихронизующем входе регистра 32, который принимает нулевой код с шин .15. Таким образом, выполнение дан1512ной команды процессором сопровождается обнулением регистра 32. 3.Процессор ЭВМ выполняет команду записи информации в некоторую не существующую ячейку памяти. Адрес этой ячейки, выставленный на шинах 14 и сопрово9кдаемь й нулевым сигналом на шине 21, опознается дешифратором 25, в результате чего на шине 40 формируется сигнал логической единицы. Этот сигнал сбрасывает регистр 33.. Кроме того,сигнал, пройдя через элемент ИЛИ-НЕ 27, вцдается) по шине 23 в процессор ЭВМ, оповещая его о том, что адрес опознан и об- мен закончен. Получив этот сигнал, процессор снимает нулевой сигнал с шины 21 и адресные сигналы с шин 14. Дешифратор 25, в свою очередь, снимает сигнал с шины 40, прекращая воздействие на вход сброса регистра 33 иснимая ответный сигнал с шины 23. Таким образом, выполнение данной команды приводит к обнулению регистра 33. 4.Процессор ЭВМ выполняет команду записи вычисленной ранее (и возможно не совпавшей с хранимым эталоном) контрольной суммы в ячейку fr 10.3 ОЗУ 1. Дешифратор 25 при обращении к ОЗУ 1 формирует сигнал на шине 38. В данном случае сигнал на шине 22 имеет нулевое значение, поэтому срабатывает элемент НЕ 28, элемент И 31 и информация с выходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 36 принимается в ре-, гистр 33 по переднему фронту сигнала на сихронизирующем входе этого регистра. Эта И1«} ормация в точности со - ответствует той, которая установлена на шинах 15, т.е. вычисленной контрольной сумме, поскольку на всех выходах элементов ИСКЛЮЧАЮЕЦЕЕ ИЛИ 37 (до приема новой информации в регистр 33) сформированы логические нули. Таким образом, в результате выполнения цепочки из четырех указанных команд, в регистр 33 занесено правильное значение контрольной суммы. В дальнейшем, по мере обновления содержимого ОЗУ 1, значение контгрольной суммы в регистре 33 постоянно корректируется с тем, чтобы в критический момент (при получении предупреждения об аварии питания по шине 17) процессор после завершения всех необходимых процедур мог воспользоваться этим значением и записать его в ячейку 1023 ОЗУ 1. Время между получением предупреждакяцего сигнала и уходом напряжения основного питания за допустимые границы недостаточно , для вычисления контрольной суммы программным путем.

Текущая коррекция значения контрольной суммы в регистре 33, производится следующим образом.10

Программа дпя ЭВМ составляется так, что каждой записи в ячейку контролируемого массива предшествует чтение из этой ячейки. Это условие может быть.перенесено на уровень микро- j программ процессора (в этом случае указанное требование к программе снимается) ..

При чтении информации из ОЗУ 1 (по описанному алгоритму) копия 20 считанного процессором слова оказывается в регистре 32. Йа выходах элементов ИС1СЛЮЧАКЩЕЕ ИЛИ 37 формируется новое промежуточное значение контрольной суммы, учитывающее тот ; факт, что только что считанный из ОЗУ 1 код возможно будет уничтожен последующей записью нового кода. Другими словами, новое промежуточное значение контрольной суммы соответствует массиву, в котором считанный код заменён нулевым, если он тактовым не является. Далее при записи нового кода в ту же самую ячейку ОЗУ 1 по описанному алгоритму промежуточный код с выходом элементов ИСКЛЮЧАЮ-35 ЩЕЕ ИЛИ 37 складывается по модулю два с кодом, поступающим с шин 15. и есть окончательное значение новой контрольной суммы, которое записывается в регистр 33. Этот процесс повторяется при каждом обновлении содержимого ОЗУ 1.

Рассмотрим пример, поясняющий процесс коррекции контрольной суммы в регистре 33, обративщись вновь к приведенному вьше содержимому ОЗУ 1.

Предположим, что в ячейку № 3 вместо кода 00001111 будет записан код 11101100. Старое значение контрольной суммы, хранимое в регистре 33, 50 равно 11011000.

При считывании старого слова из ячейки № 3 это же слово попадает в регистр 32, при этом в результате по-55 разрядного суммирования по модулю два с. помощью элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 37 содержимого регистров 32 и 33

будет сформировано промежуточное значение контрольной суммы (К.С): 11011000 - старое значение К.С. в

регистре 33;

00001111 - считанный код из ячейки № 2 ОЗУ U

11010111 - промежуточное значение

К.С.

. При записи нового слова в ячейку № 3 в регистр 33 будет занесено значение новой контрольной суммы:

11010111 - промужеточное значение

К.С

11101100 - новый код, записываемый в ячейку № 2,

00111011 - новое значение К.С. в регистре 33.

Для того, чтобы убедиться в правильности полученной контрольной суммы, просуммируем поразрядно по модулю два новое содержимое ОЗУ 1 (без учета содержимого 1023-й ячейки)

Номер ячейки Содержимое

0 01011100

111100110

201101101

311101100

400000000

500000000

00000000 00000000 00111011

Код в 1023-й ячейке ОЗУ 1 устарел после первого же изменения содержимого ОЗУ 1. Правильное значение К.С. теперь поддерживается в регистре 33 и лишь при подготовке к аварии питания перепишется из него в эту ячейку.

Считывание содержимого регистра 33 производится при обращении по адресу, который распознается дешифратором 25, что приводит к формированию единичного сигнала на его выходе 35. Этот сигнал открывает элементы И 34, которые транслируют информацию с выходов регистра 33 : на шины 15. Ответный сигнал в шину 23, подтверждающий истинность вьщанных данных, вьдается с необходимой ,для успокоения сигналов на шинах 15 задержкой на элементе 26 задержки. Получив этот сигнал, процессор принимает данные с шин 15 и снимает сигнал с шины 21, после чего снима-j 112 ет код адреса с шин 14. Дешифратор 25 закрывается и блок 8 переходит в исходное состояние. Заметим, что вместо элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 37 и 36 могут быть использованы сумматоры с циклическим переносом, работающие соответственно в режиме вычитания и сложения. 16 что позволяет обнаруживать ошибки высокой кратности. Таким образом,предлагаемое устройство обеспечивает повьппение досто.верности контроля хранимой в ОЗУ информации и, следовательно, достоверность работы всей системы в условиях прерываний питания.

tri (t i. bi

Н локу2

Y 5локу 8

Н S/toffy i Фие.Ъ

:}

2 фрогме/ffrr Блока 2

/ други уз/гам

А5

п

50

cSii

i

-

wh

/J

Li.

17Tt T,rt7,r

ТвТ,7,Т,Т,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СПОСОБ ОЧИСТКИ СТОЧНЫХ ВОД ОТ ЦИАНИДОВ И РОДАНИДОВ | 1989 |

|

RU2013378C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЕТОПОГЛОЩАЮЩЕЙ МАТРИЦЫ | 1991 |

|

RU2047927C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-15—Публикация

1983-09-12—Подача