1

Изобретение относится к устройствам для определения времени запаздывания по положению максимума взаимнокорреляционной функции и может использоваться в системах автоматического управления, измерительной аппаратуре и т.п. объектах.

Известен корреляционный измеритель времени запаздывания, содержа щий блок управления, блок задержки, первый и второй блоки умножения, первый и второй блоки усреднения и блок вычитания, первый и второй входы и выход которого соединены соответственно с выходами первого и второго блоков усреднения и входом блока управления, выход которого соединен с управляющим входом блока задержки, информационный вход которого соедине с первым входом устройства, второй вход которого соединен с первыми входами блоков умножения,вторые входы которых соединены с выходами блока задержки, а выходы блоков умножения соединены с входами соответствующих блоков усреднения tl .

Недостатком,, корреляционного измерителя времени запаздывания является невозможность обнаружения глобально-го максимума, что может привести к

ошибочному определению времени запаздывания. Действительно, если входные сигналы имеют колебательный характер, то их функция взаимной корреляции

также имеет несколько максимумов, причем истинному времени запаздывания соответствует положение глобального максимума, в то время как известное устройство зафиксирует в. качестве

максимума соответствующего времени запаздывания первый из встретившихся при настройке.

Наиболее близким к предлагаемому по технической сущности является корреляционный измеритель, содержащий блок регистров, входы и выходы которых соединены с входами и выходами ключей, три блока перемножителей, первые входы которых соединены с тремя иоследаими выходами блока регистров/а выхода блоков перемножителей соединены с входами блоков интегрирования, выходы которых соединены с входами блока элементов и, выходы коВТОРОГО соединены с первыми входами

ксилпараторов, выходы которых соединеиы с входами элементов И, выход кото4 юго соедниен с первыми входами триг геров, выхода которых через вспомогательные элементы И соединены с входами первого и второго сметчиков, вторые входы вспомогательных элементов И соединены с выходами соответс.твенно первого и второго элементов ИЛИ, входы которых соединены с выходами линий задержки,входы которых со дивены с выходом генератора,а дополнительные выходы с входами третьего элемента ИЛИ,выход которогб соединен с управляющим входом блока элементов И, а вход блока регистров и вторые входы блоков перемножит ел ей соединены соответственно с первым и вторым входами устройства 2.

Недостатком известного корреляционного измерителя времени запаздывания является невозможность определен-ня положения глобального максимума функции взаимной корреляции, а следовательно низкая достоверность получаемой оценки времени запаздывания.

Цель изобретения - повышение достоверности получаемой оценки времени запаздывания.

Поставленная цель достигается тем что в корреляционный измеритель , времени запаздывания, содержащий первый и второй аналого-цифровые преобразователи, информационные входы которых являются соответственно первьш и вторым входами измерителя, пять коммутаторов, первый и второй счетчики, первый элемент И, генератор импульсов, элемент ИЛИ, блок элементов И, первый и второй компараторы, два триггера, инверсный выход первого триггера подключен к управляющему входу первого коммутатора, информационный вход которого подключен к выходу первого аналого-цифрового преобразователя выход коммутатора соединен с информационным входом первого коммутатора и первым входом блока умножения, выход которого подключен к первому входу сумматора, введены второй блок регистров, второй элемент И, блок формирования начала поиска, блок исключения импульсов, делитель частоты, третий кьмпаратор, три регистра, управляющие входы аналого-цифровых Преобразователей соединены с выходом первого элемента И, первый вход которого подключен к прямому входу первого триггера, информационный вход второго коммутатора соединен с выходом второго аналогоцифрового преобразователя, выходы первого и второго блока регистров подключены ко вторым входам соответственно первого и второго коммутаторов, выход второго коммутатора соединен с первым входом блока элементов И, второй вход которого объединен с управляющим входом третьего коммутатора и подключен к прямому выходу второго триггера, информационные , входы третьего коммутатора подключены к соответствующим выходам второго

блока {регистров и к первому входу блока формирования начала поиска, выход третьего коммутатора соединен с первым входом элемента ИЛИ, второй вход которого подключен к выходу блока элементов И, а выход элемента ИЛИ соединен со в торым входом блока умножения, вход второго блока регистров подключен к выходу блока исключения импульса, выход генератора импульсов подключен ко входу делителя частоты и к первому входу четвертого коммутатора, второй вход которого соединен с выходом делителя частоты, второй вход четвертого коммутатора объединен с третьим входом второго коммутатора .и подключен к инверсно выходу первого триггера, выход четвертого коммутатора подключен к счетному входу первого счетчика, к первому входу блока исключения импульса и ко второму входу первого элемента И, выход первого счетчика соединен со счетным входом второго счетчика, со вторым входом блока исключения импульса, с первым входом первого триггера, с первым входом первого коммутатора, со вторым входо сумматора,.установочный вход второго счетчика соединен с первым выходом блока формирования начала поиска, первый выход второго счетчика подключен к первому входу пятого коммутатора, второй выход второго счетчика соединен со входом первого регистра и вторым входом пятого коммутатора, третий вход которого подключен -ко второму.выходу блока формирования начала поиска, выход пятого коммутатора соединен с первым входом второго триггера, с первым входом второго регистра, со вторым входом первого триггера, с первым входом второго, коммутатора и с первЕлм входом третьего регистра, второй вхол первого регистра объединен с вторим входом третьего регистра и подключен к выходу первого компаратора, третий вхо которого соединен с выходом сумматор а выход подключен ко второму входу первого компаратора, третий вхо.ц которого соединен с выходом сумматора, выход втсфого.регистра подключен ко входу блока формирования н-:чала поиска, управляющий вход сумматора, подключен к выходу второго элемента И, первый вход которого соединен с прямым выходом второго триггера, а второй - с выходом третьего когшутатора входы которого соединены соответственно со вторым выходом первого счет чика и с выходсм блока формирования начала поиска, входы начальной установки делителя частоты счетчиков ,п:ятого коммутатора,трех регистров,первого и второго блоков регистров ,сумматора второго компаратора, третий вход первого триггера и второй вход второго триггера объединены и подключены

К третьему входу корреляционного из-. ;мерителя.

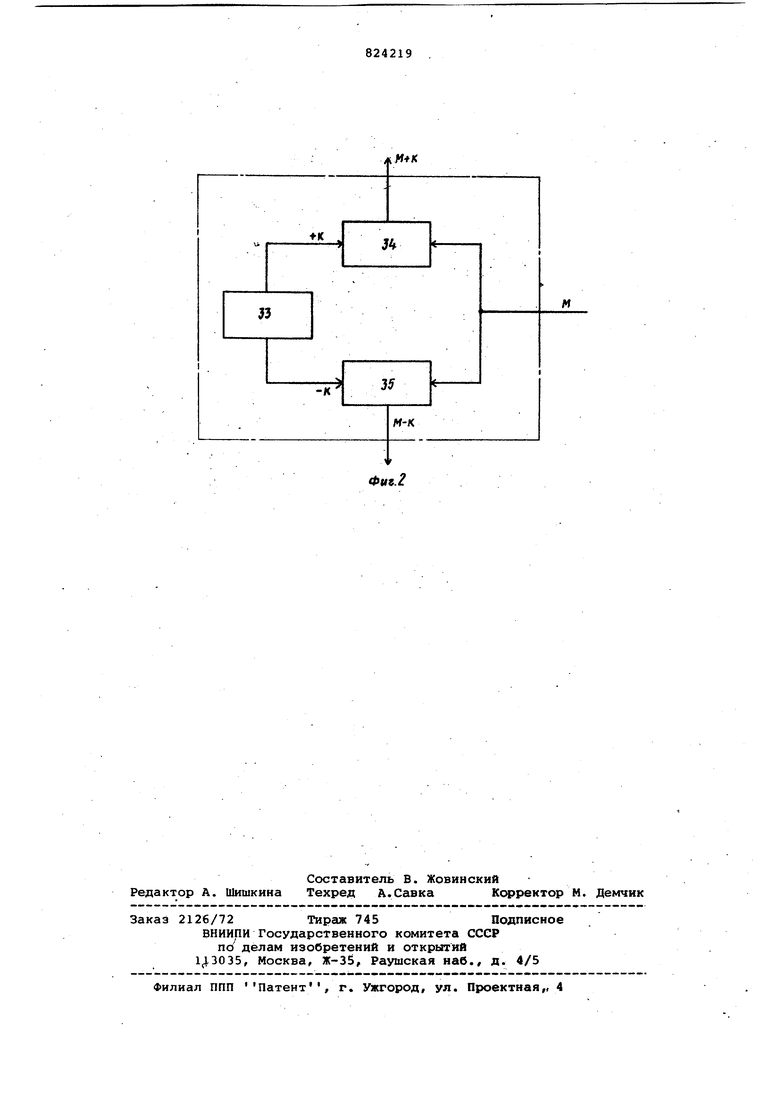

При этом блок формирования начала поиска содержит блок постоянной памяти, сумматор и блок вычитания, вход блока формирования начала поиска соединен с первыми входами сумматора и блока вычитания, вторые входда которых подключены соответственно к первому и второму выходам блока постоянной памяти, выходы сумматора и блока вычитания являются соответственно-первым и вторым выходами, блока Формирования начала поиска.

,На фиг. 1 показана структурная схема корреляционного измерителя/ на фиг. 2 - схема блока формирования начала поиска.

Корреляционный измеритель времени запаздывания содержит первый 1 и второй 2 аналого-ц фровые преоб- разователи, первый - пятый 3-7 коммутаторы, первый 8 и второй 9 блоки регистров, блок 10 умножения, сумматор 11, компараторы 12-14, регистры 15 и 16, элемент ИЛИ 17, -элемент И 18, блок элементов И 19, первый 20 и второй 21 Триггеры, третий регистр 22, блок, .23 ормирования начала поиска, блок 24 исключения импульса, генератор 25, делитель 26 частоты, первый 27 и второй 28 счетчики и элемент И 29.

Инверсный выход первого триггера 20 соединен с управляющим входом первого коммутатора 3, выход которого соединен с информационным входом первого блока 8 регистров, выход блока 10 умножения соединен с информационным входЬм блока 11 суммирования, а прямой выход второго триггера 21 соединен с управляющим Входом третьего коммутатора 5. Информационные входы первого и второго аналого-цифровых преобразов,ателей 1 и 2 соединены соответственно с первым 30 и , вторым 31 входами устройства, тактовые входы аналого-цифровых преобразователей 1 и 2 соединены с выходом элемента И 29, первый вход которого соединен с прямым выходом первого триггера 20, инверсный выход которого соединен с управляющими входами второго 4 и четвертого 6 коммутаторов, первый вход четвертого коммутатора 6 соединен с выходом делителя 26, тактовый вход которого соединен с выходом генератора 25 и вторьм входом четвертого коммутатора 6, выход Которого соединен с тактовым входом первого счетчика 27, первым входом блока 24 исключения импульса, -вторым входом элемента И 29 и тактовым входом блока 8 регистров,выход кото-, рого соединен с первым входом первого коммутатора 3, второй вход которого соединен с- выходом первого анаого-цифрового преобразователя 1, выход первого коммутатора 3 соединен с первым входом блока 10 умножения, второй вход которого соединен с выходом блока элементов ИЛИ 17, первый вход которого соединен с выходом блока элементов И 19, информационный вход которого соединен с 5 выходом второго коммутатора 4 и информационным входом второго блока 9 регистров, информационный выход которого соединен с первым входом второго коммутатора 4, второй вход

0 которого соединен с выходом второго аналого-цифрового преобразователя 2, второй вход блока элементов ИЛИ 17 соединен с -выходом третьего коммутатора 5, yпpaвляющиJй вход котороs г-О соединен с управляющим входом блока элементов И 18, коммутационные входы третьего коммутатора соединены с выходом блока 23 формирования .начала поиска, первыми входами

Q дополнительного компаратора 14 и входами установки второго счетчика 28, тактовый вход которого соединен с выходом переноса первого счетчика, выход которого соединен с вторым входом дополнительного компаратора 14,

5 вйход которого соединен с первым входом элемента И 18, второй вход и выход которого соединены соответственно с управляющим входом блока элементов И и тактовым входом блока

0 суммированмя, импульсный вход сброса которого соединен с тактовым входом первого компаратора 12, входом сброса первого триггера 20 , вторым входом блока 24 исключения импульса

5 сИ выходом переноса первого счетчика .27 вход сброса которого соединен с входом 32 запуска устройства,входами сброса первого 8 и второго 9 блоков регистров, делителя 26, второго счетчика 28, второго триггера 21,

первого регистра 15, сумматор 11 и первым входом установки первого триггера 20,а также с установочным входом пятого коммутатора 7, выход которого соединен с установочным входом в,торого триггера 21, вторым установочным входом первого триггера 20, тактовым входом второго компаратора 13, дополнительным входом сброса пер-вого регистра, а также с разрешающим

Q входом треть,его регистра 22, выход которого соединен с входом блока 24 формирования начала поиска, дополн1|тельный в№сод которого соединен с первым входом второго компаратора и управляющим входом пятого компаратгра

5 7, 11ераьЕй информационный вход которого соединен с выходом переноса второго счетчика, выход которого соединен с вторым информационным входом пятого коммутатора 7, и информационным входом второго регистра 16, первый и второй выходы которого соединены соответственно с информационным входом третьего регистра 22 и вторым

ВХОДОМ второго компаратора 13, выход

5 которого соединен с входом сброса первого регистра, информационный вхо которого соединен с выходом cy лмaтoра 11 и первым входом первого компар тора 12, второй вход которого соедииен с выходом первого регистра, вход записи соединен с входом записи второго регистра 16 и выходом первого компаратора 12, выход блока исключения импульса; соединен с тактовым входом второго блока 9 регистров, вспомогательные : выходы которого соединены с информационными входами треть его коммут атора о Блок 33 постоянной памяти (БПП) входящий в состав блока формирования начала поиска, соединен с сумматором 34 и блоком 35 вычитания. Причем в качестве БПП могут быть использованы ключи, из которых предварительно набирается требуемый кол КорреляционнЕлй измеритель времени запаздывания работает следующим образом. Перед началом работы на вход 32 установки подается сигнал, обеспечивающий установку устройства в исходное состояние. При этом обеспечивается очистка регистра 15, очист.ка первого 8 и второго 9 блоков регистров, сброс в нулевое состояние делителя 26, первого 27 и второго 28 счетчиков, установка з исходное состояние пятого коммутатора 7, сбро в нулевое состояние, второго триггера 21 и сумматора 11, а также установка в единичное состояние первого триггера 20, единичный логический сигнал с прямого выхода которого подается на вход элемента И 29, На вто рой вход этого элемента подаются импульсы с выхода ко-мг-г/татора 6, сос тояние которого опрецелнется состоянием первого триггера 20. В исходном положении этот триггер, как уже отме чалось, находится в единичном состоя нии и на выход ком1 1утатора подаются импульсы с выхода делителя с частотой, характеризующей дискретность входных сигналов в реальном масштабе времени. Эти импульсы проходят через элемент И 29 на тактовые входы аналого-цифровых Преобразователей 1 и 2, которые обеспечивают преобразование входных сигналов в соответствующие цифровые эквиваленты, которые последовательно вводятся через первый 3 и второй 4 коммутаторы соответственно в первый 8 и второй 9 бло ки регистров. Одновременно тактовые импульсы с выхода коммутатора б подсчитываются первым счетчиком 27 и после его заполнения, что соответствует вводу всей исследуемой реализации, импульсом с его выхода обеспечивается переключение, первого трйг гера 20. При вводе исходных данных .одновременно с записью в блоки регистров , получаемые цифровые оценки подаются на блок 10 умножения, результаты умножения с выхода которого подаются на вход блока суммирования в котором накапливается сумма ароизведенйй входных сигналов в течение реализации. Накопленная подаётся на первый компаратор 12 и сравнивается с хранящейся в первом регистре 15 оценкой максимума по переднему фронту сигнала, подаваемого на тактовый вход первого компаратора 12, Если получаемая сумма пtэeвышaeт хранящуюся в первом регистре 15, то первый крмпаратор 12 формирует на своем выходе сигнал, обеспечивающий запись нового; максимального значения в первый регистр 15, а также запись во второй регистр Г6 кода зафиксированного к данному моменту времени йторым счетчиком 28. После ввода реализации в блоки 8 и 9 регистрЬв и получения первой оценки максимума, переключается первый триггер 20, что приводит к переключению коммутаторов 3, 4 и 6. Кроме этого, по импульсу, подаваемому на первый вход блока 24 исключения импульса обеспечивается исключение первого из подаваемых на его второй вход и проходящих через него на тактовый вход второго блока 9 регистров импульса. Благодаря тому, что после переключения триггера 20 коммутаторы 3 и 4 переключаются, обеспечивается циркулядия информации, записанной в блоках 8 и 9 регистров, причем из-за наличия исключения импульса блоком 24 исключения импульс . через число тактов, равное длине реализации, обеспечивается относительный сдвиг записанной в обоих блоках регистров информации на один такт, что эквивалентно внесению.задержки, равной периоду импульсов генератора 25 умноженному на коэффициент деления частоты делителем 26, Получаемые сдвинутые реализации перемножаются блоком 10 умножения и результаты суммируются и сравниваются с содержимым первого регистра 15, Таким образом обеспечивается поиск глобального максимума корреляционной функции. Для этого просматривается первая реализация полностью при всех фиктивныхзначениях задержки от нуля до задержки, равной длительности реализации. После этого на выходе второго счетчика 28 появляется, сигнал-, обеспечивающий подключение пятого коммутатора 7, выходным сигналом с которого перебрасывается в единичное состояние второй триггер 21, разрешаетс.я функционирование второго компаратора 13 и производитс-я сброс первого регистра 15 и первого блока 8 регистров. Кроме того, обеспечивается переключение первого триггера 20, который переходит в единичное сое-: тряние и устройство начинаетвводить следующую реализацию. Теперь однако, из-за того, что второй триггер 21 находится в единичном логическом сос тоянии, обеспечивается считывание информации с вспомогательных выходов В.ТОРОГО блока регистров через третий коммутатор 5 и блок элементов ИЛИ 17 соответствует началу поиска максимума с некоторой задержкой, на заданный интервал, не доходящей до задержки соответствующей максимуму предьщущей реализации, положение которо го зафиксировано в третьем регистре 22. Начало поиска при этом задается блоком формирования начала поиска, который своими выходами управляет третьим коммутатором 5, обеспечивая его соответствующую коммутацию. Дополнительный компаратор 14 и злемент И 18 обеспечивают блокирование суммирования произведений до момента, когда относительный сдвиг во втором блоке регистров достигнет значени соо ветствующего началу поиска максимума. Анализ дискретных значений функции взаимной корреляции после зтого продолжается до верхней границы поис ка, задаваемой кодом с второго выхода блока .23 фо ирования начала поис ка, подаваемого на коммутатор 7 и второй корлпаратор 13. Если максимум не будет обнаружен во время данного цикла поиска внутри интервала поиска, т.е. ггопадает на границу этой области поиска, сигналом с выхода второго компаратора 13 обеспечиваетс переход к исходному состоянию и снова осуществляется поиск глобального максимума. Таким образом, поиск максимума в режиме слежения осуществляется в пределах некоторой окрестности максимума предыдущей реализации, а в ис ходном случае или в случае значитель iHoro смещения положения максимума с выходом за область поиска, обеспе чивается поиск глобального максимума что обеспечивает сочетание сравнительно высокой скорости поиска с высокой достоверностью и точностью получения оценки положения глобального максимума. Формула изобретения 1. Корреляционный измеритель времени запаздывания, содержащий первы и второй аналого-цифровые преобразователи, информационные входы которых являются соответственно первым и вторым входами измерителя, пять коммутаторов, первый и второй счетчики первый злемент И, генератор импульсов, элемент ИЛИ, блок элементов И-, первый и второй компараторы, два триггера, }1нверсный выход первого триггера подключен к управляющему входу первого коммутатора, информационный вход которого подключен к выходу первого аналого-цифрового преобразователя, выход коммутатора соединен с информационным входом первого коммутатора и с первым входом блока умножения, выход которого подключен к первому входу сумматора, отличающийся тем, что, с целью повышения точности в корреляционный измеритель введены второй .блок регистров, второй элемент И, блок формирования начала поиска, блокисключения импульса, делитель частоты, третий компаратор, три .регистра, управляющие входы аналого-цифровых преобразователей соединены с выходом первого элемента И, первый, вход которого подключен к прямому входу первого триггера,Информационный вход второго KOf MyTaTopa соединен с выходом второго аналого-цифрового пресб-, раэователя, выходы первого и второго блока регистров подключены ко вторым входам соответственно первого и второго коммутаторов, выход второго коммутатора соединен с первым входом блока элементов И, второй вход которого объединен с управляющим входом третьего коммутатора и подключен к прямому выходу второго триггера, информационные входы третьего коммутатора подключены к.соответствующим выходам второго блока регистров и к первому входу блока формирования начала поиска, выход третьего коммутатора соединен с первым входом элемента ИЛИ, второй вход которого подключен к выходу блока элементов И, а выход элемента ИЛИ соединен со вторым входом блока умножения,вход второго блока регистров подключен к выходу блока .исключения импульса, выход генератора импульсов подключен ко входу делителя частоты и к первому входу четвертого коммутатора, второй вход, которого соединен с выходом делителя частоты, вход четвертого коммутатора объединен с третьим входом второго коммутатора и подключен к инверсному выходу первого триггера, выход четвертого коммутатора подключен к счетному входу первого счетчика, к первому входу блока ис- , ключения импульса и ко второму входу первого элемента И, выход первого счетчика соединен со счетным входокР второго счетчика, со вторым входом блока исключения импульса, с первым ВХОДОМ первого триггера, с первым входом первого коммутатора, со вторьм входом сумматора, установочный вход второго счетчика соединен с первым выходом блока формирования начала поиска, первый выход второго счетчика подключен к первому входу пятого коммутатора, второй выход второго счетчика соединен со входом первого регистра и вторым входом пятого коммутатора, третий вход которого подключей ко второму выходувблока. формирования начала поиска, выход пятого коммутатора соединен с первым входом второго триггера, с первым вkoдoм вторс го регистра, со вторым входом первого триггера, с первым i входом второго компаратора, с первьгм входом третьего регистра, второй вхо первого регистра объединен со втовходом третьего регистра и подочен к выходу первого компаратора, третий вход которого соединен с БЫКОдом сумматора, а выход подключен ко второму входу яервого компаратора,третий вход которого соединен с выходом сумматора, выход второго ре- . гистра подключен ко входу блока формирования начала поиска f. управляющий вход сумматора подключен к выходу второго элемента И, первый рход которого соединен с прямым выходом, второго триггера, а второй входс выходом третьего коммутатора, входы которого соединены соответственно со вторым выходом первого счетчика и с выходом блока фор1 «1рования начала поиска, входы начальной уа-гановки делителя частоты счетчиков, тятого коммутатора, трех регистров,

первого и BTcJporo регистров, сумматсУра, второго компаратора, третий вход первого триггера и второй вход второго триггера объединены и подключены к третьему входу корреляционного измерителя.

2. Измеритель по п. 1, .о т л и чающийся тем, что в нем блок формирования начала поиска содержит блок постоянной памяти, сумматор и блок вычитания, вход блока формирования начала поиска соединен с первыми входами сумматора и блока вычитания, вторые входы которых подключены соответственно к первому и v второму выходам блока постоянной па5мяти, выходы сумматора и блока вычитания ЯВЛ1ЯЮТСЯ соответственно первым и вторым выходами блока формирования начала поиска.

0

Источники информации, принятые во внимание, при .экспертизе

1.Авторское свидетельство СССР № 226959, кл. G 06G 7/19, 1967.

2.Березин С. А. и Каратаев О. Г. Корреляционные измерительные устрой5ства в автоматике. Л, Энергия , .1976, с. 67.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| Цифровой измеритель частоты и фазы гармонического сигнала | 1988 |

|

SU1626176A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Многофункциональный цифровой коррелометр | 1983 |

|

SU1096656A1 |

| Цифровой обнаружитель-измеритель частоты | 1988 |

|

SU1597760A2 |

| Цифровой обнаружитель-измеритель частоты | 1986 |

|

SU1370584A2 |

| Коррелометр | 1983 |

|

SU1091173A1 |

Авторы

Даты

1981-04-23—Публикация

1979-06-12—Подача