C,N COS ,

n

55

«. e-T.N EM.N ,4,6,...,

2L-2

(14)

SI,N sin 2irfpt, 1-1,3,5,..., Они служат адресами, по которым из

дополнительного постоянного запо2L-1.

(11)

минающего устройства 30 считываются

55

«. e-T.N EM.N ,4,6,...,

2L-2

(14)

минающего устройства 30 считываются

n

их квадраторы, подаваемые на входы дополнительного сумматора 32 непосредственно (S тельный регистр Ji ff

С выхода дополнительного сумматора 32 через делитель 33 на два сформированные значения

f ff ) и через дополни- Тр 31 (С ).

Z(fj) -|- (c| -bSf%), ,4,6,...,2L-2

10

(15)

20

25

поступают на выход ключа 34,

Синхронизатор, переключая ключ 39 , квадратора 21 и ключ 34, поочередно подает на вход коммутатора 22 значения Z(f), ,3,5,...,2L-1 и Z(fj), ,4,6...,2L-1, которые сравниваются с содержимым регистра 24 в стробируе- мом блоке 25 сравнения. Если какое- либо значение Z(fj) превосходит содержимое регистра 24, то стробирующий импульс синхронизатора 5 проходит с входа на выход блока 25 сравнения и производит запись этого значения Z(fр) в регистр 24 через коммутатор 22, а в регистр 7 записывает состояние счетчика 6. Состояние счетчика 6 после каждого сравнения увеличивается на единицу, принимая ряд значений ,2,...,2L-1. В конечном итоге после просмотра всех (2L-1) значений Z(f«) в регистре 7 будет записан порядковый номер 1 рабочей частоты tff которой соответствует максимальное из превысивших порог обнаружения значение квадрата модуля комплексного корреляционного интеграла. Оценка частоты входного сигнала

1597760 2

разом формируются значения С р и

Sf,o .

Далее, как было описано, в oпepa тивном запоминающем устройстве 19 фиксируются результаты сложения (10) Для . С приходом следующего (второго) на интервале наблюдения (О,Т) прореженного импульса нуль-пересечений на вход 50 синхронизатора 5, последний переводит обнаружитель-измеритель частоты в режим формирования комплексного корреляционного интеграла и цикл работы повторяется.

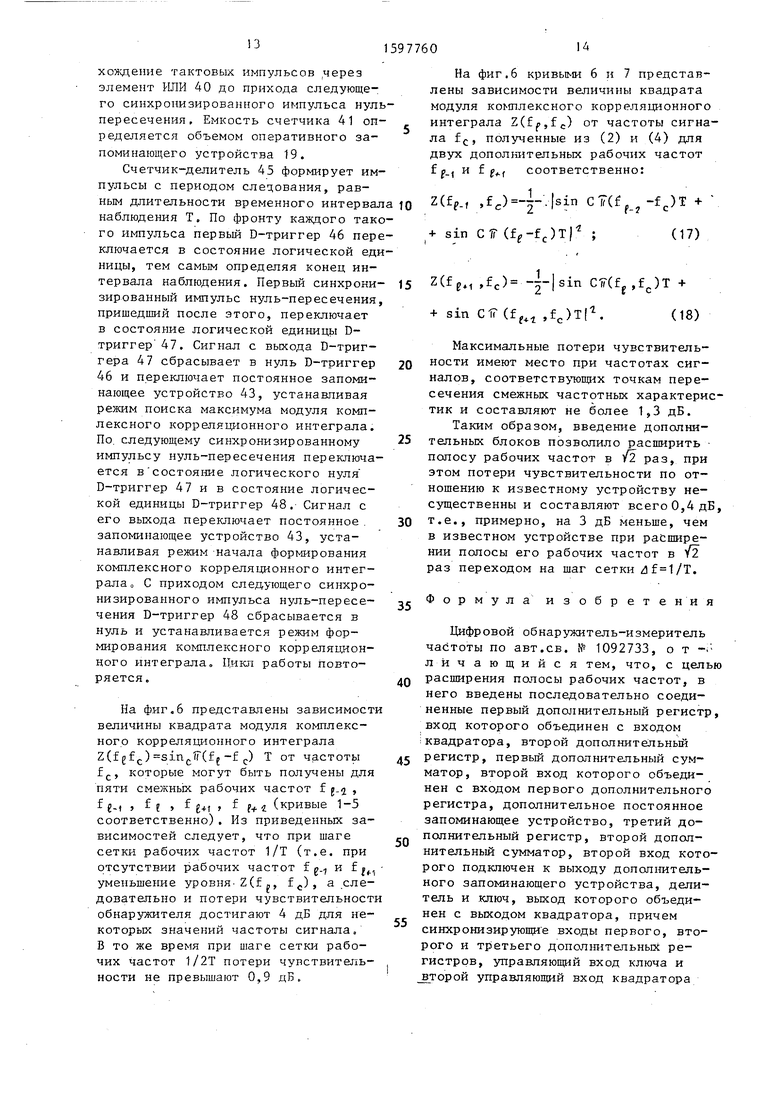

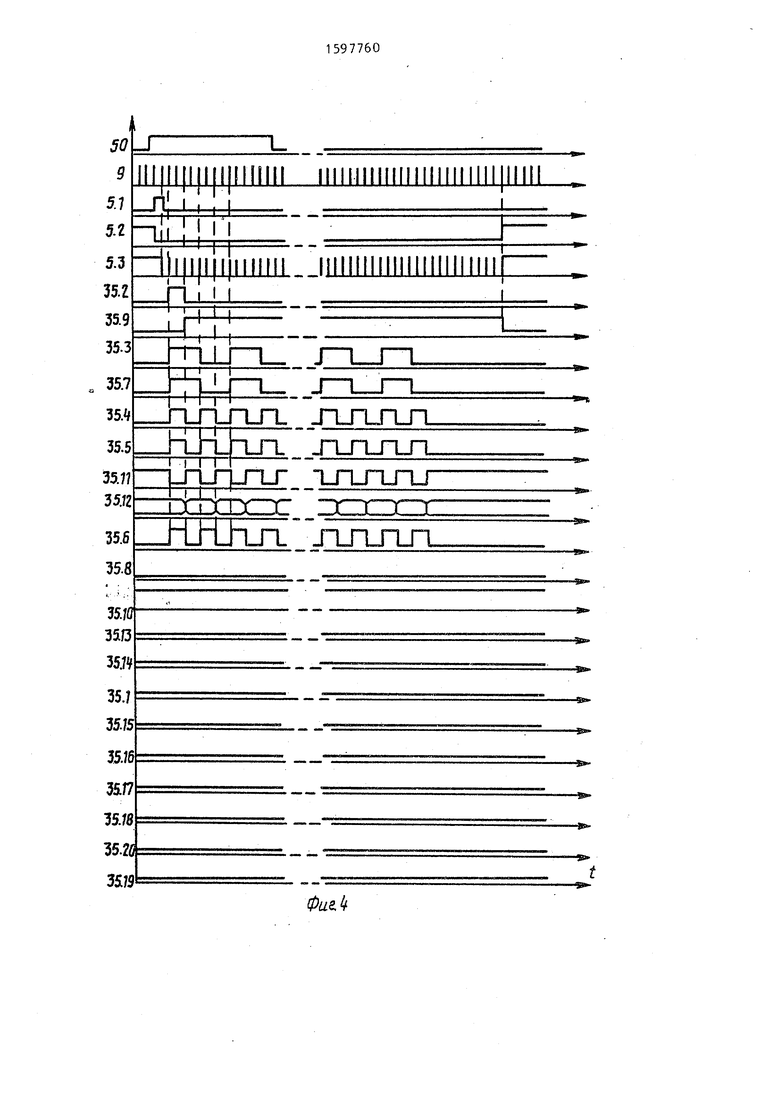

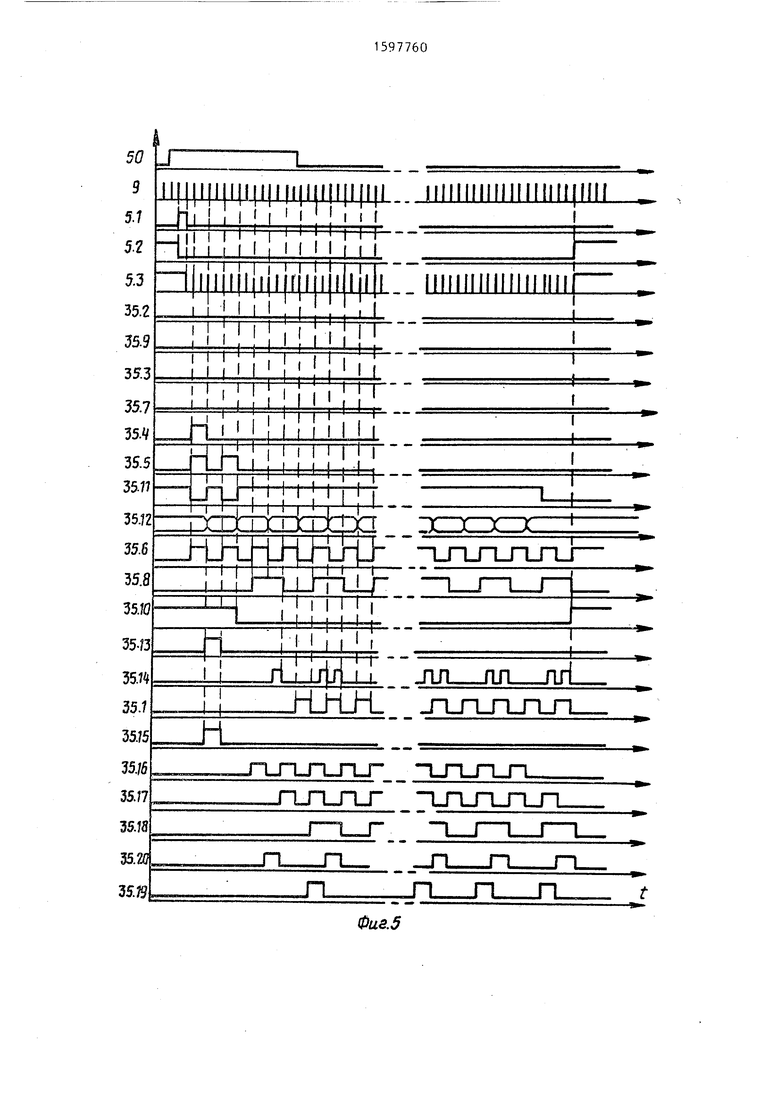

На фиг.3-5 приведены эпюры сигналов на входах 9 и 50, выходах 35,1- 35.20 и наиболее характерных точках 5.1-5.,3 синхронизатора 5 при работе в режимах начала формирования комплексного корреляционного интеграла, формирования комплексного корреляционного интеграла и поиска максимума комплексного корреляционного ин теграла соответственно.

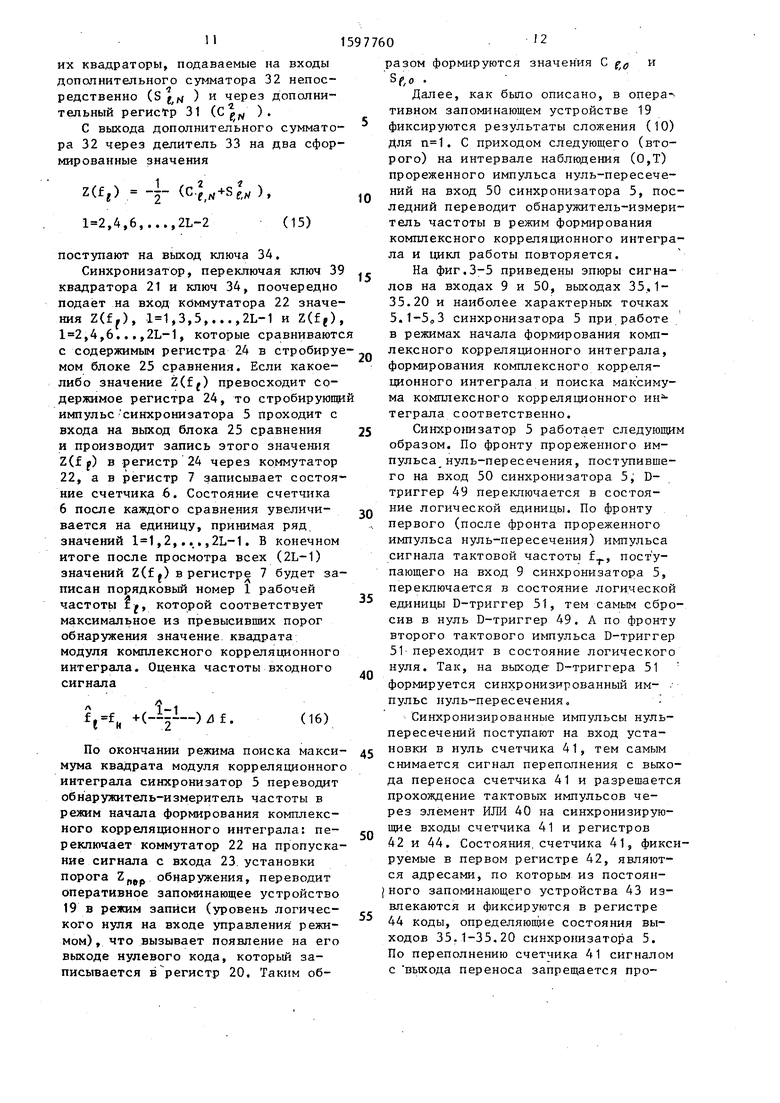

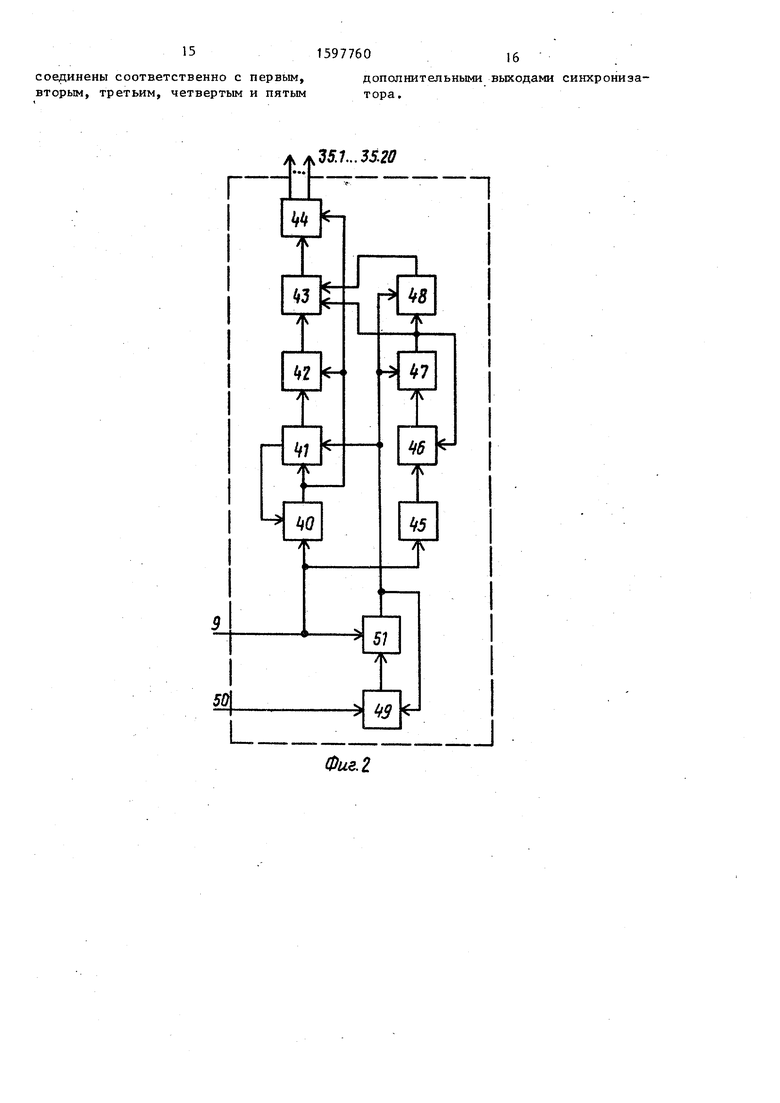

Синхро1шзатор 5 работает следующим образом. По фронту прореженного импульса нуль-пересечения, поступившего на вход 50 синхронизатора 5 D- триггер 49 переключается в состояние логической единицы. По фронту первого (после фронта прореженного импульса нуль-пересечения) импульса сигнала тактовой частоты f

30

35

40

, поступающего на вход 9 синхронизатора 5, переключается в состояние логической единицы D-триггер 51, тем самым сбросив в нуль D-триггер 49. А по фронту второго тактового импульса D-триггер 51-переходит в состояние логического нуля. Так, на выходе D-триггера 51 формируется синхронизированный им- . пульс нуль-пересечения..

+()f.

(16)

По окончании режима поиска максимума квадрата модуля корреляционного интеграла синхронизатор 5 переводит обнаружитель-измеритель частоты в режим начала формирования комплексного корреляционного интеграла: переключает коммутатор 22 на пропускание сигнала с входа 23. установки порога обнаружения, переводит оперативное запоминающее устройство 19 в режим записи (уровень логического нуля на входе управления режимом) , что вызывает появление на его выходе нулевого кода, который записывается в регистр 20. Таким об,

Синхро1шзатор 5 работает следующим образом. По фронту прореженного импульса нуль-пересечения, поступившего на вход 50 синхронизатора 5 D- триггер 49 переключается в состояние логической единицы. По фронту первого (после фронта прореженного импульса нуль-пересечения) импульса сигнала тактовой частоты f

5

0

5

0

5

, поступающего на вход 9 синхронизатора 5, переключается в состояние логической единицы D-триггер 51, тем самым сбросив в нуль D-триггер 49. А по фронту второго тактового импульса D-триггер 51-переходит в состояние логического нуля. Так, на выходе D-триггера 51 формируется синхронизированный им- . пульс нуль-пересечения..

Синхронизированные импульсы нуль- пересечений поступают на вход установки в нуль счетчика 41, тем самым снимается сигнал переполнения с выхода переноса счетчика 41 и разрешается прохождение тактовых импульсов через элемент ИЛИ 40 на синхронизирующие входы счетчика 41 и регистров 42 и 44. Состояния, счетчика 41, фиксируемые в первом регистре 42, являются адресами, по которым из постоянного запоминающего устройства 43 извлекаются и фиксируются в регистре 44 коды, определяющие состояния выходов 35.1-35,20 синхронизатора 5. По переполнению счетчика 41 сигналом с выхода переноса запрещается прохождение тактовых импульсов .через элемент ИЛИ 40 до прихода следующего синхронизированного имнульса нул пересечения. Емкость счетчика 41 определяется объемом оперативного запоминающего устройства 19.

Счетчик-делитель 45 формирует импульсы с периодом следования, равным длительности временного интервал наблюдения Т. По фронту каждого такго импульса первый D-триггер 46 перключается в состояние логической едницы, тем самым определяя конец интервала наблюдения. Первый синхрони зированный импульс нуль-пересечения пришедший после этого, переключает в состояние логической единицы D- триггер 47. Сигнал с вькода D-триг- гера 47 сбрасывает в нуль D-триггер 46 и переключает постоянное запоминающее устройство 43, устанавливая режим поиска максимума модуля комплексного корреляционного интеграла. По. следующему синхронизированному

импульсу нуль-пересечения переключается в состояние логического нуля D-триггер 47 и в состояние логической единицы D-триггер 48. Сигнал с его выхода переключает постоянное . запоминающее устройство 43, устанавливая режим -начала формирования комплексного корреляционного интеграла С приходом следующего синхронизированного импульса нуль-Пересе- чения D-триггер 48 сбрасывается в нуль и устанавливается режим формирования комплексного корреляционного интеграла. Цикл работы повторяется.

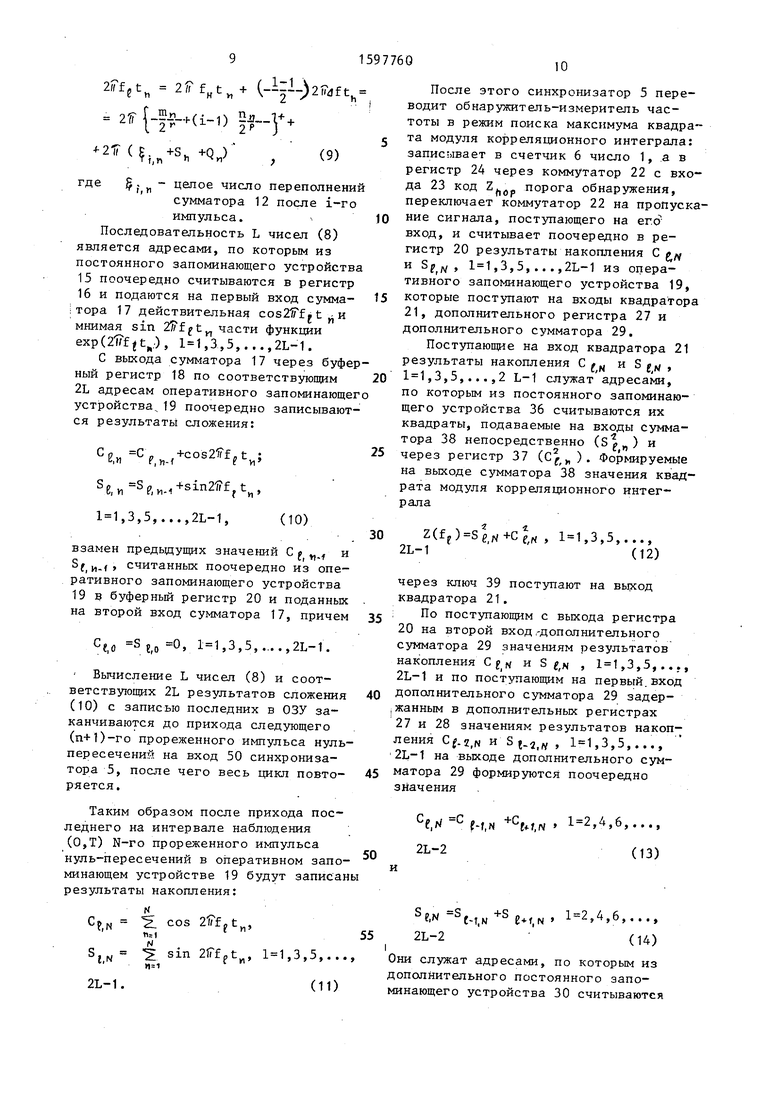

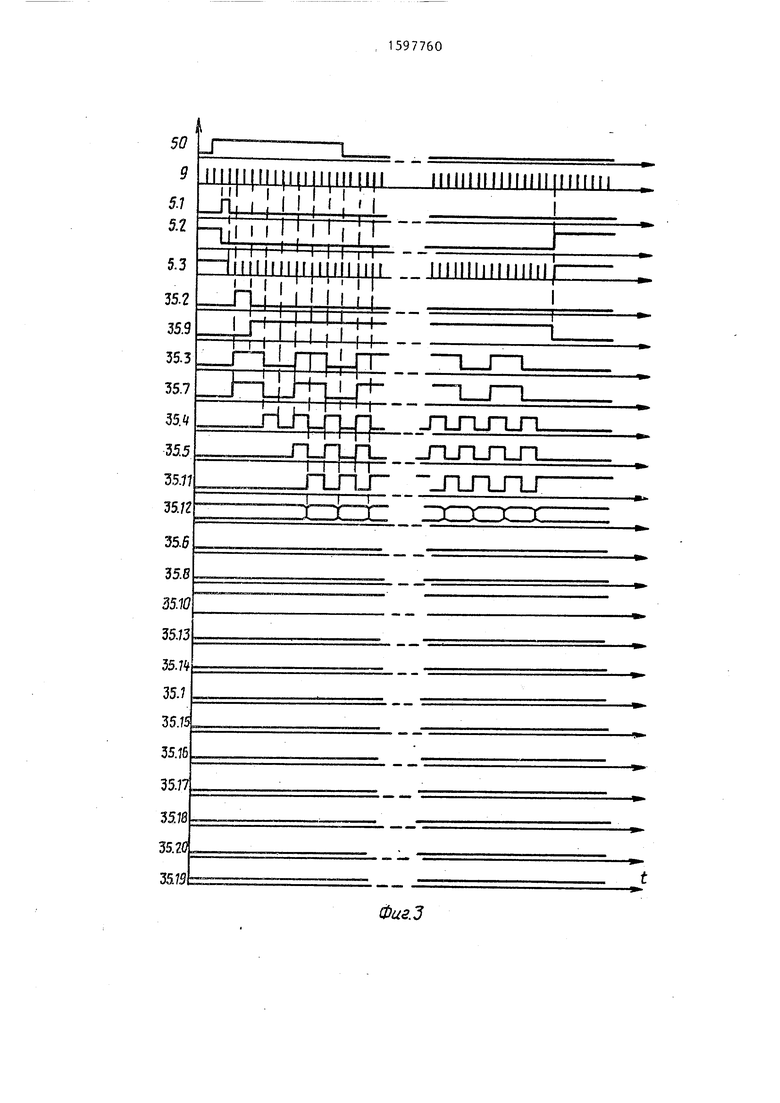

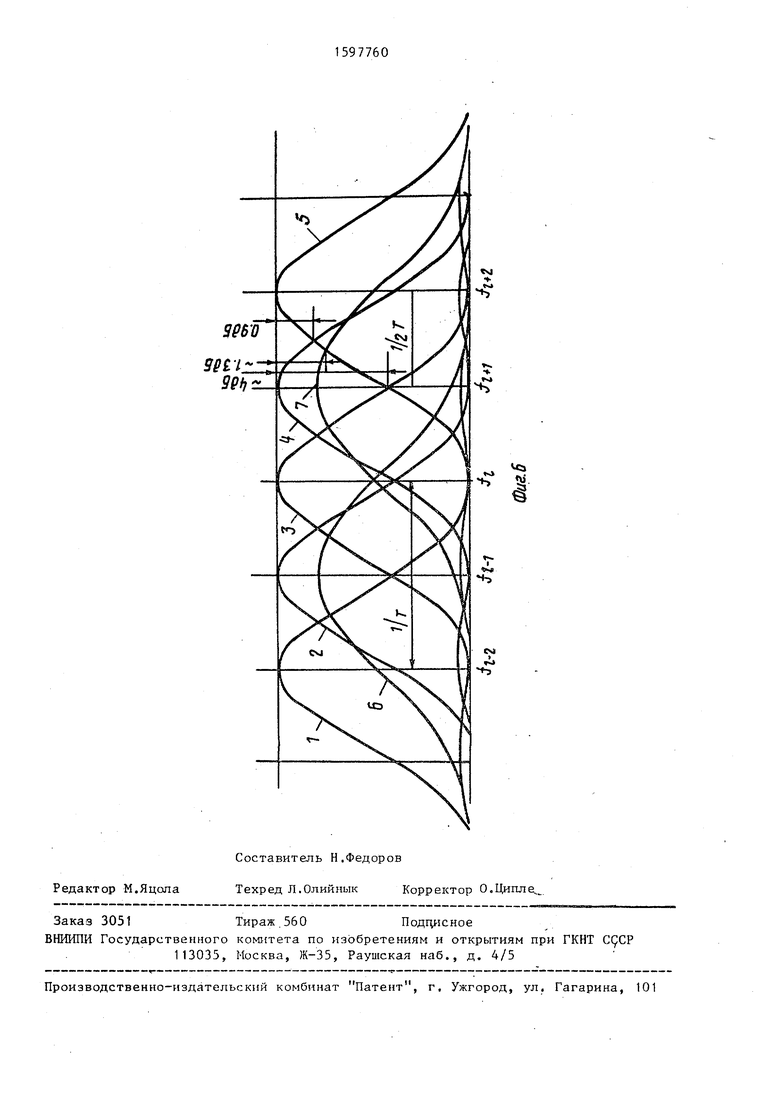

На фиг.6 представлены зависимости величины квадрата модуля комплексного корреляционного интеграла Z(f jfj.) sinj,(f f-f J.) Т от частоты

(-, которые могут быть получены для пяти смежньЬс рабочих частот f j./j , fg,, , f { , f g+, , f i+ i (кривые 1-5 соответственно). Из приведенных зависимостей следует, что при шаге сетки рабочих частот 1/Т (т.е. при отсутствии рабочих частот f g. и f, уменьшение уровня-Z(f, f) а .следовательно и потери чувствительности обнаружителя достигают 4 дБ для некоторых значений частоты сигнала. В то же время при шаге сетки рабочих частот 1/2Т потери чувствительности не превышают 0,9 дБ.

На фиг.6 кривыми 6 и 7 представлены зависимости величины квадрата модуля ко тлексного корреляционного интеграла Z(fp,fc) от частоты сигнала f{., полученные из (2) и (4) для двух допол1штельньк рабочих частот соответственно:

fp-i и f м

ю 15 20 25

30 35 4Q

j

0

5

Z(fp., ,f).Isin cT(y,-f)T + + sin С ()) ;(17)

Z(f g,, ,fc) -j-|sin C(fj ,f)T + + sin Cir(f, ,fc)T(.(18)

Максимальные потери чувствительности имеют место при частотах сигналов, соответствуюпщх точкам пересечения смежных частотных характеристик и составляют не более 1,3 дБ.

Таким образом, введение дополнительных блоков позволило расширить полосу рабочих частот в /2 раз, при этом потери чувствительности по отношению к известному устройству несущественны и составляют всего 0,4 дБ, т.е., примерно, на 3 дБ меньше, чем в известном устройстве при расширении полосы его рабочих частот в /2 раз переходом на шаг сетки 3 .

Формула изобрете ни я

Цифровой обнаружитель-измеритель частоты по авт.св. № 1092733, о т личающийся тем, что, с целью расширения полосы рабочих частот, в него введены последовательно соединенные первый дополнительный регистр, вход которого объединен с входом iквадратора, второй дополнительный регистр, первый дополнительный сумматор, второй вход которого объединен с входом первого дополнительного регистра, дополнительное постоянное запоминающее устройство, третий дополнительный регистр, второй дополнительный сумматор, второй вход которого подключен к выходу дополнительного запоминающего устройства, делитель и ключ, выход которого объединен с выходом квадратора, причем синхронизирующее входы первого, второго и третьего допол1штельных регистров, управляющий вход ключа и торой управляющий вход квадратора

соединены соответственно с первым, вторым, третьим, четвертым и пятым

дополнительными выходами синхронизатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой обнаружитель-измеритель частоты | 1986 |

|

SU1370584A2 |

| Цифровой измеритель частоты и фазы гармонического сигнала | 1988 |

|

SU1626176A1 |

| Устройство для автоподстройки частоты и цифровой обнаружитель-измеритель частоты | 1982 |

|

SU1092733A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Измеритель коэффициента шума | 1988 |

|

SU1524014A1 |

| Устройство для цифровой обработки сигналов | 1979 |

|

SU879494A1 |

| Цифровой измеритель частоты | 1988 |

|

SU1684710A1 |

| Цифровой измеритель задержки | 1981 |

|

SU951228A1 |

| Цифровой измеритель задержки | 1980 |

|

SU930219A2 |

Изобретение относится к радиоизмерительной технике и может использоваться для выделения и измерения частоты сигнала в шумах. Целью изобретения является расширение полосы рабочих частот. Цифровой обнаружитель-измеритель частоты содержит вход 1, выход 2, компаратор 3, счетчик-делитель 4, синхронизатор 5, счетчики 6, 8, регисторы 7, 11, 14, 16, 18, 20, 24, сумматоры 12, 17, коммутаторы 13, 22, постоянное запоминающее устройство 15, оперативное запоминающее устройство 19, квадратор 21, блок 25 сравнения и элемент ИЛИ 26. Введение дополнительных регистров 27, 28, 31, дополнительных сумматоров 29, 32, дополнительного постоянного запоминающего устройства 30, делителя 33 и ключа 34 позволяет расширить полосу рабочих частот в √2 раз без существенных потерь чувствительности. 6 ил.

А А35.7...557

Фиг. 2

50 9

35Л6 35.77 3578 35.20 3575

Фиг.д

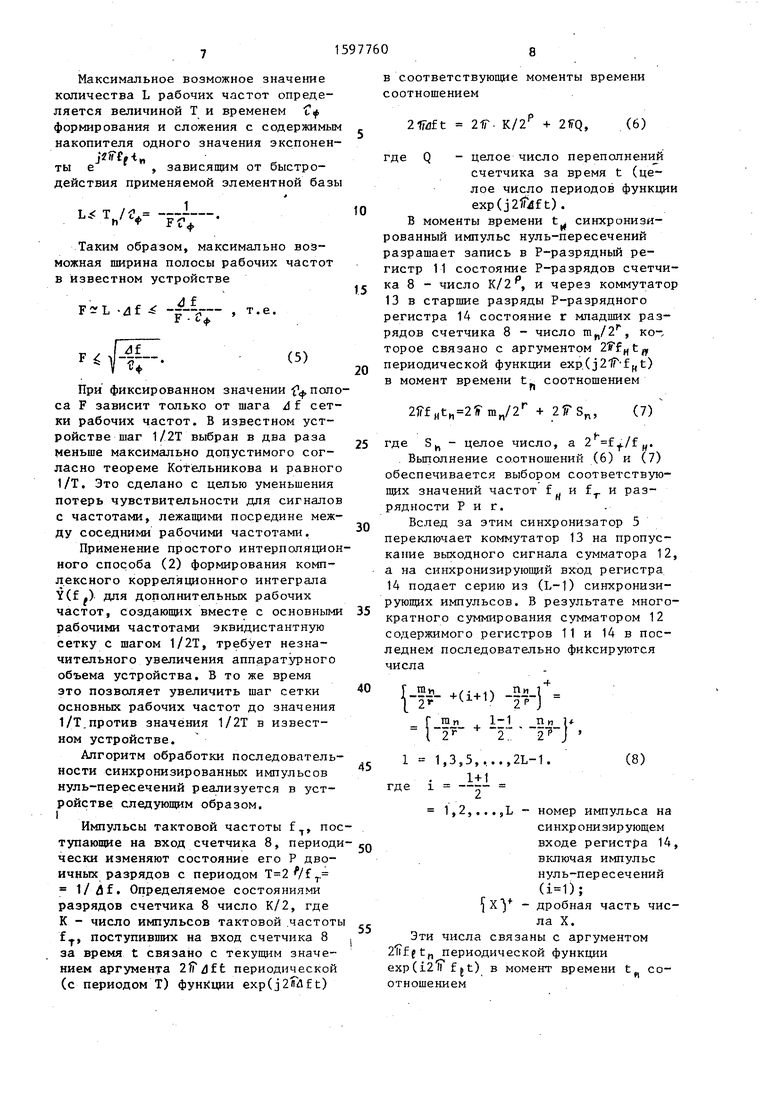

т

IIILII

п

iimi ЦНИИ liinniiiHiiiiiinini

I (f f

-гигъгъгт

IDCDGDCZX: ZXZrZXZDC

IKfLTL JTTLriJT

-

Фие.5

9ei-i

| Цифровой обнаружитель-измеритель частоты | 1986 |

|

SU1370584A2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для автоподстройки частоты и цифровой обнаружитель-измеритель частоты | 1982 |

|

SU1092733A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-10-07—Публикация

1988-10-26—Подача