Изобретение относится к радиотехнике и может быть использовано в радиоприемных устройствах для выделения сигнала с изменяющейся во времени несущей частотцй и измерения отношения сигнал/шум.

Целью изобретения является расширение функциональных возможностей

тельной установки первого счетчика 6 соединены с соответствующими выходами 34.1-34.15 синхронизатора 5, а квадратор 21 содержит постоянное запоминающее устройство 35, регистр 36 и сумматор 37.

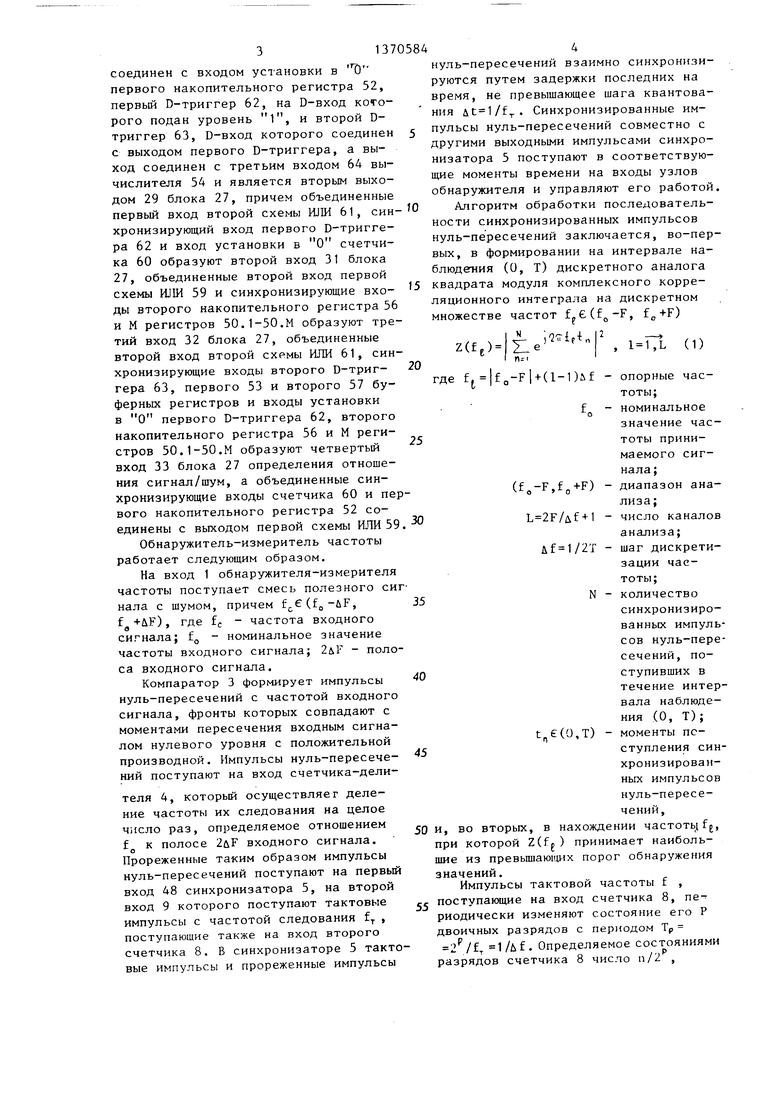

Синхронизатор 5 (фиг. 2) содержит последовательно соединенные схему

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой обнаружитель-измеритель частоты | 1988 |

|

SU1597760A2 |

| Цифровой измеритель частоты и фазы гармонического сигнала | 1988 |

|

SU1626176A1 |

| Устройство для автоподстройки частоты и цифровой обнаружитель-измеритель частоты | 1982 |

|

SU1092733A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Измеритель коэффициента шума | 1988 |

|

SU1524014A1 |

| Устройство для цифровой обработки сигналов | 1979 |

|

SU879494A1 |

| Цифровой измеритель частоты | 1988 |

|

SU1684710A1 |

| Цифровой измеритель задержки | 1979 |

|

SU822063A1 |

| Следящий измеритель частоты | 1985 |

|

SU1298675A1 |

Изобретение может быть использовано в радиоприемных устройствах для выделения сигнала с изменяющейся во времени несущей частотой и измерения отношения сигнал/шум. Цель изобретения - расширение функциональных возможностей устройства. Обнаружитель-измеритель частоты содержит компаратор 3, счетчик-делитель 4, синхронизатор 5, счетчики 6, 8, регистры 7, 11, 14, 16, 18, 20, 24, сумматоры 12, 17, коммутаторы 13, 22, постоянное запоминающее устройство 15, оперативное запоминающее устройство 19, квадратор 21, блок 25 сравнения и схему ИЛИ 26. Введение блока 27 определения отношения сигнал/шум обеспечивает совместное измерение частоты сигнала и отношения сигнал/ /шум. В описании приведены примеры выполнения блока 27 определения отношения сигнал/шум и синхронизатора 5. 3 ил. (Л со о ел 00 N)

устройства путем обеспечения совмест- ИЛИ 38, счетчик ЗУ, первый регистр 40,

ного измерения частоты сигнала и отношения сигнал/шум.

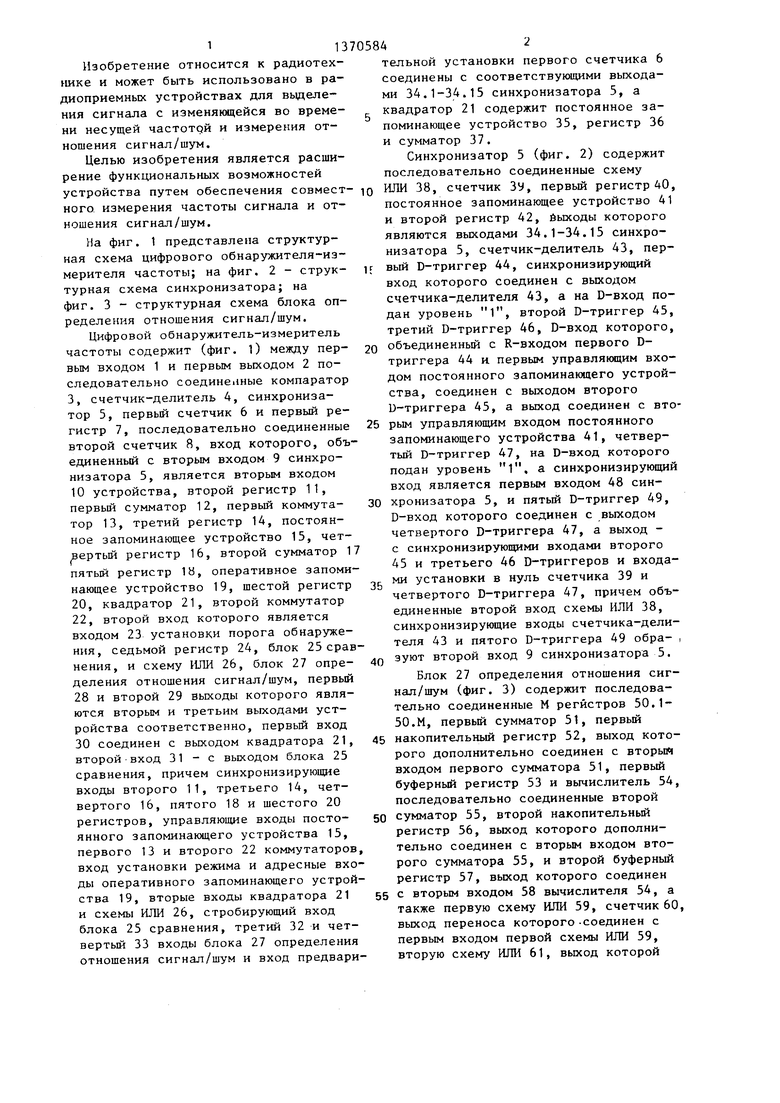

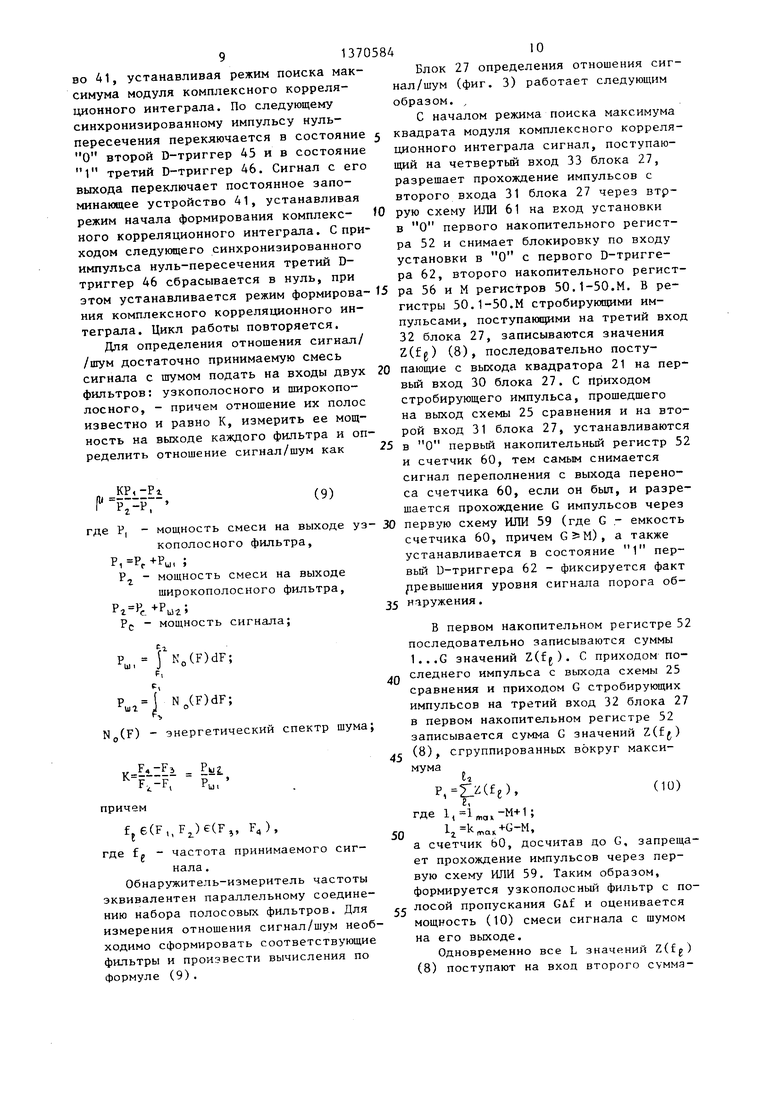

На фиг. 1 представлена структурная схема цифрового обнаружителя-измерителя частоты; на фиг. 2 - структурная схема синхронизатора; на фиг. 3 - структурная схема блока определения отношения сигнал/шум.

Цифровой обнаружитель-измеритель частоты содержит (фиг. 1) между первым входом 1 и первым выходом 2 последовательно соединенные компаратор 3, счетчик-делитель 4, синхронизатор 3, первый счетчик 6 и первый регистр 7, последовательно соединенные второй счетчик 8, вход которого, объединенный с вторым входом 9 синхронизатора 5, является вторым входом 10 устройства, второй регистр 11, первый сумматор 12, первый коммутатор 13, третий регистр 14, постоянное запоминающее устройство 15, четвертый регистр 16, второй сумматор 1 пятьй регистр 1Ь, оперативное запоминающее устройство 19, шестой регистр 20, квадратор 21, второй коммутатор 22, второй вход которого является входом 23 установки порога обнаружения, седьмой регистр 24, блок 25 сравнения, и схему ИЛИ 26, блок 27 определения отношения сигнал/шум, первый 28 и второй 29 выходы которого являются вторым и третьим выходами устройства соответственно, первый вход 30 соединен с выходом квадратора 21, второй вход 31 - с выходом блока 25 сравнения, причем синхронизирующие входы второго 11, третьего 14, четвертого 16, пятого 18 и шестого 20 регистров, управляющие входы постоянного запоминающего устройства 15, первого 13 и второго 22 коммутаторов вход установки режима и адресные входы оперативного запоминающего устройства 19, вторые входы квадратора 21 и схемы ИЛИ 26, стробирующий вход блока 25 сравнения, третий 32 и четвертый 33 входы блока 27 определения отношения сигнал/шум и вход предварипостоянное запоминающее устройство 41 и второй регистр 42, йыходы которого являются выходами 34.1-34.15 синхронизатора 5, счетчик-делитель 43, первый D-триггер 44, синхронизирующий вход которого соединен с выходом счетчика-делителя 43, а на D-вход подан уровень 1, второй D-триггер 45, третий D-триггер 46, D-вход которого,

объединенный с R-входом первого D- триггера 44 и первым управляющим входом постоянного запоминающего устройства, соединен с выходом второго D-триггера 45, а выход соединен с вторым управляющим входом постоянного запоминающего устройства 41, четвертый D-триггер 47, на D-вход которого подан уровень 1, а синхронизирующий вход является первым входом 48 синхронизатора 5, и пятый D-триггер 49, D-вход которого соединен с выходом четвертого D-триггера 47, а выход - с синхронизирующими входами второго 45 и третьего 46 D-триггеров и входами установки в нуль счетчика 39 и четвертого D-триггера 47, причем объединенные второй вход схемы ИЛИ 38, синхронизирующие входы счетчика-делителя 43 и пятого D-триггера 49 обра- i

зуют второй вход 9 синхронизатора 5.

Блок 27 определения отношения сигнал/шум (фиг. 3) содержит последовательно соединенные М регистров 50.1- 50.М, первый сумматор 51, первый

накопительный регистр 52, выход которого дополнительно соединен с вторый входом первого сумматора 51, первый буферный регистр 53 и вычислитель 54, последовательно соединенные второй

сумматор 55, второй накопительный регистр 56, выход которого дополнительно соединен с вторым входом второго сумматора 55, и второй буферный регистр 57, выход которого соединен

с вторым входом 58 вычислителя 54, а также первую схему ИЛИ 59, счетчик 60, выход переноса которого -соединен с первым входом первой схемы ИЛИ 59, вторую схему ИЛИ 61, выход которой

3137

соединен с входом установки в О первого накопительного регистра 52, первый D-триггер 62, на D-вход которого подан уровень 1, и второй D- триггер 63, D-вход которого соединен с выходом первого D-триггера, а выход соединен с третьим входом 64 вычислителя 54 и является вторым выходом 29 блока 27, причем объединенные первый вход второй схемы ШШ 61, син хронизирующий вход первого D-триггера 62 и вход установки в О счетчика 60 образуют второй вход 31 блока 27, объединенные второй вход первой схемы ИЛИ 59 и синхронизирующие входы второго накопительного регистра 56 и М регистров 50.1-50.М образуют третий вход 32 блока 27, объединенные второй вход второй схемы ИЛИ 61, синхронизирующие входы второго D-триггера 63, первого 53 и второго 57 буферных регистров и входы установки в О первого D-триггера 62, второго накопительного регистра 56 и М регистров 50.1-50.М образуют четвертый вход 33 блока 27 определения отношения сигнал/шум, а объединенные синхронизирующие входы счетчика 60 и первого накопительного регистра 52 соединены с выходом первой схемы ИЛИ 59

Обнаружитель-измеритель частоты работает следующим образом.

На вход 1 обнаружителя-измерителя частоты поступает смесь полезного сигнала с шумом, причем .6 (, f -i-uF), где fc - частота входного сигнала; f - номинальное значение частоты входного сигнала; 2дР - полоса входного сигнала.

Компаратор 3 формирует импульсы нуль-пересечений с частотой входного сигнала, фронты которых совпадают с моментами пересечения входным сигналом нулевого уровня с положительной производной. Импульсы нуль-пересечений поступают на вход счетчика-дели

теля 4, который осуществляет деление частоты их следования на целое члсло раз, определяемое отношением f к полосе 2лГ входного сигнала.

О

Прореженные таким образом импульсы нуль-пересечений поступают на первый вход 48 синхронизатора 5, на второй вход 9 которого поступают тактовые импульсы с частотой следования f,. , поступающие также на вход второго счетчика 8. В синхронизаторе 5 тактовые импульсы и прореженные импульсы

нуль-пересечений взаимно синхронизируются путем задержки последних на время, не превышающее шага квантования . Синхронизированные импульсы нуль-пересечений совместно с другими выходными импульсами синхронизатора 5 поступают в соответствующие моменты времени на входы узлов обнаружителя и управляют его работой. Алгоритм обработки последовательности синхронизированных импульсов нуль-пересечений заключается, во-первых, в формировании на интервале на- блюдегния (О, Т) дискретного аналога квадрата модуля комплексного корреляционного интеграла на дискретном множестве частот (, f„+F)

0

О

5

5

0

5

Z(f,)

N

Г-е

П-1

) 2 ip-tn

,L (1)

где (l-1)Af f, (,f,+F)

L 2F/uf-i-l

N опорные частоты;

номинальное значение частоты принимаемого сигнала;

диапазон анализа;

число каналов анализа; шаг дискретизации частоты;

количество синхронизированных импульсов нуль-пересечений, поступивших в течение интервала наблюдения (О, Т); моменты поступления синхронизированных импульсов нуль-пересечений,

0 и, во вторых, в нахождении частотщГ, при которой ZCfj) принимает наибольшие из превьш1аю1цих порог обнаружения значений.

Импульсы тактовой частоты f , поступающие на вход счетчика 8, пе риодически изменяют состояние его Р двоичных разрядов с периодом Тр 1/if . Определяемое состояниями разрядов счетчика 8 число п/2 ,

(o,T)

5

где n - число импульсов тактовой

частоты f, поступающих на вход счетчика 8 за время t, связано с текущим значением фазы опорного сигнала sinZITuft в соответствующие момен13705846

(соз21Г с„) и мнимая (з1п21Г р tf,)

части функции exp(j2Tfgt), ,L

С выхода второго сумматора 17 через пятый буферный регистр 18 п соответствующим 2L адресам опера ного запоминакщего устройства 19 писываются результаты сложения:

(2)

ты времени соотношением

2T;ift 27.n/2 +2 rK, где К - целое число.

В моменты времени t синхронизированный импульс нуль-пересечений разрешает запись в Р-разрядный второй регистр 11 состояния Р разрядов второго счетчика 8 - числа Пп/2 и через первый коммутатор 13 в старшие разряды Р-разрядного третьего регистра 14 - состояния г младших разрядов второго счетчика 8 - числа т„/2 , которое связано с фазой (fo- F)t опорного сигнала sin2 rr(fo-F) t соотношением

2ir(fo-F)t,27m /242TS, (3) где S - целое число;

,/(f,-F).

Выполнение соотношений (2) и (3) обеспечивается выбором соответствующих значений частот „, fr и разрядности Риг.

Вслед за этим синхронизатор 5 переключает первый коммутатор 13 на пропускание выходного сигнала первого сумматора 12, а на синхронизирующий вход третьего регистра 14 подает серию из L-1 синхронизирующих импульсов. В результате многократного суммирования первым сумматором 12 содержимого первого 11 и третьего 14 регистров в последнем последовательно фиксируются числа

|(1-1) l bt, (А) где xj - дробная часть числа X,

С выхода второго сумматора 17 через пятый буферный регистр 18 по соответствующим 2L адресам оператив ного запоминакщего устройства 19 за писываются результаты сложения:

/О

15

20

25

30

35

Cfn Ce,n-l +СОз2Т е „;

е,п

Se,..+SLn2Tfjt, ,L, (6)

взамен предыдущих сумм С

е,п е, псчитанных из оперативного запоминаю щего устройства 19 в шестой буферны регистр 20 и поданных на второй вхо второго сумматора 17, причем Срд , ,L.

Вычисления L чисел (4) и соответ ствующих 2L сумм (6) заканчивается до прихода следующего (п+1)-го прореженного импульса нуль-пересечений на вход 48 синхронизатора 5, после чего весь цикл повторяется.

Таким образом, практически сразу после прихода последнего на интерва ле наблюдения (О, Т) N-ro прореженн го импульса нуль-пересечений в опер тивном запоминающем устройстве 19 записаны результаты накопления:

N

Ce, Z:cos2Tfjt ;

e-1

S sin2irfgt, 1 T7L.

(7)

После этого синхронизатор 5 пере водит обнаружитель-измеритель часто в режим поиска максимума квадрата модуля корреляционного интеграла: записывает в первый счетчик 6 число

40 а в седьмой регистр 24 через второй коммутатор 22 с входа 23 - код Z по рога обнаружения, переключает второ коммутатор 22 на пропускание выходн го сигнала квадратора 21 и считывае

45 поочередно в шестой регистр 20 резу

таты накопления , и

е,и

,

связанные с фазой, 2 ii fgtf опорного сигнала sinZiffj t соотношением

2 r:fetn 2 ir(fo-F)t + (l-1)2irflft (1-1),(5)

где - целое число.рез регистр 36 (С.. ).

Последовательность чисел (4) явля- Каждое из формируемых на выходе ется адресами, по которым из постоян- сумматора 37 квадратора 21 значение

ного запоминающего устройства 15 по-квадрата модуля корреляционного иночередно считываются в четвертый ре-теграла гистр 16 и подаются на первый вход второго сумматора 17 действительная

из оперативного запоминающего устро ства 19. Последние служат адресами, по которым из постоянного запоминаю 50 щего устройства 35 считываются их квадраты, подаваемые на входы сумма тора 37 непосредственно (S, „ ) и че

Ci

(ft)

Ч,н

1 -TTi,

(8

части функции exp(j2Tfgt), ,L.

С выхода второго сумматора 17 через пятый буферный регистр 18 по соответствующим 2L адресам оперативного запоминакщего устройства 19 записываются результаты сложения:

/О

Cfn Ce,n-l +СОз2Т е „;

е,п

Se,..+SLn2Tfjt, ,L, (6)

взамен предыдущих сумм С

е,п е, п1

считанных из оперативного запоминающего устройства 19 в шестой буферный регистр 20 и поданных на второй вход второго сумматора 17, причем Срд , ,L.

Вычисления L чисел (4) и соответствующих 2L сумм (6) заканчивается до прихода следующего (п+1)-го прореженного импульса нуль-пересечений на вход 48 синхронизатора 5, после чего весь цикл повторяется.

Таким образом, практически сразу после прихода последнего на интервале наблюдения (О, Т) N-ro прореженного импульса нуль-пересечений в оперативном запоминающем устройстве 19 записаны результаты накопления:

N

Ce, Z:cos2Tfjt ;

e-1

S sin2irfgt, 1 T7L.

(7)

35

После этого синхронизатор 5 переводит обнаружитель-измеритель частоты в режим поиска максимума квадрата модуля корреляционного интеграла: записывает в первый счетчик 6 число 1,

40 а в седьмой регистр 24 через второй коммутатор 22 с входа 23 - код Z порога обнаружения, переключает второй коммутатор 22 на пропускание выходного сигнала квадратора 21 и считывает

45 поочередно в шестой регистр 20 результаты накопления , и

е,и

,

рез регистр 36 (С.. ).

из оперативного запоминающего устройства 19. Последние служат адресами, по которым из постоянного запоминаю- 50 щего устройства 35 считываются их квадраты, подаваемые на входы сумматора 37 непосредственно (S, „ ) и чеCi

Ч,н

1 -TTi,

(8)

.пропорциональное мощности сигнала на частоте fj , сравнивается с содержимым

седьмого регистра 24 в стробируемом блоке 25 сравнения. Если какое либо значение Z(fj ) превосходит содержи- 5 мое регистра 24, то стробирующий импульс синхронизатора 5 проходит с входа на выход блока 25 сравнения и производит запись в седьмой регистр 24 через второй коммутатор 22 этого зна- О еле фронта прореженного импульса чения, а в первый регистр 7 записывает нуль-пересечения) импульса сигнала

комплексного корреляционного интег ла и цикл работы повторяется.

Синхронизатор 5 работает следую щим образом.

По фронту прореженного импульса нуль-пересечения, поступающего на первый вход 48 синхронизатора 5, ч вертый D-триггер 47 переключается состояние 1. По фронту первого (

состояние первого счетчика 6. Состояние первого счетчика 6 после каждого сравнения увеличивается на единицу, принимая ряд значений ,L. В конечном итоге после просмотра всех L значений Z(fp) в первом регистре 7 записывается оценка частоты rnai максимальной составляющей комплексного корреляционного спектра (1)

Каждое из L значений квадрата модуля корреляционного интеграла Z(fj) (8) также поступает на первый вход 30 блока 27 определения отноще- ния сигнал/шум, на второй вход 31 блока 27 поступают стробирующие импульсы, прошедшие на выход блока 25 сравнения, на третий вход 32 блока 27 поступают стробирующие импульсы, а на четвертый вход 33 блока 27 поступает сигнал, переводящий обнаружитель в режим поиска максимума квадрата модуля корреляционного интеграла.

По окончании режима поиска максимума квадрата модуля корреляционного интеграла синхронизатор 5 переводит обнаружитель-измеритель частоты в режим начала формирования комплексного корреляционного интеграла: переключает второй коммутатор 22 на пропускание сигнала с входа 23 установки порога обнаружения, переводит оперативное запоминающее устройство 19 в режим записи (уровень О на входе управления режимом), что вызывает появление на его выходе нулевого кода, который записывается в шестой регистр 20. Таким образом, формируются значения Cgp и .

Далее, как описано выше, в оперативном запЬминающем устройстве 19 фиксируются результаты сложения (6) для . С приходом следующего ( го импульса первый D-триггер 44 п ключается в состояние 1, тем сам определяя конец интервала наблюден Первый синхронизированный импульс нуль-пересечения, пришедший после

рого) на интервале наблюдения (О, Т) этого, переключает в состояние Т

прореженного импульса нуль-пересечения на вход 48 синхронизатора 5 последний переводит обнаружитель-измеритель частоты в режим формирования

второй D-триггер 45. Сигнал с выхо второго D-триггера 45 сбрасывает в нуль первый D-триггер 44 и переклю ет постоянное запоминающее устройс

еле фронта прореженного импульса нуль-пересечения) импульса сигнала

комплексного корреляционного интеграла и цикл работы повторяется.

Синхронизатор 5 работает следующим образом.

По фронту прореженного импульса нуль-пересечения, поступающего на первый вход 48 синхронизатора 5, четвертый D-триггер 47 переключается в состояние 1. По фронту первого (потактовой частоты f, поступающего на второй вход 9 синхронизатора 5, в состояние 1 переключается пятый 15 D-триггер 49, тем самым сбрасывая в нуль четвертый D-триггер 47, а по фронту второго тактового импульса пятый D-триггер 49 переходит в сос- тояние О. Так на выходе пятого 20 D-триггера 49 формируется синхронизированный импульс нуль-пересечени

Синхронизированные импульсы нуль- пересечений поступают на вход установки в О счетчика 39, тем самым 25 снимается сигнал переполнения с выхода переноса счетчика 39 и разрешаетс прохождение тактовых импульсов через схему ИЛИ 38 на синхронизирующие входы счетчика 39 и регистров 40 30 и 42. Состояния счетчика 39, фиксируемые в первом регистре 40, являются адресами, по которым из постоянного запоминающего устройства 41 извлекаются и фиксируются во втором реги- 35 стре 42 коды, определяющие состояния выходов 34.1-34.15 синхронизатора 5. По переполнению счетчика 39 сигналом с выхода переноса запрещается прохождение тактовых импульсов через схе- 40 му ИЛИ 38 до прихода следующего синхронизированного импульса нуль-пересечения. Емкость счетчика 39 определяется объемом оперативного запоминающего устройства 19.

451

Счетчик-делитель 43 формирует импульсы с периодом следования, равным длительности временного интервала наблюдения Т. По фронту каждого тако Q го импульса первый D-триггер 44 переключается в состояние 1, тем самым определяя конец интервала наблюдения. Первый синхронизированный импульс нуль-пересечения, пришедший после

этого, переключает в состояние Т

этого, переключает в состояние Т

второй D-триггер 45. Сигнал с выхода второго D-триггера 45 сбрасывает в нуль первый D-триггер 44 и переключает постоянное запоминающее устройст91370584

во 41, устанавливая режим поиска максимума модуля комплексного корреляционного интеграла. По следующему синхронизированному импульсу нуль- пересечения переключается в состояние 5 О второй D-триггер 45 и в состояние 1 третий D-триггер 46. Сигнал с его выхода переключает постоянное запоминающее устройство 41, устанавливая

10

Блок 27 определения отношения сигнал/шум (фиг. 3) работает следующим образом. ,

С началом режима поиска максимума квадрата модуля комплексного корреляционного интеграла сигнал, поступающий на четвертый вход 33 блока 27, разрешает прохождение импульсов с второго входа 31 блока 27 через втррежим начала формирования комплекс- tO рую схему ИЛИ 61 на вход установки кого корреляционного интеграла. С приходом следующего синхронизированного импульса нуль-пересечения третий D- триггер 46 сбрасывается в нуль, при

в О первого накопительного регистра 52 и снимает блокировку по входу установки в О с первого D-тригге- ра 62, второго накопительного регистэтом устанавливается режим формирова-15 ра 56 и М регистров 50.1-50.М. В рения комплексного корреляционного интеграла. Цикл работы повторяется.

Для определения отношения сигнал/ /щум достаточно принимаемую смесь сигнала с шумом подать на входы двух фильтров: узкополосного и широкополосного, - причем отношение их полос известно и равно К, измерить ее мощность на выходе каждого фильтра и определить отношение сигнал/шум как

KP,-Pi fU -----,

где Р. мощность смеси на кополосного фильтра,

PI РГ +РЫ. ;

Р - мощность смеси на выходе широкополосного фильтра,

Рр - мощность сигнала;

РЫ, ГЬ О(Р)Г;

гистры 50.1-50.М стробирующими импульсами, поступающими на третий вход 32 блока 27, записываются значения Z(fg) (8), последовательно посту20 пающие с выхода квадратора 21 на первый вход 30 блока 27. С йриходом стробирующего импульса, прошедшего на выход схемы 25 сравнения и на второй вход 31 блока 27, устанавливаются

25 в О первый накопи-тельный регистр 52 и счетчик 60, тем самым снимается сигнал переполнения с выхода перено- (9) са счетчика 60, если он был, и разрешается прохождение G импульсов через выходе уз- 30 первую схему ИЛИ 59 (где G - емкость счетчика 60, причем ), а также устанавливается в состояние 1 первый D-триггера 62 - фиксируется факт превышения уровня сигнала порога обнаружения .

35

В первом накопительном регистре 52 последовательно записываются суммы 1...G значений Z(fg). С приходом последнего импульса с выхода схемы 25 сравнения и приходом G стробирующих импульсов на третий вход 32 блока 27 в первом накопительном регистре 52 записывается сумма G значений Z(fj) (8), сгруппированных вокруг максимума

Ршг

-1

,(F)dF;

N(,(F) - энергетический спектр шума;

К

Руг F .-F, РМ-

причем

fj6(F,,F)e(F,, F, ),

где fл - частота принимаемого сигнала .

Обнаружитель-измеритель частоты эквивалентен параллельному соединению набора полосовых фильтров. Для измерения отношения сигнал/шум необходимо сформировать соответствующие фильтры и произвести вычисления по формуле (9).

10

Блок 27 определения отношения сигнал/шум (фиг. 3) работает следующим образом. ,

С началом режима поиска максимума квадрата модуля комплексного корреляционного интеграла сигнал, поступающий на четвертый вход 33 блока 27, разрешает прохождение импульсов с второго входа 31 блока 27 через втррую схему ИЛИ 61 на вход установки

в О первого накопительного регистра 52 и снимает блокировку по входу установки в О с первого D-тригге- ра 62, второго накопительного регист2530

35

0

5

В первом накопительном регистре 52 последовательно записываются суммы 1...G значений Z(fg). С приходом последнего импульса с выхода схемы 25 сравнения и приходом G стробирующих импульсов на третий вход 32 блока 27 в первом накопительном регистре 52 записывается сумма G значений Z(fj) (8), сгруппированных вокруг максимума

P,pCfe).

(10)

где

0

(-I

1, ,

1,1„,-М-И;

-г -так М,

а счетчик 60, досчитав до G, запрещает прохождение импульсов через первую схему ИЛИ 59. Таким образом, формируется узкополосный фильтр с по- c лосой пропускания и оценивается мощность (10) смеси сигнала с шумом на его выходе.

Одновременно все L значений Z(fg) (8) поступают на вход второго суммаU . 137 тора 55 и во втором накопительном регистре 56 записываются результаты сложения

., +Z(fe), ,L, (11) взамен предыдущей суммы Pj, , , причем Р 0. После прихода L значений Z(fg) (9) во втором накопительном регистре 56 записывается сумма

записывается

ь

Р

Z(fg)

(12)

Таким образом, формируется широкополосный фильтр с полосой пропускания L&f и оценивается мощность (12) смеси сигнала с шумом на его выходе.

По окончании режима поиска максимума квадрата модуля комплексного корреляционного интеграла Z(fj) в буферных регистрах 53 и 57 фиксируются значения Р, (10) и Р (12), а во втором D-триггере 63 - факт обнаружения сигнала. Эта информация поступает на первый 65, второй 58 и третий 64 входы вычислителя 54, где по формуле (9) определяется отношение сигнал/шум,

причем . С выхода второго D-триг- G

гера 63 сигнал поступает также на второй выход 29 блока 27 и может быть использован для индикации обнаружения сигнала. Одновременно происходит установка в О первого D-триггера 62 первого 52 и второго 56 накопительных регистров и регистров 50.1-50.М, после чего блок 27 определения отношения сигнал/шум готов к следующему циклу работы. При конструкция блока 27 определения отношения сигнал/шум может быть упрощена за счет исключения блоков 60, 59, 51, 50.

Формула изобретения

Цифровой обнаружитель-измеритель частоты по авт. св. № 1092733, отличающийся тем, что, с целью расширения функциональных возможностей, в него введен блок определения отношения сигнал/шум, содержащий последовательно соединенные М реги

t5

0

25

0

стров, первьш сумматор, первый накопительный регистр, выход которого дополнительно соединен с вторым входом первого сумматора, первый буфер- ный регистр и вычислитель, выход которого является выходом блока, и последовательно соединенные второй сумматор, вход которого соединен с входом первого из М регистров, второй W накопительный регистр, выход которого дополнительно соединен с вторым входом второго сумматора, и второй буферный регистр, выход которого соединен С вторым входом вычислителя, а также первую схему ИЛИ, счетчик, выход переноса которого соединен с первым входом первой схемы ИЛИ, вторую схему WM, выход которой соединен с входом установки в О первого накопительного регистра, первый D-триг- гер, на D-вход которого подан уровень логической единицы, и второй D-триг- гер, D-ВХОД которого соединен с выходом первого В-триггера, а выход соединен с третьим входом вычислителя, объединены первый вход второй схемы ИЛИ, синхронизирующий вход первого DL-триггера и вход установки в О счетчика, объединены второй вход первой схемы ИЛИ и синхронизирующие входы второго накопительного регистра и М регистров, объединены второй вход второй схемы ИЛИ, синхронизирующие входы второго D-триггера, первого и второго буферных регистров и входы установки в О первого D-триггера, второго накопительного регистра и М регистров, выход первой схемы ШШ соединен с синхронизирующим входом

0 счетчика и первого накопительного регистра, причем выходы блоков устройства сравнения, квадратора и управляющие входы блоков устройства сравнения, второго коммутатора, соеди5 нены соответственно с входами счетчика, второго сумматора, вторым входом первой схемы ИЛИ, вторым входом второй схемы ИЛИ блока определения отношения сигнал/шум.

5

| Устройство для автоподстройки частоты и цифровой обнаружитель-измеритель частоты | 1982 |

|

SU1092733A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-01-30—Публикация

1986-08-27—Подача