Изобретение относится к преобразователям цифрового кода в фазовый сдвиг сигнала переменного тока и может быть использовано в устройствах автоматики и измерительной техники, в частности в преобразователях уголфаза-код.

Известно устройство, содержащее кодовый регистр, блок ключей, N-разрядный блок фазосдвигаклцих цепочек, соединенных мезвду собой с помощью ключевых элементов блока ключей, управляющие вхо.цы которых подключены к выходам кодового регистра 1 .

Недостатком этого устройства является низкая точность преобразования, обусловленнсш нестабильностью элементов фазосдвиганвдих цепочек.

Известен также преобразователь

код-фаза, содержащий генератор импульсов, два двоичных счетчика, вводное устройство, вход которого ггодк. лючен к выходу первого двоичного счетчика, а выход - ко входу второго двсжчного счетчика, два формирователя участков аппроксимации и частот, подключенных к выходам двоичных счетчиков, два реверсивных счетчика и дв П е еобразователя код-напряжение, полключенных к выходам соответствующих реверсивных счетчиков 2| .

Недостатком устройства является зависимость точности преобразования от быстродействия двоичного счетчика, что не позволяет получить точность преобразования при высокой частоте (превышающей 1000 Гц) выходного полезного сигнала цифрового фазовращателя, а также его сложность , что усложняет его практическую реализацию.

Цель изобретения - повышение точности преобразователя и упрощение его конструкции.

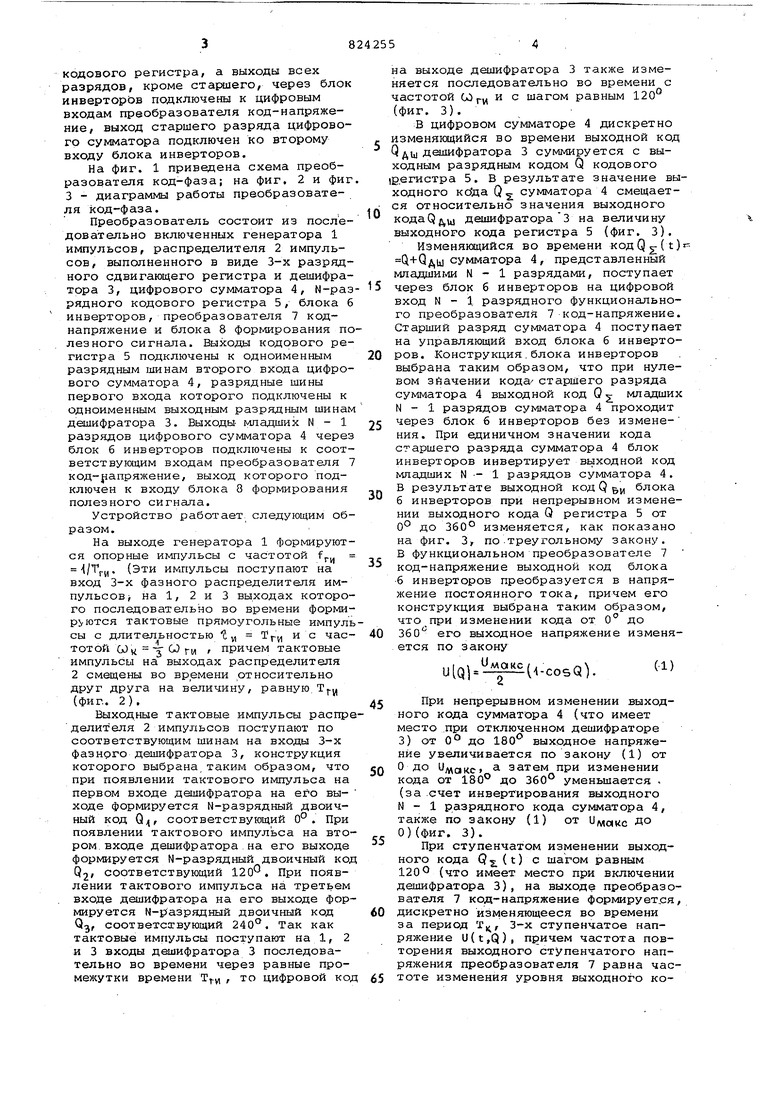

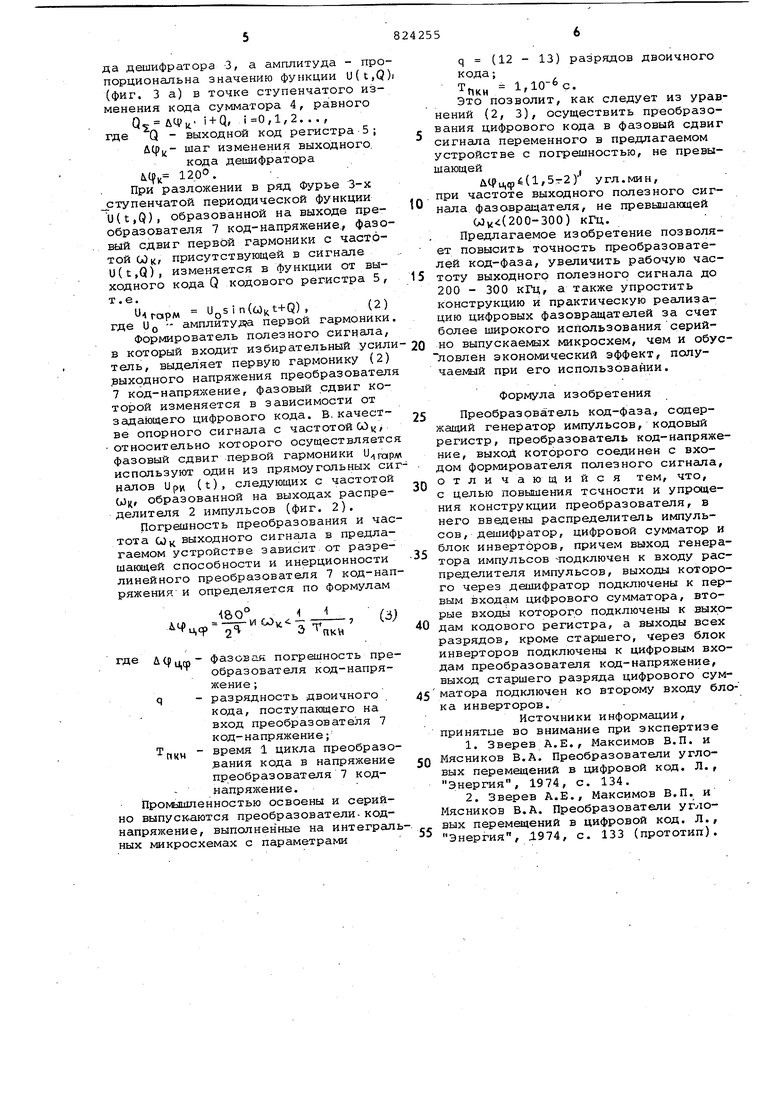

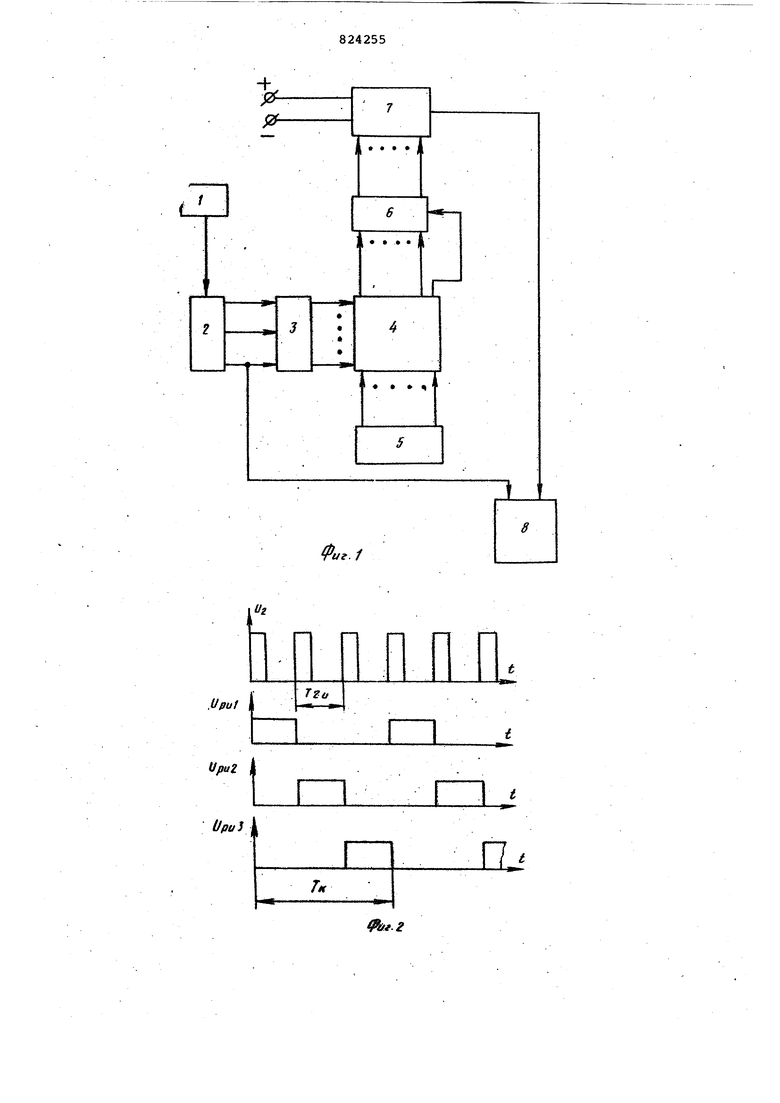

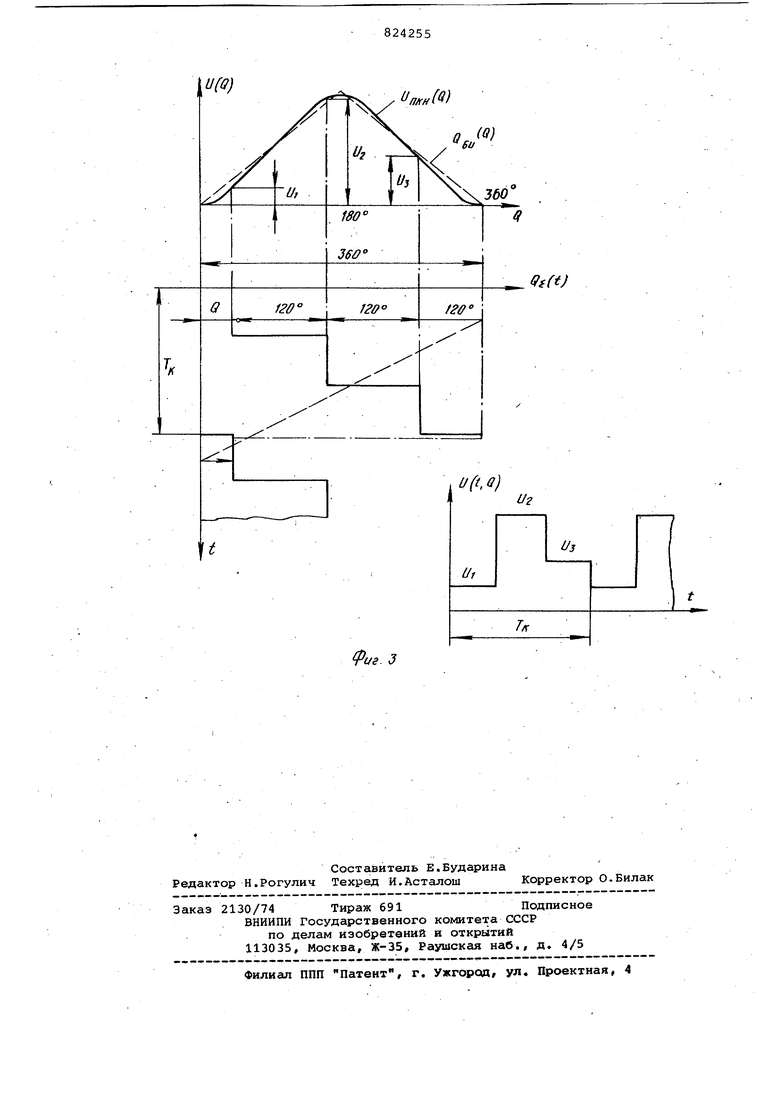

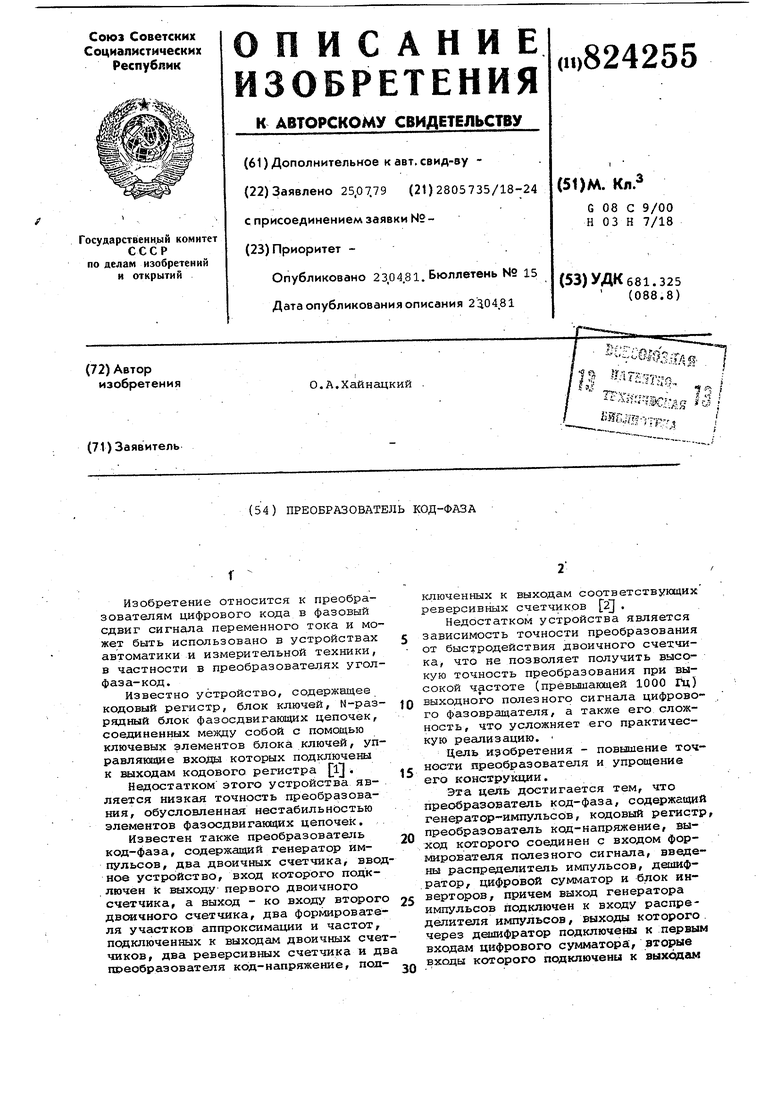

Эта дель достигается тем, что преобразователь код-Фаза, содержащий генератор-импульсов, кодовый регистр преобразователь код-напряжение, выход которого соединен с входом формирователя полезного сигнсша, введены распределитель импульсов, дешифратор, цифровой сумматор и блок инверторов, причем выход генератора импульсов подключен к входу распределителя импульсов, выходы которого через дешифратор подключены к первым входам цифрового сумматора, вторые входы которого подключены к выходам кодового регистра, а выходы всех разрядов, кроме старшего, через блок инверторов подключены к цифровым входам преобразователя код-напряжение, выход старшего разряда цифрового сумматора подключен ко второму входу блока инверторов. На фиг. 1 приведена схема преобразователя код-фаза; на фиг. 2 и фиг 3 - диаграммы работы преобразователя код-фаза. Преобразователь состоит из последовательно включенных генератора 1 импульсов, распределителя 2 импульсов, выполненного в виде 3-х разрядного сдвигающего регистра и дешифратора 3, цифрового сумматора 4, N-раз рядного кодового регистра 5, блока б инверторов, преобразователя 7 коднапряжение и блока 8 формирования по лезного сигнала. Выходы кодового регистра 5 подключены к одноименным разрядным шинам второго входа цифрового сумматора 4, разрядные шины первого входа которого подключены к одноименным выходным разрядным шинам дешифратора 3. Выходы- младших N - 1 разрядов цифрового сумматора 4 через блок б инверторов подключены к соответствующим входам преобразователя код-рапряжение, выход которого подключен к входу блока 8 формирования полезного сигнала. Устройство работает следующим образом. На выходе генератора 1 формируются опорные импульсы с частотой f (/Trj,. (Эти импульсы поступают на вход 3-х фазного распределителя импульсов j на 1, 2 и 3 выходах которого последовательно во времени формируются тактовые прямоугольные импул сы с длительностью t vt 1ги ° частотой GJ« -г СО ги причем тактовые импульсы на выходах распределителя 2 смещены во времени относительно друг друга на величину, равную. Т,.j, (фиг. 2). Выходные тактовые импульсы распр делителя 2 импульсов поступают по соответствующим шинам на входы 3-х фазного дешифратора 3, конструкция которого выбрана таким образом, что при появлении тактового импульса на первом входе дешифратора на его выходе формируется N-разрядный двоичный код QH, соответствующий 0°. При появлении тактового импульса на вто ром входе дешифратора на его выходе формируется М-разрядный двоичный код Q2, соответствующий 120. При появлении тактового импульса на третьем . входе дешифратора на его выходе фор мируется N-разрядный двоичный код соответствующий 240°. Так как тактовые импульсы поступают на 1, 2 и 3 входы дешифратора 3 последовательно во времени через равные промежутки времени , , то цифровой ко а выходе дешифратора 3 также измеяется последовательно во времени с астотой СО ги и с шагом равным 120° (фиг. 3). В цифровом сумматоре 4 дискретно зменяющийся во времени выходной код ди| дешифратора 3 суммируется с выодным разрядным кодом Q кодового егистра 5. В результате значение выодного кбда. Q сумматора 4 смещаетя относительно значения выходного кoдaQ s цJ дешифратора 3 на величину выходного кода регистра 5 (фиг. 3). Изменянвдийся во времени кoдQ2-(t)г- Ц+Оди1 сумматора 4, представленный мпадши1у1и N - 1 разрядами, поступает через блок 6 инверторов на цифровой вход N - 1 разрядного функционального преобразователя 7 код-напряжение. Старший разряд сумматора 4 поступает на управляющий вход блока 6 инверторов. Конструкция.блока инверторов выбрана таким образом, что при нулевом зйачении кода старшего разряда сумматора 4 выходной код младших N - 1 разрядов сумматора 4 проходит через блок б инверторов без изменения. При единичном значении кода старшего разряда сумматора 4 блок инверторов инвертирует выходной код младших N - 1 разрядов сумматора 4. Б результате выходной код Q блока б инверторов при непрерывном изменении выходного кода Q регистра 5 от до 360° изменяется, как показано на фиг. 3, по.треугольному закону. В функциональном преобразователе 7 код-напряжение выходной код блока б инверторов преобразуется в напряжение постоянного тока, причем его конструкция выбрана таким образом, изменении кода от 0° до 360 его выходное напряжение изменяется по закону UlQh - T H-cosQ). При непрерывном изменении выходного кода сумматора 4 (что имеет место при отключенном дешифраторе 3) от 0° до 180 выходное напряжение увеличивается по закону (1) от О до ( затем при изменении кода от 180° до 360° уменьшается . (за .счет инвертирования выходного N - 1 разрядного кода сумматора 4, также по закону (1) от УЛ/ЮКС ДО 0)(фиг. 3). При ступенчатом изменении выходного кода Q(t) с шагом равным 120О (что имеет место при включении дешифратора 3), на выходе преобразователя 7 код-напряжение формирует.ся, дискретно изменяющееся во времени за период Т, 3-х ступенчатое напряжение U(t,Q), причем частота повторения выходного ступенчатого напряжения преобразователя 7 равна частоте изменения уровня выходного кода дешифратора 3, а амплитуда - про порциональна значению функции U(t,Q (фиг. 3 а) в точке ступенчатого изменения кода сумматора 4, равного 0 utVii i + Q, ,l,2. .., где Q - выходной код регистра-5; ЛСр,- шаг изменения выходного. кода дешифратора ( 120°. При разложении в ряд Фурье 3-х ступенчатой периодической функции U(t,Q), образованной на выходе преобразователя 7 код-напряжение., фазо вый сдвиг первой гармоники с частотой СО к, присутствующей в сигнале U(t,Q), изменяется в функции от выходного кода Q кодового регистра 5, U sintoKt+Q),(2) где DO - амплитудз а первой гармоники Формирователь полезного сигнала, в который входит избирательный усил тель, выделяет первую гармонику (2) .выходного напряжения преобразовател 7 код-напряжение, фазовый .сдвиг которой изменяется в зависимости от задак)щего цифрового кода. В. качестве опорного сигнала с частотой относительно которого осуществляетс фазовый сдвиг первой гармоники используют один из прямоугольных си налов Upn (t), следующих с частотой СлЗц, образованной на выходах распределителя 2 импульсов (фиг. 2). Погрешность преобразования и час тота со к выходного сигнала в предлагаемом устройстве зависит от разрешакядей способности и инерционности линейного преобразователя 7 код-нап ряжения и определяется по формулам MGOvt-tцср 2 где UCpiicp Фазовая погрешность преобразователя код-напряжение ; q - разрядность двоичного кода, поступающего на вход преобразователя 7 к од-напряжение; Т(,цц - время 1 цикла преобразо.вания кода в напряжение преобразователя 7 коднапряжение. Промышленностью освоены и серийно выпускаются преобразователи- коднапряжение, выполненные на интеграль ных микросхемах с параметрами q (12 - 13) разрядов двоичного кода; 1,10-6с. Это позволит, как следует из уравнений (2, 3), осуществить преобразования цифрового кода в фазовый сдвиг сигнала переменного в предлагаемом устройстве с погрешностью, не превышающей(1/5-2) угл.мин, . при частоте выходного полезного сигнала фазовращателя, не превышающей 00к(200-300) кГц. Предлагаемое изобретение позволяет повысить точность преобразователей код-фаза, увеличить рабочую частоту выходного полезного сигнала до 200 - 300 кГц, а также упростить конструкцию и практическую реализацию цифровых фазовращателей за счет более широкого использования серийно выпускаемых микросхем, чем и обус ловлен экономический эффект, получаемый при его использовании. Формула изобретения Преобразователь код-фаза., содержащий генератор импульсов, кодовый регистр, преобразователь код-напряжение, выход которого соединен с входом формирователя полезного сигнала, отличающийся тем, что, с целью повышения точности и упрощения конструкции преобразователя, в него введены распределитель импульсов, дешифратор, цифровой сумматор и блок инверторов, причем выход генератора импульсов -подключен к входу распределителя импульсов, выходы которого через дешифратор подключены к первым входам цифрового сумматора, вторые входы которого подключены к выхрдам кодового регистра, а выходы всех разрядов, кроме старшего, через блок инверторов подключены к цифровым входам преобразователя код-напряжение, выход старшего разряда цифрового сумматора подключен ко второму входу блока инверторов... Источники информации, принятие во внимание при экспертизе 1.Зверев А.Е., Максимов В.П. и Мясников В.А. Преобразователи угловых перемещений в цифровой код. Л., Энергия, 1974, с. 134. 2.Зверев А.Е., Максимов В,П. и Мясников В.А. Преобразователи угловых перемещений в цифровой код. Л., Энергия, 1974, с. 133 (прототип).

.Upul

UpuZ UpoJ

I1

11.

n

UaffH(Q)

./

fpus.S

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоичного кода в код магнитного носителя | 1980 |

|

SU1148572A3 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Устройство для логарифмирования чисел | 1984 |

|

SU1257846A1 |

| Устройство для идентификации характеристик четырехполюсников | 1983 |

|

SU1188676A1 |

| Преобразователь код-угол | 1984 |

|

SU1264345A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1977 |

|

SU732853A1 |

| Многоканальное устройство приема сложных сигналов | 1989 |

|

SU1786664A1 |

| Преобразователь угла поворота вала в код | 1980 |

|

SU896654A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННОГО СИГНАЛА | 1996 |

|

RU2110145C1 |

| Преобразователь напряжения в код | 1979 |

|

SU851767A1 |

Авторы

Даты

1981-04-23—Публикация

1979-07-25—Подача