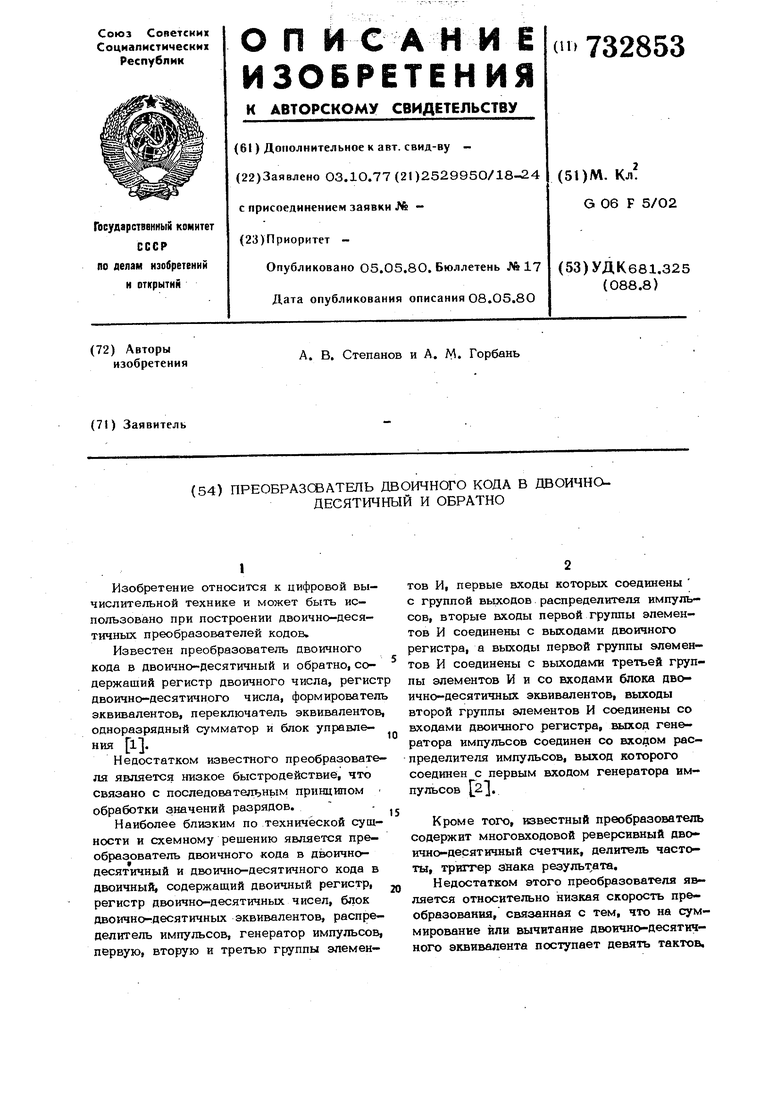

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении двоично-десятичных преобразователей кодов. Известен преобразователь двоичного кода в двоично-десятичный и обратно, содержащий регистр двоичного числа, регис двоично-десятичного числа, формировател эквивалентов, переключатель эквивалентов одноразрядный сумматор и блок управления l. Недостатком известного преобразовате ля является низкое быстродействие, что связано с последовательным принципом обработки значений разрядов. Наиболее близким по технической сущности и схемному решению является преобразователь двоичного кода в двоичнодесятичный и двоично-десятичного кода в двоичный, содержащий двоичный регистр, регистр двоично-десятичных чисел, блок двоично-десятичных эквивалентов, распределитель импульсов, генератор импульсов первую, вторую и третью группы элементов и, первые входы которых соединены с группой вьрсодов распределителя импульсов, вторые входы первой группы элементов И соединены с выходами двоичного регистра, а выходы первой группы элементов И соединены с выходами третьей группы элементов И и со входами блока двоично-десятичных эквивалентов, выходы второй группы элементов И соединены со входами двоичного регистра, выход генератора импульсов соединен со входом распределителя импульсов, выход которого соединен с первым входом генератора импульсов 2., Кроме тогю, известный преобразователь содержит многовходовой реверсивный двоично-десятичный счетчик, делитель частоты, триггер знака результ,ата. Недостатком этого преобразователя является относительно низкая скорость преобразования, связанная с тем, что на суммирование или вычитание двоично-десятичного эквивалента поступает девять тактов. Цель изобретения - увеличение скорости преобразования. Это достигается за счет того, что пре образователь содержит двоично-десятичный сумматор, схему сравнения, четвертую группу элементов И, элемент ИЛИ, первый и второй элементы И, элемент НЕ, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом первого элемента И и вторыми входами всех элементов И второй группы, выход элемента ИЛИ соед1шен с первыми входами всех элементов И четвертой группы, вторые входы- которых сое динены с выходами двоично-десятичного сумматора, подключенными к первой группе входов схемы сравнения, выходы элементов И четвертой группы соединены с входами регистра двоично-десятичных чисел, выходы которого соединены с первыми входами двоично-десятичного сумматора вторые входы которого соединены с выхо дами блока двоично-десятичных эквивалентов, первый и второй выходы схемы сравнения соответственно соединены с первыми входами первого и второго элементов И, вторые входы которых соединены с . , входом элемента НЕ и со вторыми входами всех элементов И четвертой группы, выход второго элемента И соединен со вторым входом генератора импульсов, вто рая группа входов схемы сравнения соединена со входами преобразователя. На чертеже изображена функциональная схема устройства. Устройство преобразования разрядного двоичного числа в двоично-десятичное и обратно содержит двоичный регистр 1, блок 2 двоично-Десятичных эквивалентов, двоично-десятичный сумматор 3, регистр 4 двоично-десятичных чисел, распределитель 5 импульсов, схему 6 сравнения, шины 7 двоично-десятичного числа, управляющую шину. 8, генератор 9 импульсов, первый и второй элементы И 10 и 11, элемент ИЛИ 12, элемент НЕ 13, шины 14 двоичного числа, первую, вторую, третью и четвертую группы элементов И ISIS. Выходы распределителя подключены на грутшы элементов И 15 и 17, на вторые входы которых подключены выходы разрядов двоичного регистра 1. Выходы элементов И из групп 15 и 17 подключены на входы блока 2 двоично-десятичных эквивалентов, выходы которого подключены на входы двоично-десятичного сумматора 3, Выходы сумматора подключены через вентили группы элементов И 18 на входы сумматора, Выходы сумматора подключены также на входы схемы сравнения 6, на вторые входы которой подключены шины 7 двоично-десятичного числа. Выходы распределителя импульсов подключены также на входы элементов И 16 второй группы, на вторые входы которых подключен элемент И 10, выход сигнала больше, равно схемы сравнения. Выход сигнала равенства схемы сравнения 6 через второй элемент И 11 подключен на вход сброс генератора импульсов 9, Выход элемента И 10 через элемент ИЛИ 12 поцключен на входы вентилей элементов И 18 чет вертой группы. На элемент ИЛИ 12 поступает также сигнал с БЬЕХОДЗ элемента НЕ 13. Устройство рабсгТает следующим образом, В режиме преобразования двоичного числа в двокчно-десят чное на улравляк щую шиггу 8 подается нулевой потенциал. Через шкны 14 в двоичный регистр 1 ваписывается код преобразуемого двоичного числа. Затем включается генератор 9 импульсов. Превый импултэС с первого выхода распределителя импульсов опрашивает старший разряд двоичного регистра. При единичном значении разряда сиггшл поступает на вход блока 2 двоично-десятичных эквивалентов, с выходов которого десятичный эквивалент старшего разряда з.аносит- ся в двоично-десятичный сумматор 3. Следующий импульс Со второго выхода распределителя импульсов опрашивает следующий разряд регистра 1 и при наличии в нем единицы сигнал с выхода элемента И из группы 15 поступает-на вход блока эквивалентов. С выходов последнего десятичный эквивалент второго разряда поступает в сумматор 3,. где суммируется с предыдущц1у) значением и т,д. После опроса всех разрядов импульс с выхода распределителя вьжлючает генератор импульсов, В режиме преобразования двоично-десятичного числа в двоичное на шину 8 подается единичный потенциал. На 7 подается потенциальный двоично-десятичный код преобразуемого числа, триггеры регистра 1 устанавливаются в нуль. Затем включается генератор импульсов и импульс с первого выхода распредели теля импульсов через открытый элемент И из группы 17 поступает на блок 2 эквивалентов, С выхода блока 2 на сумматор поступает двоично о.есятичный эквива- лент старше о двоичного разряда. Если код на шинах 7 равен коду, поступающему с сумматора, сигнал .с выхода равенства схемы 6 сравнения выключает генератор импульсов. Если код на шинах 7 больше кода, поступающего с сумматора, то открыты элементы И 18 четвертой группы, элемент И старшего разряда в группе 16. По окончании первого тактового импульса в регистр 4 дво{гчно-десятичного числа (так же как и в случае равенства кодов) запишется десятичный эквивалент старшего двоичного разряда и единица в старший разряд двоичного регистра. Если код на шинах 7 меньше кода поступающего с выходов сумматора, то регистр 4 и регистр 1 после первого такта не изменяет своих значений. Второй тактовый импульс через открытый эл мент И из группы 17 поступает на еле- дующий вход блока эквивалентов 2, с выходов которого на сумматор поступает десятичный эквивалент следующего двоичного разряда. С выходов сумматора на схему 6 сравнения поступает сумма экви валента второго разряда и содержимого регистра. Если код суммы равен коду на шинах 7, то сигнал со схемы 6 сравнения выключает генератор импульсов. Если код на шш1ах 7 больше кода, поступающе го с выходов сумматора, то открыты эле менты И из группы 18 и элемент И ii3 группы 16. По окончании второго тактового импульса в регистр 4- двоично-десятичного числа запишется упомянутая сумма и единица во второй разряд регистра 1. В противном случае содержимое регис ра сумматора и регистра 1 не изменится и т.д. Таким образом, после выключения генератора выходным сигналом распределителя импульсов 5 (или ранее) в регист ре 1 будет содержаться двоичный эквивалент преобразуемого двоично-десятичного .числа. Быстродействие устройства при прямо и обратном преобразовании остается одинаковым, поскольку число тактов работы устройства в обоих режимах равно числу разрядов преобразуемых чисел, что в 9 раз количества тактов преобразо вателя. Формула изобретения Преобразователь двоичного кода в двоично-десятичный и обратно, содержащий двоичный регистр, регистр двоично-десятичных чисел, блок двоично-десятичных эквивалентов, распределитель импульсов, генератор импульсов, первую, вторую и третью группы элементов И, первые входы которых соединены с группой выходов распределителя импульсов, вторые входы элементов И первой группы соединены с выходами двоичного регистра, а выходы элементов И первой группы соединены с выходами элементов И третьей группы и со входами блока двоично-десятичных эквивалентов, выходы элементов И второй группы соединены со нходами двоичногорегистра, выход генератора импульсов соеД1шен со входом распределителя импульсов, выход которого соединен с первым входом генератора импульсов, отличающийся тем, что, с целью. увеличения скорости преобразования, он содержит двоично-десятичный сумматор, схему сравнения, четвертую группы элементов И, элемент ИЛИ, первый и второй элементы И и элемент НЕ, выход которого соеди нен с первым входом элемента ИЛИ, второй вход которого соединен с выходом nef вого элемента И и вторыми входами всех элементов И второй группы, выход элемента ИЛИ соединен с первыми входами всея элементов И четвертой группы, вторые входы которых соединены с выходами двоично-десятичного сумматора, подключенными к первой группе входов схемы сравнения, выходы элементов И четвертой группы соединены с входами регмстпя пвоично-десятичных чисел, выходы которого соединены с первой группой входов аьо.гч но-десятичного сумматора, вторая группа входов которого .соединена с выходами блока двоично-десятичных эквивалентов, первый и второй выходы схемы сравнения соответственно соединены с первыми входами первого и второго элементов И, вторые входы которых соединены с входом элемента НЕ и со вторыми входами всеэс элементов И четвертой группы, выход второго элемента И соединен со вторым входом генератора имIiyjл.coв, вторая группа входов схемы сравнения соединена со входами преобразователя. Источники информации, принятые во внимание при экспертизе 1. Авторсксо свидетельство СССР № 526886, кг. G 06 F 5/02,26.02.74. 2. Авторское свидетельство СССР по заявке М 2468249/24, 1976. Г t i вЛ вЛ ffli t-S--S /5 i-5----J 1.J

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1983 |

|

SU1149243A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1084779A1 |

| Устройство для преобразования двоичного кода в двоично-десятичношестидесятиричный | 1977 |

|

SU734668A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

Авторы

Даты

1980-05-05—Публикация

1977-10-03—Подача