группы элементов ИСКШОЧАЩЕЕ ИЛИ, первые входы которых являются информационными входами входного преобразователя, вторые входы элементов ЙСКЛЮЧАЩЕЕ ИЛИ группы соединены с управляющим входом входного преобразователя, а выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы являются выходами входного преобразователя.

3.Устройство по п.1, о т л и чающееся тем, что в нем блок вычисления текущей разности содержит вычитатель и первый и второй узлы вычисления числа единиц, каждый из которых состоит из элемента И и элемента ИСКЛКНАЩЕЕ ИЛИ, первьй и второй входы которого соединены соответственно с первым и вторым входами элемента И и являются информационны o входами блока вычисления текущей разности, выходы которого соединены с выходами вычитателя, входы переноса и первого разряда первой и второй групп которого соединены с входом логической единицы блока вычисления теку1дей разности, входы вторых разрядов первой и второй групп вычитателя соединены соответственно с выходами элементов ИСКЛЮЧАЮЩЕЕ Ш1И, входы третьих разрядов первой и в.торой групп вычитателя соединены соответственно с выходами элементов И, sxot ды чегвертых разрядов первой и второ групп вычитателя соединены соответственно с входами нуля и единицы блока вычисления текущей разности.

4.Устройство по п.Т, о т л и ч аю щ е е с я тем, что в нем одноразрядная схема сравнения состоит из элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента НЕi выход которого является выходом одноразрядной схемы сравнения, входы которой являются входами элемента ИСКШОЧАЩЕЕ ИЛИ, выход которого соединен со входом элемента НЕ.

5.Устройство по П.1,. о т л и чающееся тем, что в нем входной преобразователь и блок вычисления текущей разности вьтолнены в виде постоянного запоминакицего устройства, адресные входы младших разрядов которого соединены с информационными входами устройства, адресный вход старшего разряда является дополнительным информационным входом входного преобразователя, выходы которого соединены с группой выходов младших разрядов постоянного запоминающего устройства, группа выходов старших разрядов которого является выходами блока вычисления текущей разности.

6.Устройство по П.1, о т л и чающееся тем, что в нем бло вычисления текущей разности содержи группу входных элементов НЕ, дешифратор комбинаций с разностью отличной от +1t две группы элементов НЁ-ШШ и группу элементов НЕ, выходы которых являются выходами старших разрядов блока вычисления текущей разности, выход первого разряда которого соединен с входом логической единицы, выход группы младших разрядов &тока вычисления текущей разности соединен с выходами элементов НЕ-ИПИ первой группы, выходы элементов НЕ-ИЛИ второй группы соединены с входами соответствующих элементов НЕ второй группы, входы элементов ЙЕ-ИЛИ обеих групп соединены с соответствующими группами выходов дешифратора комбинаций с разностью отличной от +1, первая группа входов которого соединена с информационными входами блока вычисления текущей разности и с входами входных элементов НЕ группы, выходы которых соединены с второй группой входов девшфратора Комбинаций с разностью отличной от -f 1.

7.Устройство по П.1, отличающееся тем, что в нем блок вычисления текущей разности содержит группу элементов НЕ, элемент НЕ-ИЛИ и дешифратор комбинации с разностью 2, первая группа входов которого соединена с информационными входами блока вычисления текущей разности и с входами элементов НЕ группы, вых;оды которых соединены с второй группой входов дешифратора комбинаций

с разностью 2, первый выход которого является выходом старшего разряда блока вычисления текущей разности, выход младшего разряда которого соединен с выходом элемента НЕ-ИЛИ, входы которого соответственно соединены со всеми выходами , кроме первого, дешифратора комбинаций с разностью 2.

Изобретение относится к цифровой вычислительной технике и может быть

использовано при построении устройств преобразования информации в коды, используемые магнитными носителями. 5

Известно устройство для преобразования двоичного кода в код магнитного носителя, содержащее два генератора импульсов, модулятор, кодирующее устройство, триггер Шмидта,фор- fO мирователь импульсов, два триггера с соответствующию связями PJ ,

Недостаток известного устройства заключается в невозможности слежения и минимизации постоянной состав- |5 ляющей кодовой посл1едовательности.

Наиболее близким к предлагаемому является устройство преобразования двоичного кода в код магнитного носителя, содержащее входной преобра- |0 зователь и сдвиговый регистр, информационные входы которого соединены с выхода ш входного преобразователя, информащ1онш 1е входы которого соединены с информационными входами уст- 25

ройства, первый тактовьй вход которого соединен с тактовым входом сдвигового регистра, выход которого является выходом устройства.

Кроме того, известное устройство 30 содержит управлякшпгю память, блок декодирования, память специальных символов и счетчик.

Недостаток известного устройства также состоит в невозможности слеже- 31$ ния и минимизации постоянной составляющей кодовой последовательности.

Цель изобретения - распшремие v класса решаемых задач за счет обеспечения минимизации постоянной состав- 40 лякядей хранимых кодовых последовательностей .

Поставленная цель достигается тем, что в устройство для преобразования двоичного кода в код магнитно- 45 го носителя, содержащее входной преобразователь и сдвиговьй регистр,информационные входы которого соединены с выходами входного преобразозвателя информационные входы которого соеди- 50 нены с информационными входа в1 уст-; ройства, первый тактовый вход кото-i рого соединен с тактовьм входом сдвигового регистра, выход которого является выходом устройства, введены .55 блок вычисления текущей разности,Ин- тегратор разности, состояний из сумматора и регистра, группа злемен- .

тов ИСКЛЮЧАЮЩЕЕ ИЛИ, одноразрядная схема сравнения и блок управления сдвигом, содержапщй два D-триггера и элемент И-НЕ, первый и второй входы которого соединены соответственно с инверсным выходом первого и прямым выходом второго D-триггеров, синхровходы которых соединены с первым тактовьм входом устройства, второй Tai;:товьй вход которого соединен с тактовым входом регистра и с D-входом первого D-триггера, прямой выход которого соединен с D-входом второго D-триггера, выход злемента И-НЕ соединен с управляющим входом сдвигового регистра, дополнительный информационный вход которого соединен с выходом одноразрядной схемы сравнения, с -управляющим входом входного преобразователя и первыми входами злемёнтов ИСКЛОЧАЩЕЕ ИЛИ группы, вторые входы которых соединены соответственно с выходами старших разрядов блока вычисления .текущей разности, .информационные входы которого соединены соответственно с информационными входами устройства, а выходы младшего и старшего разрядов блока вычисления текущей разности соединены соответственно с входами младшего разряда первой группы входов сумматора и с первый входом одноразрядной схемы сравнения, второй вход которой соединен с выходом старшего разряда регистра, входа которого соединены с выхода сумматора, входы старших разрядов первой группы которого соединены с выходами элементов ИСКЛКНАЮЩЕЕ ИЛИ группы, входы нуля и единицы блока вычисления текущей разности ;Являются выходами нуля и единицы устройства, выходы регистра соединенны с входами второй группы суммато ра,.

; Входной преобразователь вьшолнен ;В виде группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы которых являются информационными входами входного преобразователя, вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединены с управляющим входом входного преобразователя, а выходы элементов ИСКПЮЧАЩЕЕ ИЛИ группы являют.ся выходами входного преобразователя.

Блок вычисления текущей разности содержит вычйтатель и первый и вто1рой узлы вычисления числа единиц, каждьй из которых состоит и элемён-

та И и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй, входы которого соединены соответственно с первым и вторым входами элемента ИСКЛОЧАЮЩЕЕ ИЛИ и являются информационными входами блока вычисления текущей разности, выходы которого соединены с выходами вычитателя, входы переноса и первого разряда первой и второй Групп которого соединены с входом логической единицы блока вычисления текущей разности, входы вторых-разрядов первой и второй групп вычитателя соединены соответственно с выходами элементов ИСКЛЮЧАМДЕЕ ИЛИ, входы третьих разрядов первой и второй групп вычитателя соединены соответственно с выходами элементов И, входы четвертых разрядов первой и второй групп вычитателя соединены соответственно с входами нуля и единицы блока вычисления текущей разности.

Одноразрядная.схема сравнения состит из элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента НЕ, выход которого является выходом одноразрядной схемы сравнения, входы которой являются входами элемента ИСКЛЮЧАЩЕЕ ИЛИ, выход которого соединен со входом элемента НЕ.

I .-

Входной преобразователь и блок вычисления текущей разности выполнен в вчце постоянного запоминающего устройства, адресные входы младших разрядов которого соединены с информационными входами устройства, адресный вход старшего разряда является дополнительным информационным входом входного преобразователя, выходы которого соединены с группой выходов мпадших разрядов постоянного дополнительного устройства, группа выходов старших разрядов которого является выходами блока вычисления текущей разности.

Блок вычисления текущей разности содержит группу входных элементов НЕ, депщфратор комбинаций, с разностью отличной от +1, две группы элемен-. тов НЕ-ИЛИ и группу элементов НЕ, выходы которых являю тся выходами . старших разрядов блока вычисления текущей разности, выход первого разряда которого соединен с входом логической единицы, выход группы мпадших разрядов блока вычисления текущей разности соединен с выходами элементов НЕ-ИЛИ, первой группы, выходы элементов НЕ-ИЛИ второй группы сое- ;

динены с входами соответствующих элементов НЕ второй группы, входы элементов ВЕ-ИЖ обеих групп соединены с соответствующими группами выходов дешифратора комбинаций с разностью отличной от +1, первая группа входов которого соединена с информационными входами блока вычисления текущей разности и с входами входных элементов НЕ группы, выходы которых соединены с второй группой входов дешифратора комбинаций с разностью отличной от +1.

Блок вычисления текущей раз ности содержит группу элементов НЕ, элемент КЕ-4ШИ и дешифратор комбинаций с разностью 2 первая группа входов которого соединена с информационными входаьда блока вьгаисления текущей раз.ности и с входами элементов НЕ группы, выходы которых соединены с второй группой входов дешифратора комбинаций с разностью 2, первый выход которого является выходом старшего разряда блока вычисления текущей разности, выход мпадшего разряда которого соединен с выходом элемен- ; ,та НЕ-ШШ, входы которого соответст-j венНо соединены со всеми выходами, кроме первого.дешифратора комбйна,ций с разностью 2.

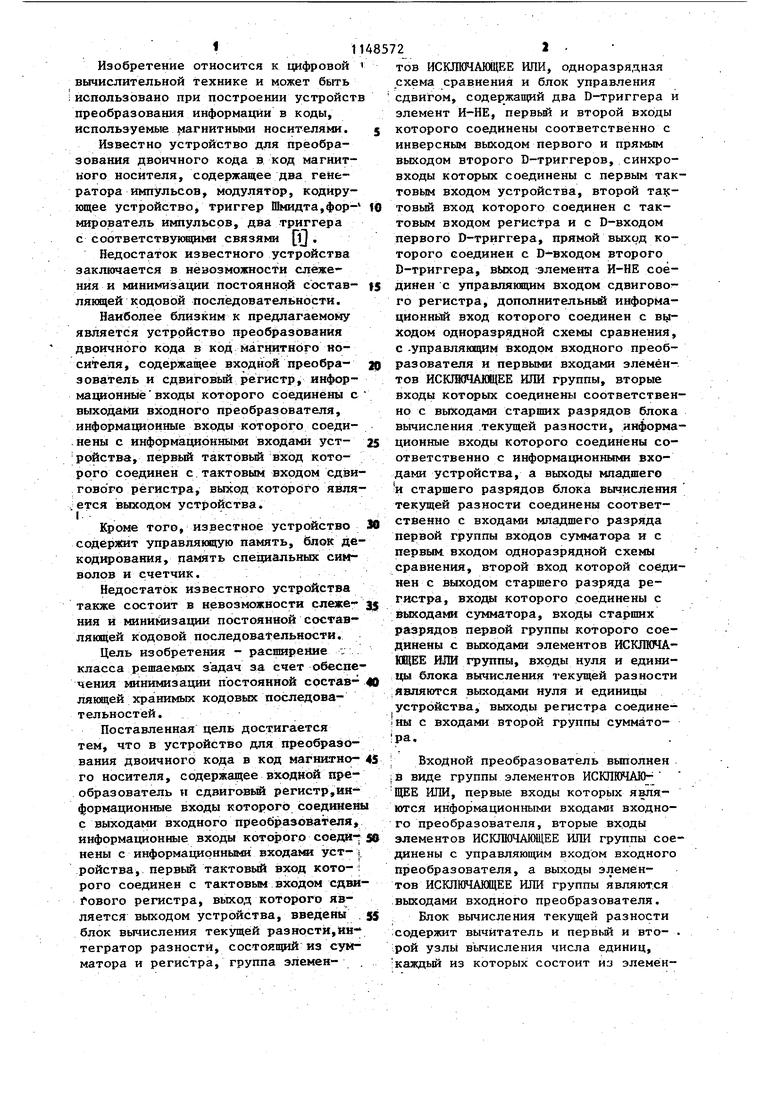

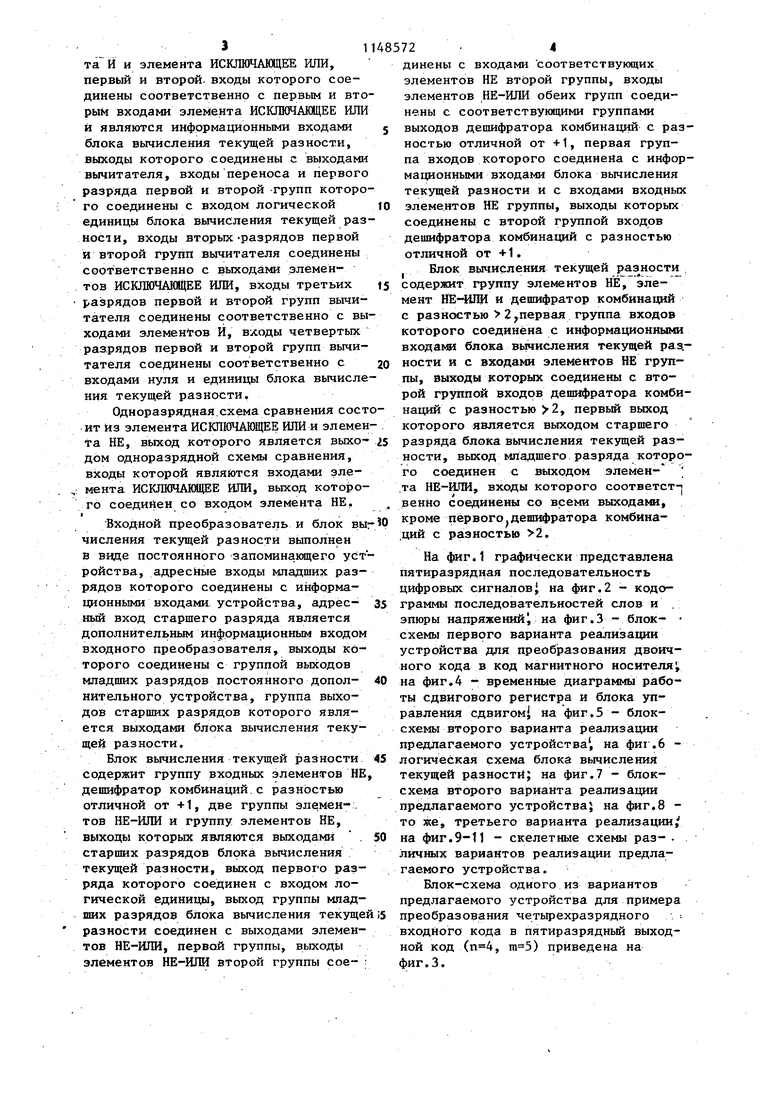

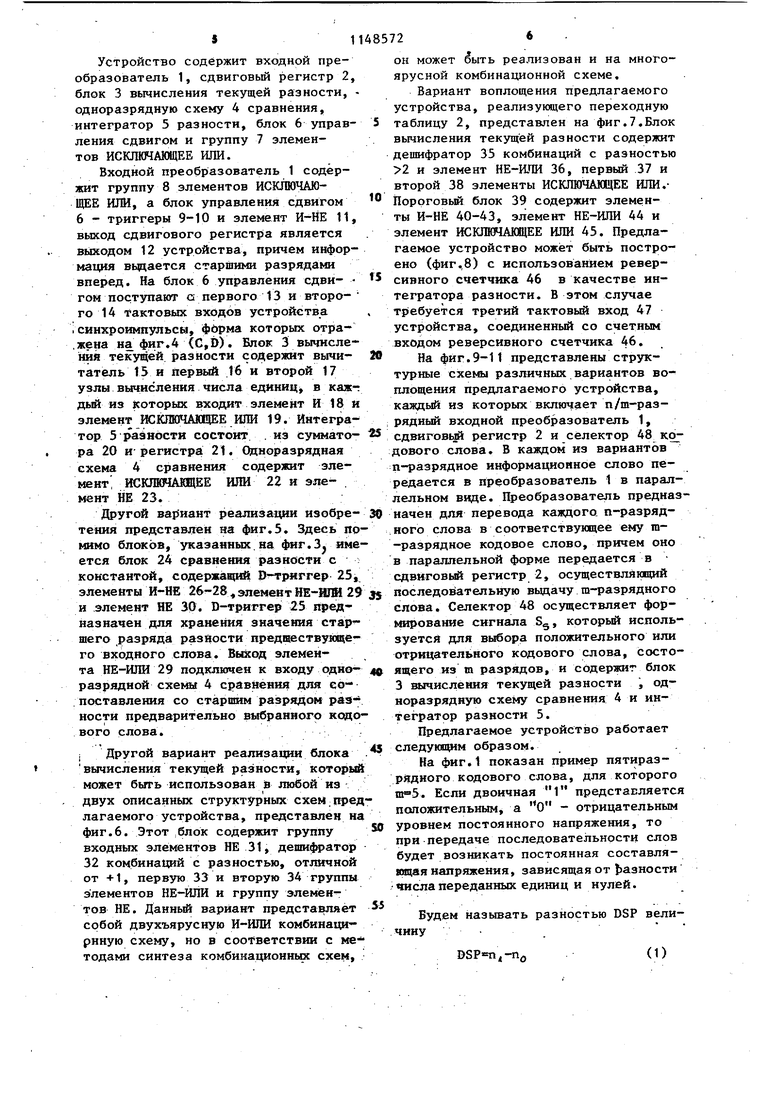

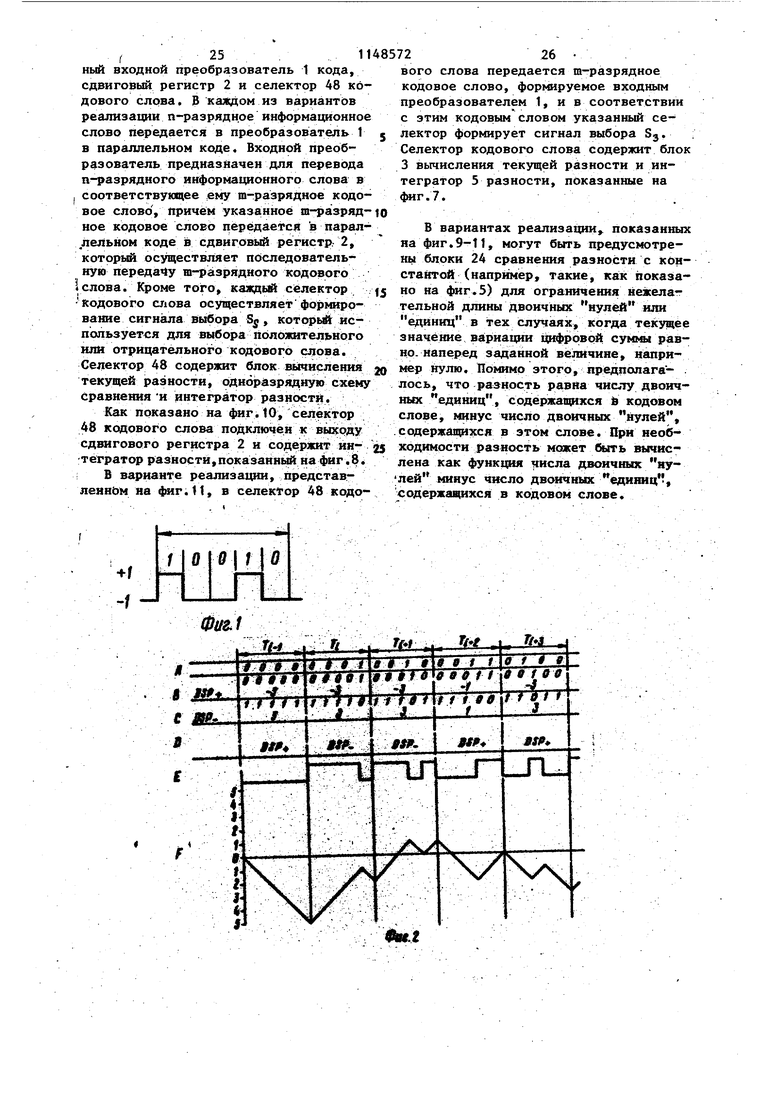

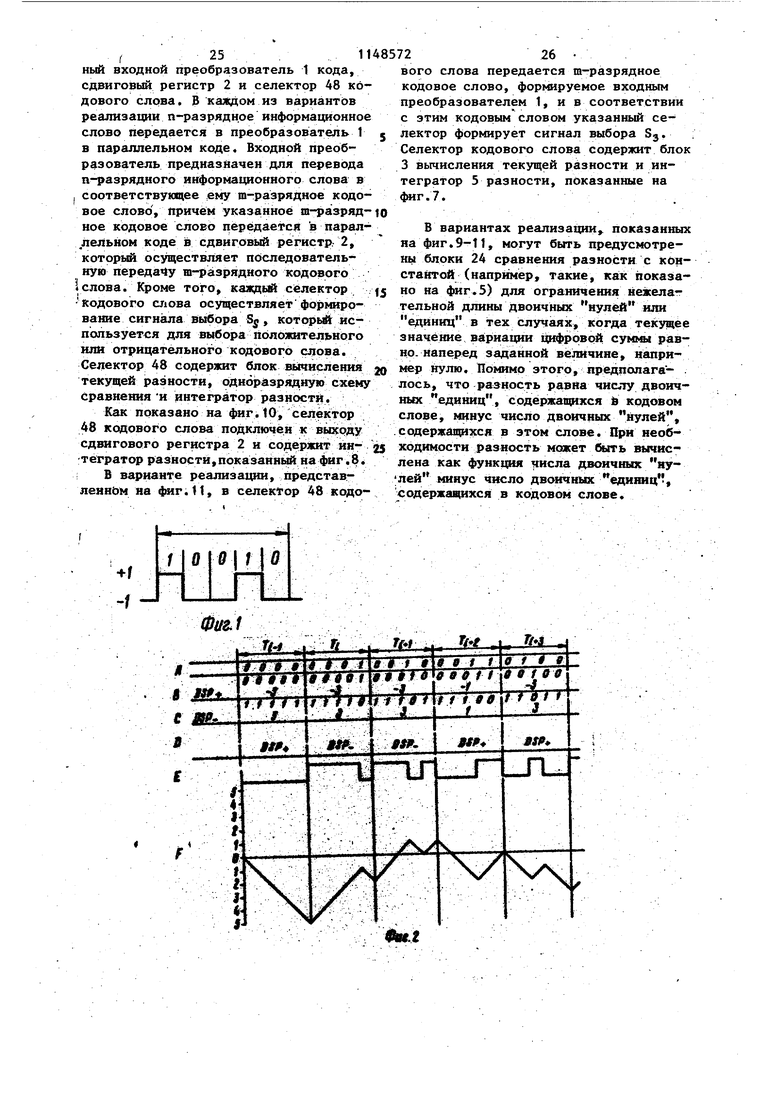

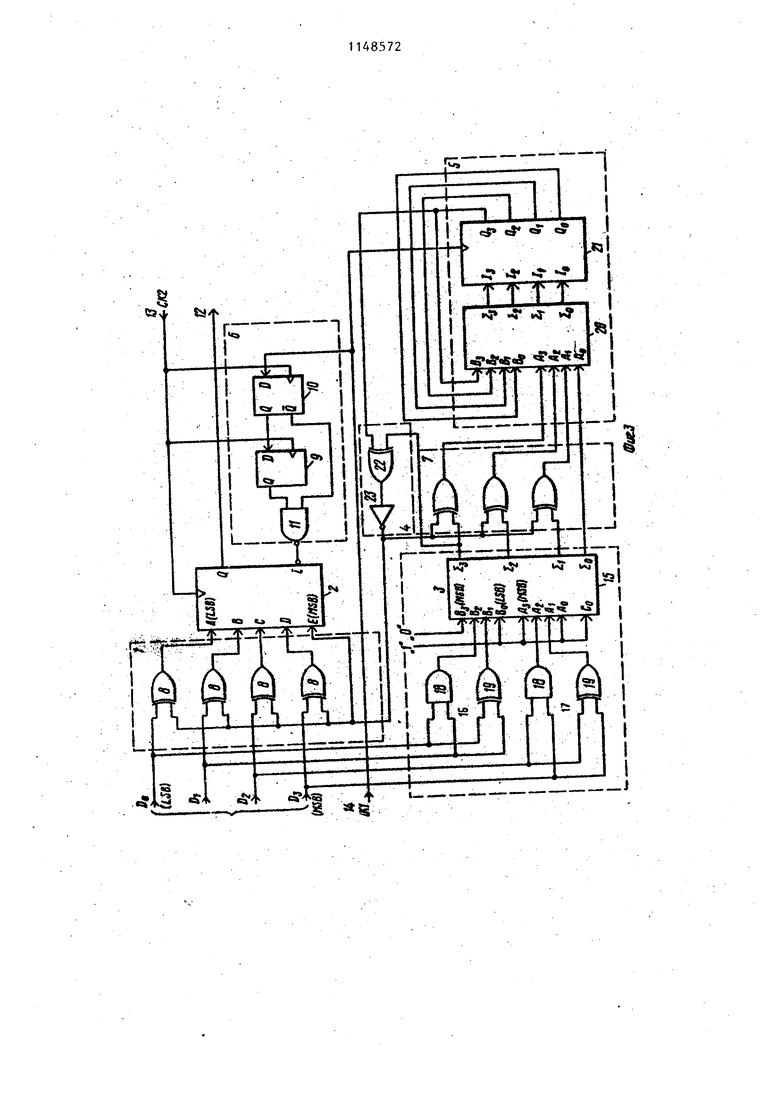

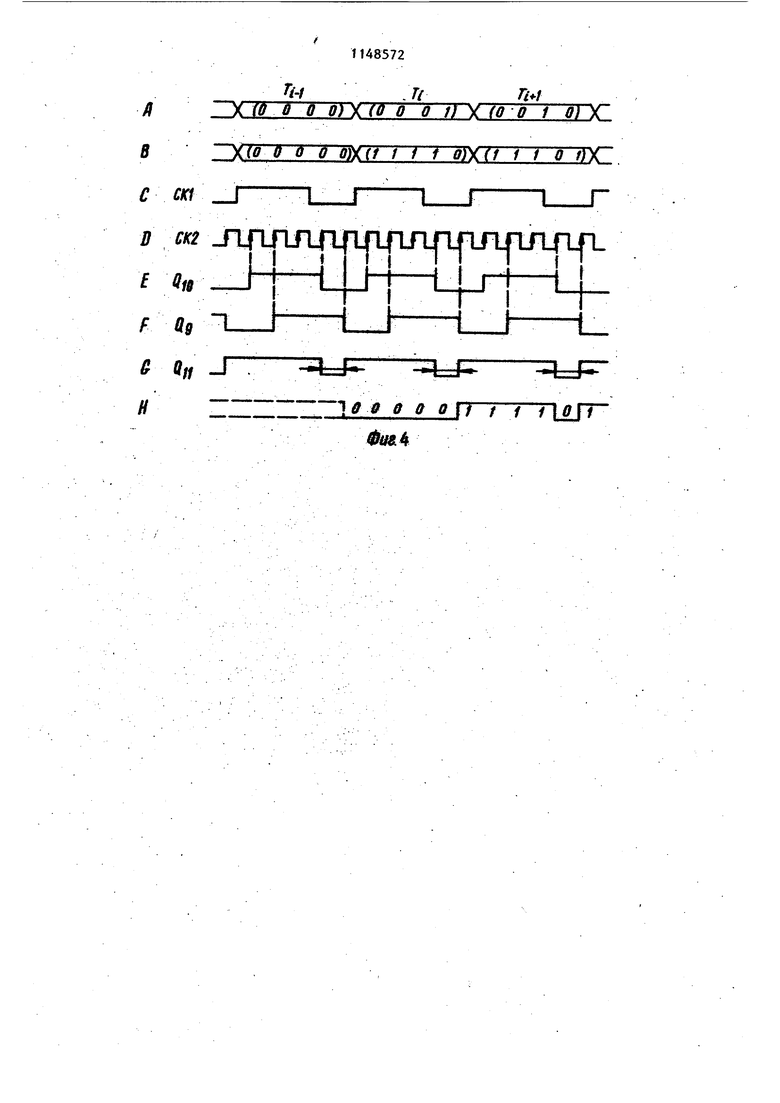

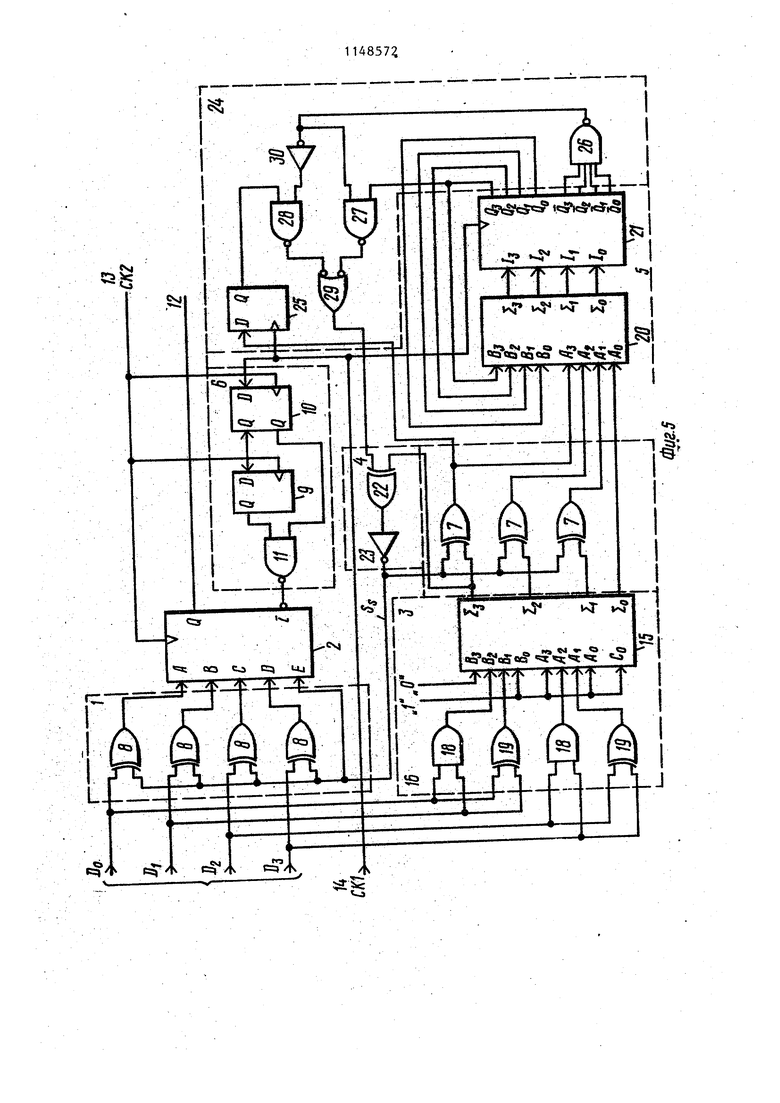

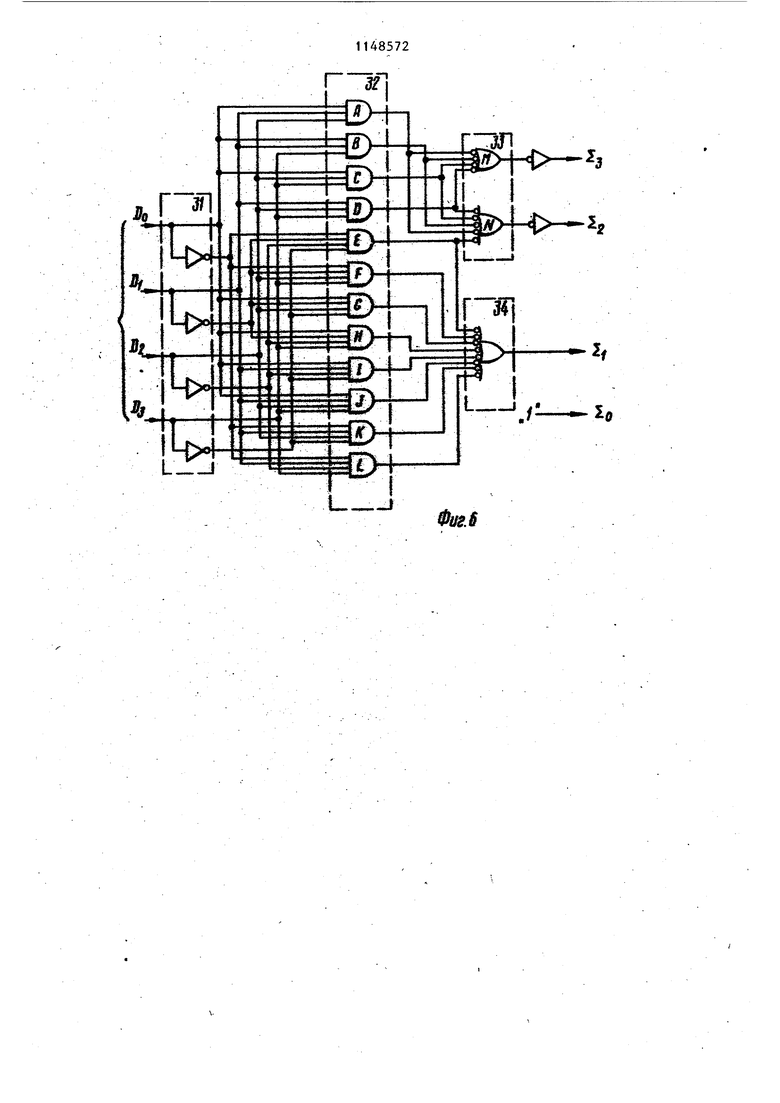

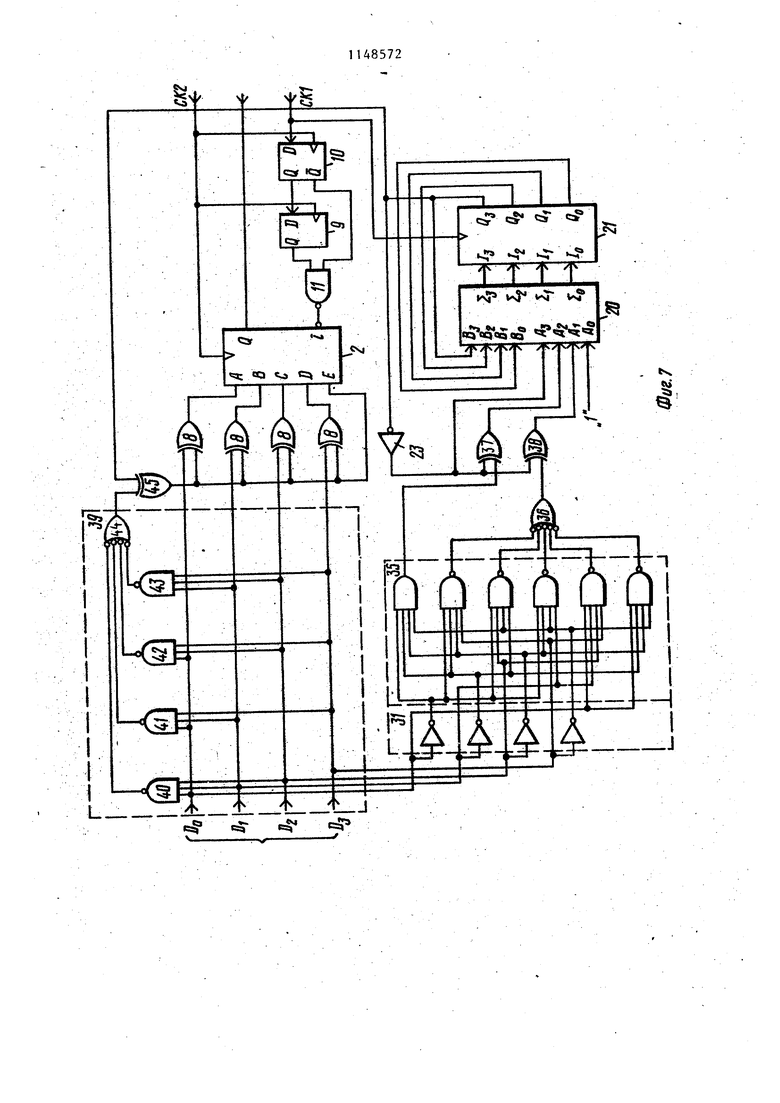

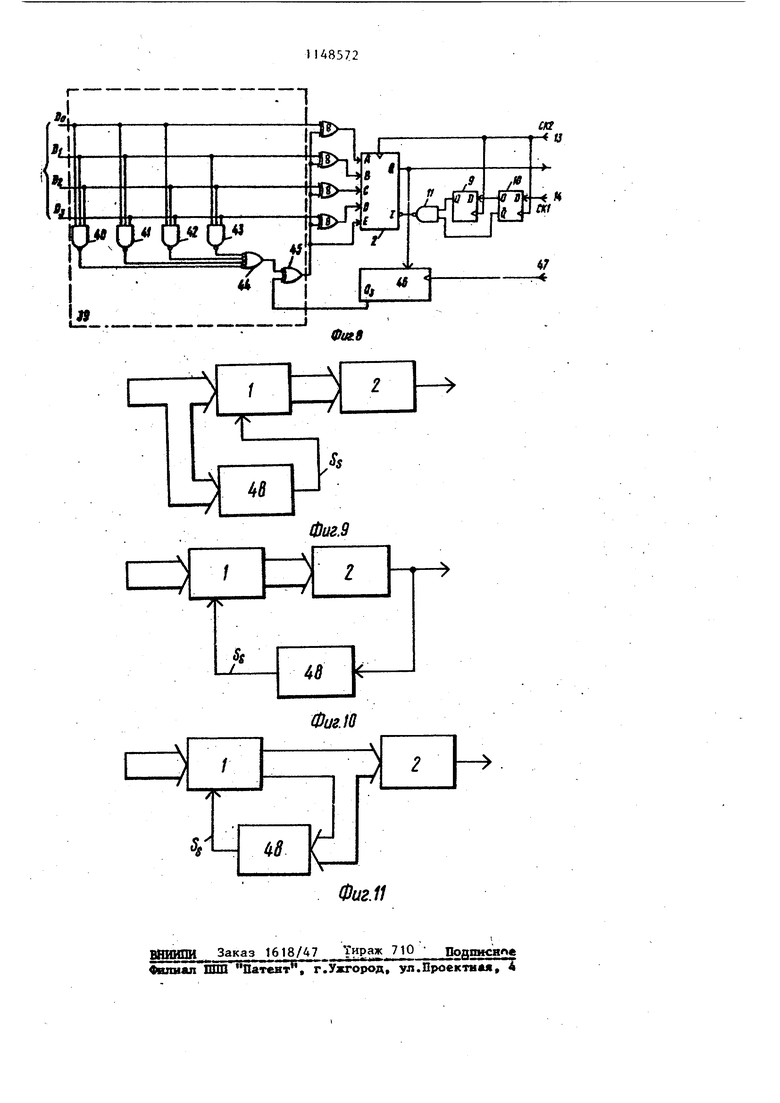

На фиг.1 графически представлена пятиразрядная последовательность цифровых сигналовi на фиг.2 - кодограммы последовательностей слов и эпюры напряжений на фиг.З - блок- схемы первого варианта реализации устройства для преобразования двоичного кода в код магнитного носителя на фиг.4 - временюле диаграювл работы сдвигового регистра и блока управления cдвигoмi на фиг,5 - блоксхемы второго варианта реализации предлагаемого устройства , на фит .6 логическая схема блока вычисления текущей разности; на фиг.7 - блоксхема второго варианта реализации предлагаемого устройства; на фиг.8 то же, третьего варианта реализации, на фиг.9-11 - скелетные схемы раз- . личных вариантов реализации предлагаемого устройства.

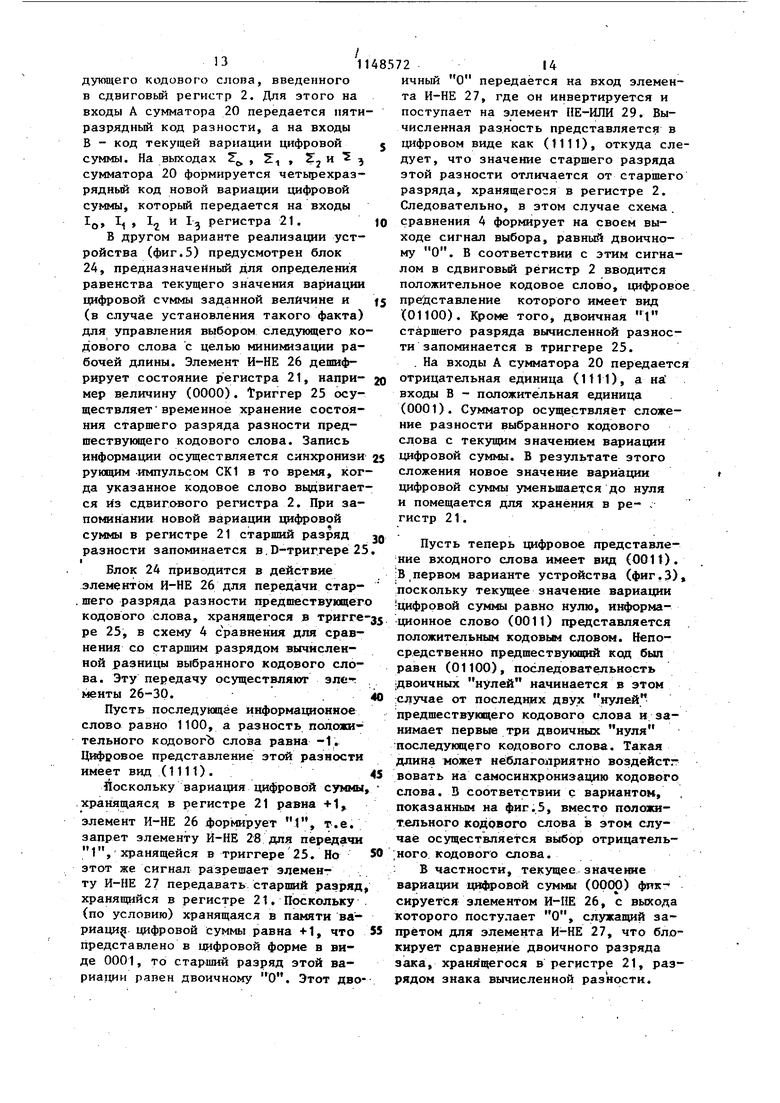

Нпок-схема одного из вариантов предлагаемого устройства для примера преобразования четырехразрядного . входного кода в пятиразрядный выходной код (, ) приведена на фиг.З.

Устройство содержит входной преобразователь 1, сдвиговый регистр 2, блок 3 вычисления текущей разности, одноразрядную схему 4 сравнения, интегратор 5 разности, блок 6 управления сдвигом и группу 7 элементов ИСКЛЮЧАМЦЕЕ ИЛИ.

Входной преобразователь 1 содержит группу 8 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а блок управления сдвигом 6 - триггеры 9-10 и элеме нт И-НЕ 11, выход сдвигового регистра является выходом 12 устройства, причем информация Бодается старшими разрядами вперед. На блок 6 управления сдви- гott поступают о первого 13 и второго 14 тактовых входов устройства iсинхроимпульсы, фьрма которых отра, жена на фиг.4 (С,i)). Блок 3 вычисления текущей разности содержит вьяитатель 15 и первый 16 и второй 17 узлы вычисления числа единиц в ках-. дый из Которых входит элемент И 18 и элемент ИСКЛЮИАЩЕЕ ИЛИ 19. Интегратор 5 разности состоит . из сумматора 20 и-регистра 21. Одноразрядная схема 4 сравнения содержит элемент ЙСКЛЮЧАВДЕЕ ИЛИ 22 и эяе- . мент НЕ 23.

Другой BajJHaHT рвализа1Ц1И изобретения представлен на фиг.5. Здесь помимо блоков, указанных.на фиг.3. имеется блок 24 сравнения разности с константой, содержащий Р-трнггер 25, элементы И-НЕ 26-28,элемент НЕ-НШ 29 и элемент НЕ 30. D-триргер 25 предназначен для хранения значения стар шего разряда разности предиествукяцего входного слова. Выход элемента НЕ-ИЯИ 29 подключен к входу одноразрядной схемы 4 сравнения для сопоставления со старшим разрядом разности предварительно выбранного кодового слова..

j Другой вариант реализации блока вычисления текущей разности, который может быть использован В любой из двух описанных структурных схем предлагаемого устройства, представлен на фиг.6. Этот ,блок содержит группу входных элементов НЕ 31, деши фатор 32 комбинаций с разностью, отличной от +1, первую 33 и вторую 34 группы э лементов НЕ-ИЛИ и группу элементов НЕ. Данный вариант представляет собой двухъярусную И-ШШ комбинацирнную схему, но в соответствии с методами синтеза комбииационньос схем.

он может быть реализован и на многоярусной комбинационной схеме.

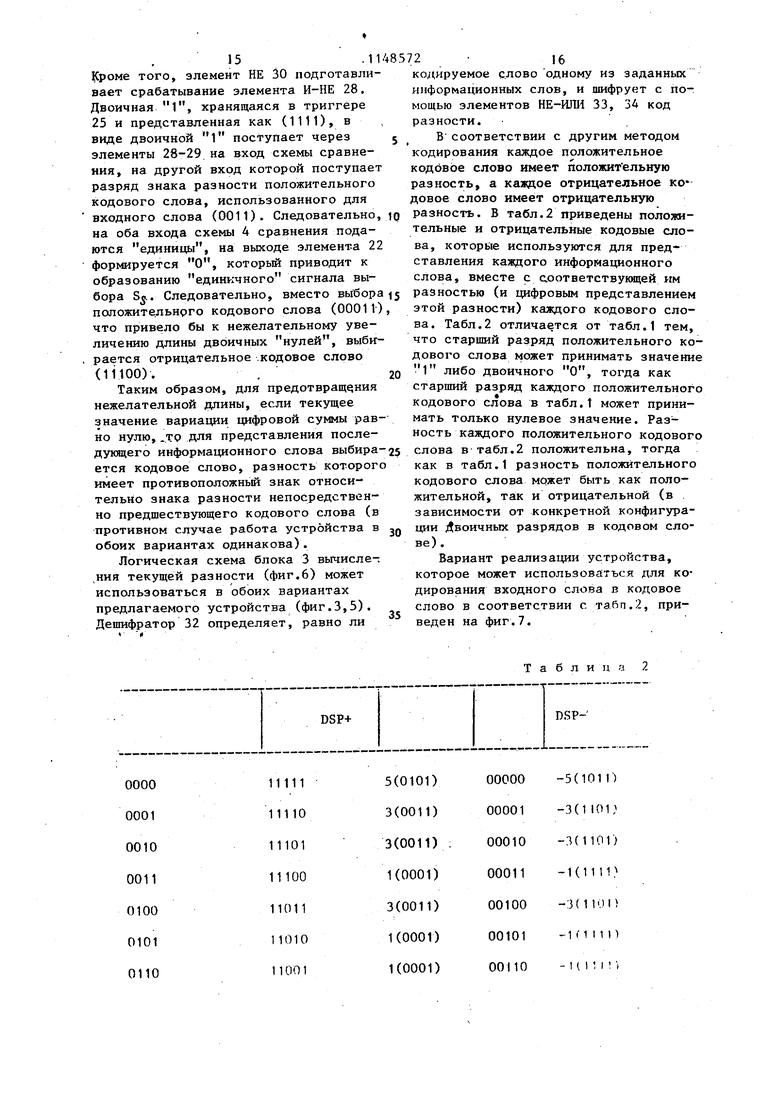

Вариант воплощения предлагаемого устройства, реализующего переходную таблицу 2, представлен на фиг.7.Блок вычисления текущей разности содержит дешифратор 35 комбинаций с разностью 2 и элемент НЕ-ИЛИ 36, первый 37 и второй 38 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ.Поррговьй блок 39 содержит элементы И-НЕ 40-43, элемент НЕ-ИЛИ 44 и элемент ИСКЛЮЧАЮЩЕЕ ШШ 45. Предлагаемое устройство может быть построено (фиг.,8) с использованием реверсивного счетчика 46 в качестве интегратора разности. В этом случае трребуется третий тактовый вход 47 устройства, соединенный со счетным входом реверсивного счетчика 46.

На фиг.9-11 представлены структурные схеьва различных вариантов воплощения предлагаемого устройства, каяодый из которых включает n/m-разрядный входной преобразователь 1, сдвиговЕл регистр 2 и селектор 48 ко дового слова, В каждом из вариантов п-разрядное информационное слово передается в преобразователь 1 в параллельном виде. Преобразователь преднаначен для перевода каждого п-разряд,ного слова в соответствующее ему га-разрядное кодовое слово, причем оно в параллельной форме передается в сдвиговый регистр 2, осуществляющий последовательную выдачу т-разрядного слова. Селектор 48 осуществляет формирование сигнала Sg, который используетсй для положительного или отрицательного кодового слова, состоящего из m разрядов, и содержит блок 3 вычисления текущей разности , одноразрядную схему сравнения 4 и интегратор разности 5.

Предлагаемое устройство работает следующим образом.

На фиг.1 показан пример пятиразрядного кодового слова, для которого . Если двоичная 1 представляетс положительным, а - отрицательным уровнем постоянного напряжения, то при передаче последовательности слов будет возникать постоянная составляющая напряжения , зависящая от разности числа переданных единиц и нулей.

Будем называть разностью DSP величину

DSP-n -no(1)

-число единиц , содержащихся в цифровом слове,

-число нулей, образукмцих то Же самое цифровое слово.

т-разрядного кодового слова

. Следовательно, разность m. Выражение вариация цифровой суммы относится к величине постоянной составляющей, получаемой посредством интегрирования последовательных двоичных единиц и нулей последовательных цифровых сигналов, например последовательных т-разрядньи кодовых слон. Если цифровые слова передаются в последовательном коде, то величина, вариации цифровой суммы изменяется при поступлении каждого последующего двоичного разряда. Например, вариация цифровой суммы последовательно передаваемого слова (10010) изменяется последовательно от начальной величины (например, от нуля) следукщим образом: +1, О, -1,0 В конце этого слова она примет значение -1. Отскща следует, что раз- ность рассматриваемого слова (10010) равна -1. Таким, образом вычисляют разность для множества т-разрядных кодовых слов, которая представляет постоянну1о составля мцую этих слов. Кодовые слова выбираются таким обра-зом, чтобы величина общей вариации . цифровой суммЕЫ была минимальной.При передаче последовательности информационных или кодовых слов без ограни- чения их выбора возможны случаи,

когда вариация цифровой суммы для последовательности таких цифровых слов будет неограниченно увеличиваться в положительном или отрицательном направлениях. Однако в соответствии с изобретением устанавливается максимальная величина дЛя вариации цифровой суммы, при этом определение т-разрядных кодовых слов производится таким образом, чтобы общая величина вариации цифровой суммы уменьшалась.

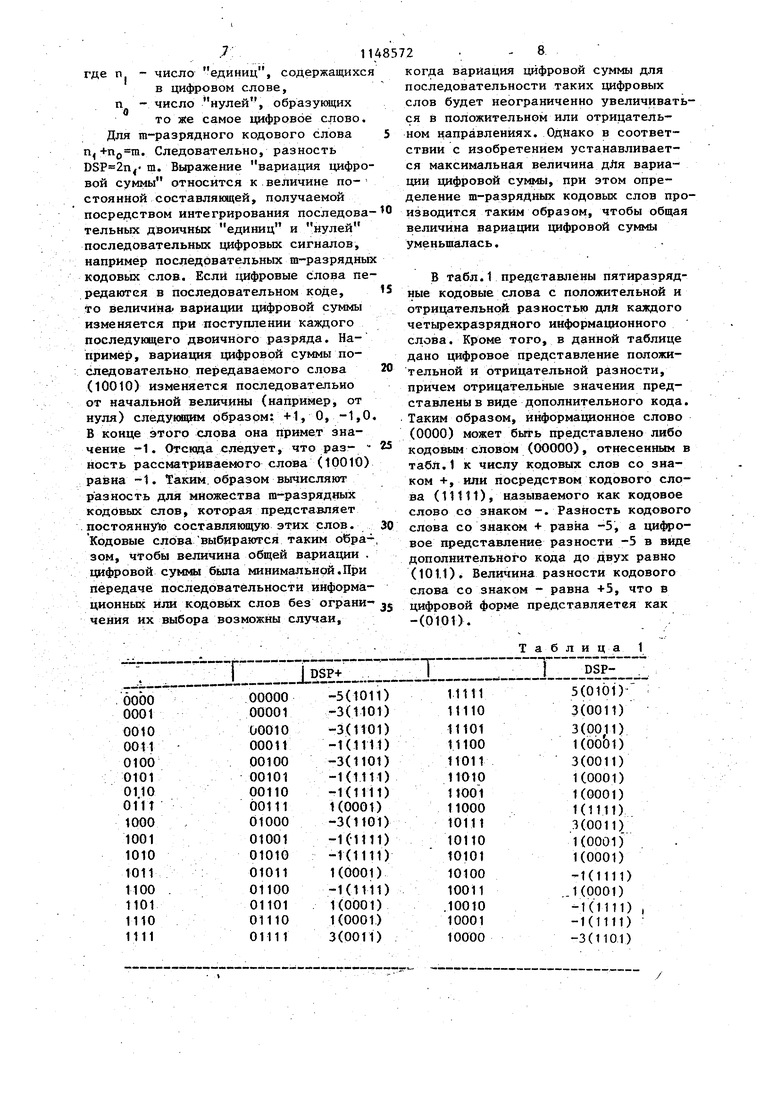

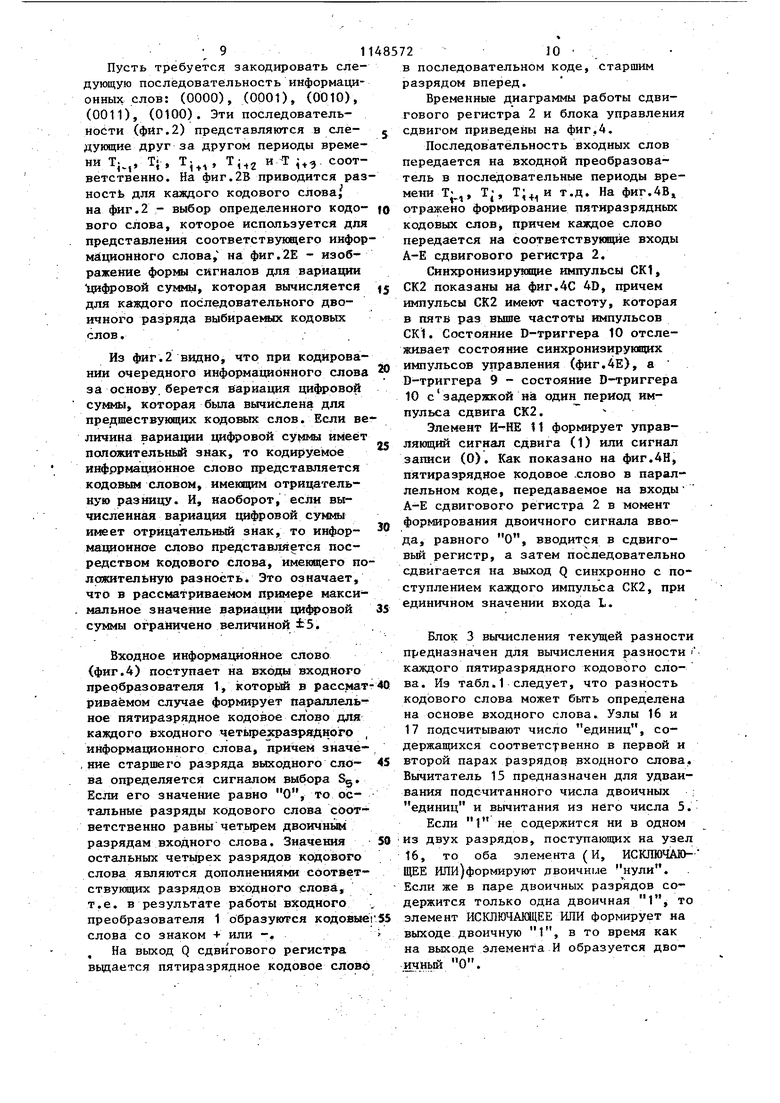

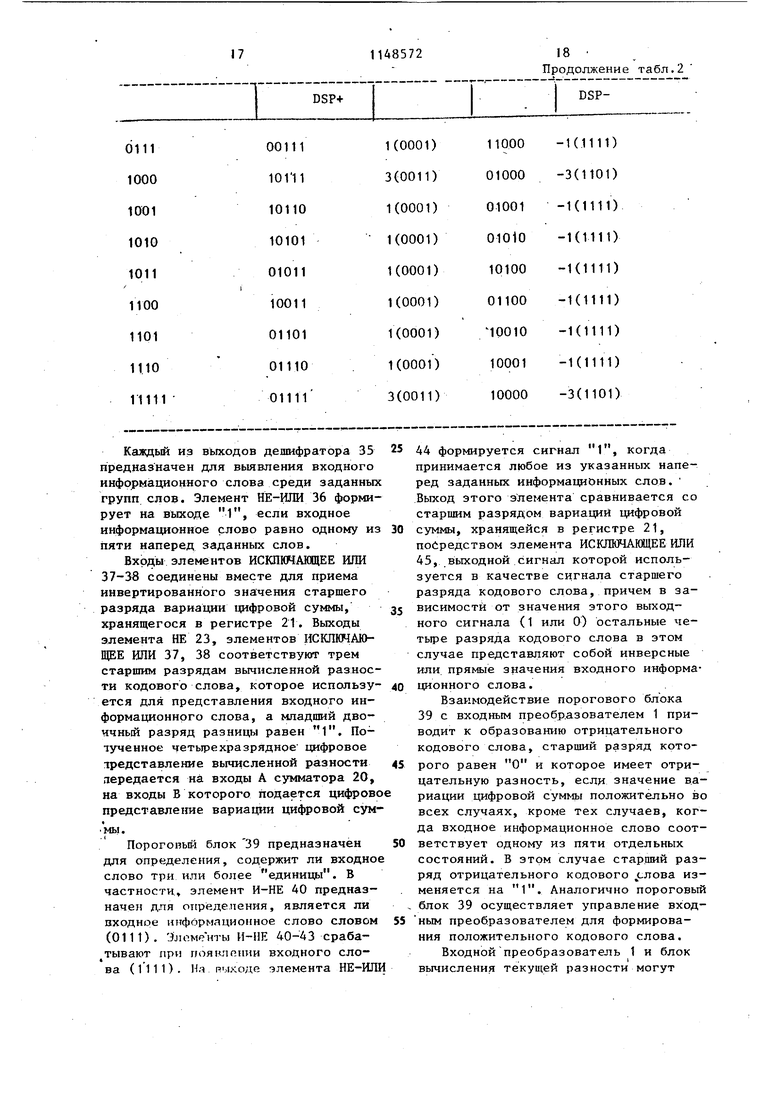

В табл.1 представлены пятиразрядные кодовые слова с положительной и отрицательной разностью длй каждого четырехразрядного информационного слова. Кроме того, в данной таблице дано цифровое представление положительной и отрицательной разности, причем отрицательные значения представлены в виде дополнительного кода. Таким образом, информационное слово (0000) может быть представлено либо кодовым словом (00000), отнесенным в табл.1 к числу кодовых слов со знаком +, или посредством кодового слова (11111), называемого как кодовое слово со знаком -.Разность кодового слова со знаком + равна -5, а ци овое представление разности -5 в виде дополнительного кода до двух равно (101.1). Величина разности кодового слова со знаком - равна +5, что в цифровой форме преДставляетея как -(0101).

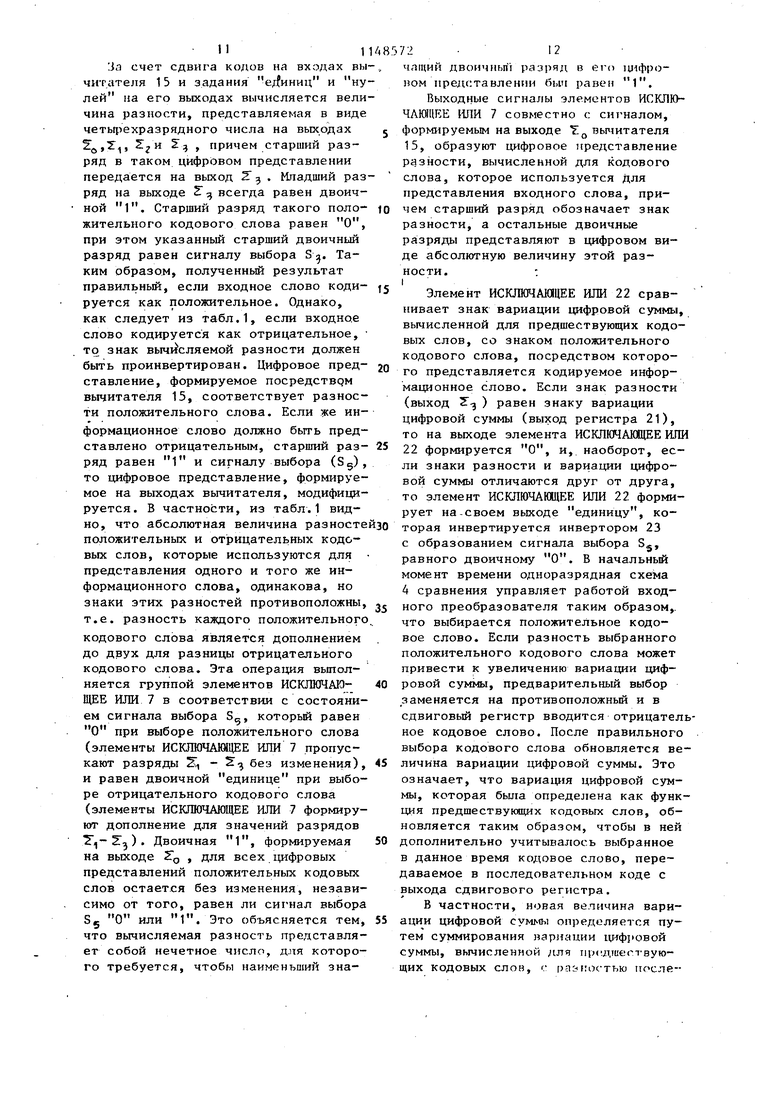

Пусть требуется закодировать следующую последовательность информационных слов: (0000), (0001), (0010), (0011), (0100). Эти последовательности (фиг.2) представляются в еледующие друг за другом периоды времени Tj,, Т-, Tj, , Ti,2 и-Т соответственно. На фиг.2В приводится разностЬ для каждого кодового слава на фиг.2 - выбор определенного кодового слова, которое используется для представления соответствующего информйционного слова, на фиг.2Е - изображение формы сигналов для вариации цифровой суммы, которая вычисляется для каждого последовательного двоичного разряда выбиpae яыx кодовьгх слов.

Из фиг.2 видно, что при кодировании очередного информационного слова за основу, берется вариация цифровой суммы, которая была вычислена для предшествующих кодовых слов. Если величина вариации цифровой сумьвл имеет положительный знак, то кодируемое информационное слово представляется кодовым словом, имеющим отрицательную разницу. И, наоборот, если вычисленная вариация цифровой имеет отрицатепьш 1й знак, то информационнае слово представляется посредством кодового слова, имеющего полрясительную разность Это означает, что в рассматриваемом примере максимальное значение вариации цифровой суммы ограничено величиной i5.

Входное информационное слово (фиг.4) поступает на входы входно го преобразователя 1, который в рассмат риваёмом случае формирует параллельное пятиразрядное кодовое слово для каждого входного четырехразрядного информационного слова, причем значе, ние старшего разряда выходного елова определяется сигналом выбора Sg. Если его значение равно О, то остальные разряды кодового слова соответственно равны четырем двоичньЫ разрядам входного слова. Значения остальных четырех разрядов кодового слова являются дополнениями соответствующих разрядов входного слова, т.е. в результате работы входного преобразователя 1 образуются кодогые слова со знаком + или -,

На выход Q сдвигового регистра вьщается пятиразрядное кодовое слово

в последовательном коде, старшим разрядом вперед.

Временные диаграммы работы сдвигового регистра 2 и блока управления сдвигом приведены на фиг.4.

Последовательность входных слов передается на входной преобразователь в последовательные периоды времени Т-, , Tj-, т.д. На фиг.4В, отражено формирование пятиразрядных кодовых слов причем каждое слово передается на соответствующие входы А-Е сдвигового регистра 2.

Синхронизируюоще импульсы СК1, СК2 показаны на фиг.4С 4D, причем импульсы СК2 имеют частоту, которая в пять раз выше частоты импульсов СК1. Состояние D-триггера 10 отслеживает состояние синхронизирующих импульсов управления (фиг.4Е), а В-триггера 9 - состояние D-триггера 10 сзадержкой His один период импульса сдвига СК2.

Элемент 1 формирует управляющий сигнал сдвига (1) или сигнал записи (0). Как показано на фиг.АН, пятиразрядное кодовое .слово в параллельном коде, передаваемое на входы А-Е сдвигового регистра 2 в момент формирования двоичного сигнала ввода, равного О, вводится в сдвиговьй регистр, а затем последовательно сдвигается на выход Q синхронно с поступлением каждого импульса СК2, при единичном значении входа L.

Блок 3 вычисления текущей разност предназначен для вычисления разности каждого пятиразрядного кодового елова. Из табл.1 следует, что разность кодового слова может быть определена на основе входного слова . Узлы 16 и 17 подсчитывают число единиц, содержащихся соответственно в первой и второй парах разрядов входного слова Вычитатель 15 предназначен для удваивания подсчитанного числа двоичных единиц и вычитания из него числа 5 Если 1 не содержится ни в одном ;из двух разрядов, поступающих на узел 16, то оба элемента (И, ИСКЛЮЧАЮЩЕЕ ИЛИ)формируют двоичные нули. Если же в паре двоичных разрядов содержится только одна двоичная 1, т элемент ИСКЛЮЧАЩЕЕ ИЛИ формирует на выходе двоичную 1, в то время как на выходе элемента И образуется двоичный О.

111

:ia счет сдвига кодов на входах вы читателя 15 и задания и нулей на его выходах вычисляется величина разности, представляемая в виде четьфехразрядного числа на выходах 2(j,T,, 2 причем старший разряд в таком цифровом представлении передается на выход Z . Младший разряд на выходе всегда равен двоичной 1. Старший разряд такого положительного кодового слова равен О, при этом указанный старший двоичный разряд равен сигналу выбора S. Таким образом, полученный результат правильный, если входное слово кодируется как положительное. Однако, как следует из табл.1, если входное слово кодируется как отрицательное, то знак выш сляемой разности должен быть проинвертирован. Цифровое представление, формируемое посредстврм вычитателя 15, соответствует разности положительного слова. Если же информационное слово должно быть представлено отрицательным, старший разряд равен 1 и сигналу выбора (S), то цифровое представление, формируемое на выходах вычитателя, модифицируется. В частности, из табл.1 видно, что абсолютная величина разносте положительных и от рицательных кодовых слов, которые используются для представления одного и того же информационного слова, одинакова, но знаки этих разностей противоположны, т.е. разность каждого положительного

кодового слова является дополнением до двух для разницы отрицательного кодового слова. Эта операция выполняется группой элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7 в соответствии с состоянием сигнала выбора S, который равен О при выборе положительного слова (элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 7 пропускают разряды Zi - 3 без изменения), и равен двоичной единице при выборе отрицательного кодового слова (элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 7 формируют дополнение для значений разрядов ). Двоичная 1, формируемая на выходе , для всех цифровых представлений положительных кодовых слов остается без изменения, независимо от того, равен ли сигнал выбора SK О или 1. Это объясняется тем, что вычисляемая разность представляет собой нечетное число, для которого требуется, чтобы наименьший зна72 12

чпгдий двончмьп разряд в еш 1и1фро1юм представлении быч равен 1.

Выходные сигналы элементов ИСКЛЮЧАКЯЦ1 1Е ИЛИ 7 совместно с сигналом, формируемым на выходе Т вычитателя 15, образуют цифровое представление разности, вычисленной для кодового слова, которое используется для представления входного слова, причем старший разряд обозначает знак разности, а остальные двоичные разряды представляют в цифровом виде абсолютную величину этой разности. : I

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 22 сравнивает знак вариации цифровой суммы вычисленной для предшествующих кодовых слов, со знаком положительного кодового слова, посредством которого представляется кодируемое информационное слово. Если знак разности (выход ) равен знаку вариации цифровой суммы (выход регистра 21), то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛ 22 формируется О, и, наоборот, если знаки разности и вариации цифровой суммы отличаются друг от друга, то элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 22 формирует на-своем выходе единицу, которая инвертируется инвертором 23 с образованием сигнала выбора Sj, равного двоичному О. В начальный момент времени одноразрядная схема 4 сравнения управляет работой входного преобразователя таким образом,, что выбирается положительное кодовое слово. Если разность выбранного положительного кодового слова может привести к увеличению вариации цифровой суммы, предварительный выбор заменяется на противоположный и в сдвиговый регистр вводится отрицателное кодовое слово. После правильного выбора кодового слова обновляется величина вариации цифровой суммы. Это означает, что вариахщя цифровой суммы, которая бь01а определена как функция предшествующих кодовых слов, обновляется таким образом, чтобы в ней дополнительно учитывалось выбранное в данное время кодовое слово, передаваемое в последовательном коде с выхода сдвигового регистра.

В частности, новая величина вариации цифровой суммы определяется путем суммирования вариации 1и-тфровой суммы, вычисленной для щя-.дткегтвующих кодовых слов, с разностью ттосле131дующего кодового слова, введенного в сдвиговый регистр 2. Для этого на входы А сумматора 20 передается пяти разрядный код разности, а на входы В - код текущей вариации цифровой суммы. На выходах Z , Z, , Sj и 3 сумматора 20 формируется четырехраз- рядньй код новой вариации цифровой суммы, которьй передается на входы IQ, I, , 1 и I, регистра 21. В другом варианте реализации устройства (фиг.5) предусмотрен блок 24, предназначенный для определения равенства текущего значения вариации цифровой СУММЫ заданной величине и (в случае установления такого факта) для управления выбором следунмцего ко дового слова с целью минимизации рабочей длины. Элемент И-НЕ 26 дешифрирует состояние регистра 21, например величину (0000). Триггер 25 осуществляет временное хранение состояния старшего разряда разности предшествующего кодового слова. Запись информации осуществляется синхронией руищим импульсом СК1 в то время, ког да указанное кодовое слово ввдвигает ся из сдвигового регистра 2. При запоминании новой вариации цифровой суммы в регистре 21 старший разряд разности запоминается в. D-триг.гере 25 Блок 24 приводится в действие элементом И-НЕ 26 для передачи стар. шего разряда разности предшествуищег кодового слова, хранящегося в тригге ре 25, в схему 4 сравнения для сравнения со старшим разрядом вычисленной разницы выбранного кодового слова. Эту передачу осуществляют злет менты 26-30.. Пусть последующее информационное слово равно 1100, а разность падожительного кодовогЪ слова равна -1. Цифровое представление этой разности имеет вид (1111). Поскольку вариация цифровой суммы хранящаяся в регистре 21 равна +1 элемент И-НЕ 26 формирует 1, т.е. запрет элементу Й-НЕ 28 для передачи 1, хранящейся в триггере 25. Но этот же сигнал разрешает злеменг ту И-НЕ 27 передавать старший разряд хранящийся в регистре 21. Поскольку (по условию) хранящаяся в памяти вариаци цифровой суммы равна +1, что представлено в цифровой форме в виде 0001, то старший разряд этой вариадаи равен двоичному О. Этот дво 72 ичный О передаётся на вход элемента И-НЕ 27, где он инвертируется и поступает на элемент ПЕ-ИЛИ 29. Вычисленная разность представляется в цифровом виде как (1111), откуда следует, что значение старшего разряда этой разности отличается от старшего разряда, хранящегося в регистре 2. Следовательно, в этом случае схема сравнения 4 формирует на своем выходе сигнал выбора, равный двоичному О. В соответствии с этим сигналом в сдвиговый регистр 2 вводится положительное кодовое слово, цифровое предоставление которого имеет вид 1 01100). Кроме того, двоичная 1 старшего разряда вычисленной разности запоминается в триггере 25. .На входы А сумматора 20 передается отрицательная единица (И 11), а на входы В - положительная единица (0001). Сумматор осуществляет сложение разности выбранного кодового слова с текущим значением вариации цифровой суммы. В результате этого сложения новое значение вариации цифровой cjTMMM уменьшается до нуля и помещается для хранения в ре- гистр 21. Пусть теперь цифровое представление входного слова имеет вид (001t). ;В,первом варианте устройства (фиг.З) поскольку текущее значение вариации цифровой суммы равно нулю, информа.ционное слово (0011) представляется положительным кодовым словсш. Непосредственно предшествующий код был равен (01100), последовательность двоичных нулей начинается в этом :случае от последвдх двух нулей предшествующего кодового слова и занимает первые три двоичных нуля последующего кодового слова. Такая длина может неблаголриятно воздейстг вовать на самосинхронизацию кодового слова. В соответствии с вариантой, показанным на фиг.5, вместо положительного кодового в этом случае осуществляется выбор отрицательного кодового слова. : В частности, текущее значение вариации цифровой суммы (ООСЮ) фиксируется элементом И-ПЕ 26, с выхода которого поступает О, служащий запретом для элемента И-НЕ 27, что бл.окирует сравне.ние двоичного разряда зака, хранящегося в регистре 21, разрядом знака вычисленной разности. Кроме того, элемент НЕ 30 подготавливает срабатывание элемента И-НЕ 28. Двоичная 1, хранящаяся в триггере 25 и представленная как (1111), в виде двоичной 1 поступает через элементы 28-29 на вход схемы сравнения, на другой вход которой поступает разряд знака разности положительного кодового слова, использованного для входного слова (0011). Следовательно, на оба входа схемы 4 сравнения подаются единицы, на выходе элемента 22 формируется О, который приводит к образованию единичного сигнала выбора S.. Следовательно, вместо выбора положительного кодового слова (00011) что привело бы к нежелательному увеличению длины двоичных нулей, выбирается отрицательное .кодовое слово (11100). Таким образом, для предотвращения нежелательной длины, если текущее значение вариации цифровой суммы равно нулю,.то для представления последукядего информационного слова выбирается кодовое слово, разность которого имеет противоположньй знак относительно знака разности непосредственно предшествующего кодового слова (в противном случае работа устройства в обоих вариантах одинакова). Логическая схема блока 3 вычисле-. ,ния текущей разности (фиг.6) может использоваться в обоих вариантах предлагаемого устройства (фиг.3,5). Дешифратор 32 определяет, равно ли .1 72 кодируемое слово одному из заданных информационных слов, и шифрует с помощью элементов НЕ-ИЛИ 33, 34 код разности. Всоответствии с другим методом кодирования каждое положительное кодовое слово имеет положительную разность, а каждое отрицательное кодовое слово имеет отрицательную разность. В табл.2 приведены положительные и отрицательные кодовые слова, которые используются для представления каяздого информационного слова, вместе с с.оответствукщей им разностью (и цифровым представлением этой разности) каждого кодового слова. Табл.2 отличается от табл.1 тем, что старший разряд положительного кодового слова может принимать значение 1 либо двоичного О, тогда как старший разряд каждого положительного кодового слова в табл. может принимать только нулевое значение. Разность каждого положительного кодового слова в табл.2 положительна, тогда как в табл.1 разность положительного кодового слова может быть как положительной, так и отрицательной (в зависимости от конкретной конфигурации Двоичных разрядов в кодовом слове). Вариант реализации устройства, которое может использоваться для кодирования входного слова в кодовое слово в соответствии с табп.2, приведен на фиг.7.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБЫ И УСТРОЙСТВА МОДУЛИРОВАНИЯ И ДЕМОДУЛИРОВАНИЯ СИГНАЛОВ | 1995 |

|

RU2171505C2 |

| Преобразователь кодов | 1988 |

|

SU1547071A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Способ диагностики недвоичных блоковых кодов | 2018 |

|

RU2693190C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Преобразователь кода | 1987 |

|

SU1557685A1 |

| Преобразователь последовательного знакоразрядного кода в дополнительный двоичный код | 1983 |

|

SU1113796A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

1. УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДВОИЧНОГО КОДА В КОД МАГНИТНОГО НОСИТЕЛЯ, содержащее входной преобразователь и сдвиговьй регистр, ин41Ормационные входы которого соединены с выходами входного преобразователя, информационные входы которого соединены с информационными входами устройства, первый тактовый вход которого соединен с тактовым входом сдвигового регистра, выход которого является выходом устройства, о т л ичающееся тем, что, с целью расширения класса решаегшх задач за счет обеспеч ения минимизации постоянной составляющей хранимых кодовых последовательностей, в него введены блок вычисления текущей разности, интегратор разности, состоящий из сумматора и регистра, группа элементов ИСКЛЮЧАНЦЕЕ ИЛИ, одноразрядная схема сравнения и блок управления сдвигом, содержащий два D -триггера и элемент И-НЕ, первьй и второй входы которого соединены соответственно с инверсным входом первого и прямым выходом второгоD-триггеров, синхровходы которых соединены с первым тактовым входом устройства, второй тактовый вход котррого соединен с тактовым входом регистра и с 0-входом первого)-триггера, прямой выход которого соединен сD-входом второго 1)-триггера, выход элемента И-НЕ соединен с управляющим входом сдвигового регистра, дополнительный информационный вход которого соединен с выходом одноразрядной схемы сравнения, с управляюпщм входом входного преобразователя и с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, вторые входы которых соединены соответственно с выходами старших разрядов блока вычисСО ления текущей разности, информационные входы которого соединены соответственно с информационными входами устройства, а выходы младшего и старшего разрядов блока вычисления текущей разности соединены соответственно с входами младшего разряда первой группы в:содов сумматора и г с первым входом одноразрядной схемы 00 сравнения, второй вход KOTOpofif соеел | динен с выходом старшего разряда регистра, входы которого соединены с Nd выходами сум1 штора, входы старших разрядов первой группы которого соединены с выходами элементов ИСКЛЮЧАЮ,ЩЕЕ ИЛИ группы, входы нуля и единицы блока вычисления текущей разности являются выходами нуля и единицы устройства, выходы регистра соединены с входами второй группы сумматора. 2. Устройство по П.1, о т л и чающееся тем, что в нем входной преобразователь вьтолнен в виде

11111

11110 11101 11100 11011 11010 1 1001

Таблица 2 Каждый из выходов дешифратора 35 предназначен для выявления входного информационного слова среди заданных групп слов. Элемент НЁ-ИЛИ 36 формирует на выходе 1, если входное информационное слово равно одному из пяти наперед заданных слов. Входы элементов ИСКПКНАИЦЕЕ ИЛИ 37-38 соединены вместе для приема инвертированного значения старшего разряда вариации цифровой суммы, хранящегося в регистре 21. Выходы элемента НЕ 23, элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 37, 38 соответствуют трем старшим разрядам вычисленной разности кодового слова, которое используется для представления входного информационного слова, а младший двоччньй разряд разницы равен 1. По1ученное четырехразрядное цифровое 1редставление вычисленной разности передается на входы А сумматора 20, на входы В которого подается цифрово представление вариации цифровой сумГТороговьш блок 39 предназначен для определения, содержит ли входно слово три или более единицы. В частности., элемент И-НЕ 40 предназначен для определения, является ли входное информационное слово словом (0111). Элементы И-НЕ 40-43 сраба тывают при ПОЯШ1ПИНИ входного слова (1111). Ил выходе элемента НЕ-ИЛ 44 формируется сигнал 1, когда принимается любое из указанных наперед заданных информационных слов. Выход этого элемента сравнивается со старшим разрядом вариации щфровой суммя, хранящейся в регистре 21, посредством элемента ИСКЛЮЧАЩЕЕ ИЛИ 45, выходной сигнал которой используется в качестве сигнала старшего разряда кодового слова, причем в зависимостй от значения этого выходного сигнала (1 или 0) остальные четыре разряда кодового слова в этом случае представляют собой инверсные или. прямые значения входного информационного слова. Взаимодействие порогового блока 39 с входным преобразователем 1 приводит к образованию отрицательного кодового слова, старший разряд крторого равен О и которое имеет отрицательную разность, если значение вариации цифровой суммь положительно во всех случаях, кроме тех случаев, когда входное информационное слово соответствует одному из пяти отдельных состояний. В этом случае стар.пий разряд отрицательного кодового лова изменяется на 1. Аналогично пороговый блок 39 осуществляет управление входным преобразователем для формирования положительного кодового слова. Входнойпреобразователь 1 и блок вычисления текущей разности могут быть реализованы на постоянном запоминающем устройстве, которое может также использоваться для осуществления функций порогового блока 39. Постоянное запоминающее устройство може-т содержать, например, тридцать две адресуемые ячейки памяти восьмиразрядных слов, причем двоичные разряды Djj-D изображают пятиразрядное кодовое слово, а остальные три разряда , отведены для трех старших разрядов цифрового представления разности. Для адресации каждой ячейки может использоваться пятиразрядное .слово, поступающее на адресны входы. Старрий разряд адресного слов может представлять знак вариации циф ровой суммы. Остальные четьфе разряда адресного слова отведены для изоб ражения четырехразрядного информаци- онного слова. Если реализуется табл.2, то всяки раз,- когда разряд знака вариациициф ровой суммы равен О, производится адресование тех ячеек, в которых хра нятся отрицательные кодовые слова, при этом конкретный адрес ячейки запоминающего устройства задается сами информационным словом. Таким образом определенное кодовое слово, считывае мое из ПЗУ, является точным представ лением принятого на входе информационного слова, при этом оно выбирается как функция знака текущего значения вариации цифровой суммы. Помимо этого, в этой самой ячейке памяти Хранятся три из четырех разрядов, представлякнцих разность указанного кодового слова. Интегратор разности 5 в предлагае мом устройстве может быть вьшолнен на реверсивном счетчике (фиг.8), при

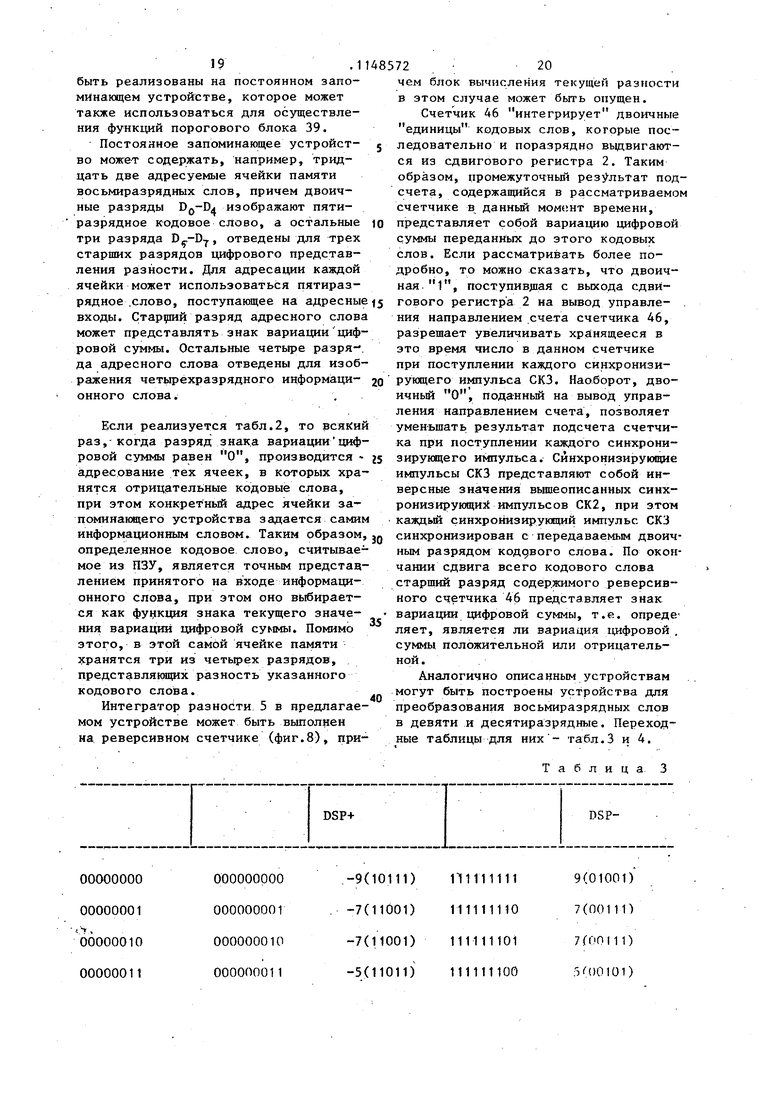

000000000 000000001 000000010 000000011

9(01001)

П1111111 7(00111) 111111110 7(00111) 111111101

5аю101) 111111100 чем блок вычисления текущей разности в этом случае может быть опущен. Счетчик 46 интегрирует двоичные единицы кодовых слов, которые последовательно и поразрядно вьщвигаются из сдвигового регистра 2. Таким образом, промежуточна рез5 льтат подсчета, содержащийся в рассматриваемом счетчике в данный момент времени, представляет собой вариацию цифровой суммы переданных до этого кодовых слов. Если рассматривать более подробно, то можно сказать, что двоичпоступив аая с выхода сдвигового регистра 2 на вывод управле- . ния направлением счета счетчика 46, разрешает увеличивать хранящееся в это время число в данном счетчике при поступлении каждого синхронизирующего импульса СКЗ. Наоборот, двоичньй , поданньй на вывод управления направлением счета, позволяет уменьшать результат подсчета счетчика при поступлении каждого синхронизирующего импульса. Синхронизирующие импульсы СКЗ представляют собой инверсные значения вышеописанных синхронизирующиз4 импульсов СК2, при этом каждьй синхронизирующий импульс СКЗ синхронизирован с передаваемым двоичным разрядом КОД9ВОГО слова. По окончании сдвига всего кодового слова старший разряд содержимого реверсивного счетчика 46 представляет знак вариации цифровой суммы, т.е. определяет, является ли вариация цифровой , суммы положительной или отрицательной . Аналогично описанным устройствам могут быть построены устройства для преобразования восьмиразрядных слов в девяти и десятиразрядные. Переходные таблицы для них- табл.3 и 4. Таблица 3

Прододженне табл.3

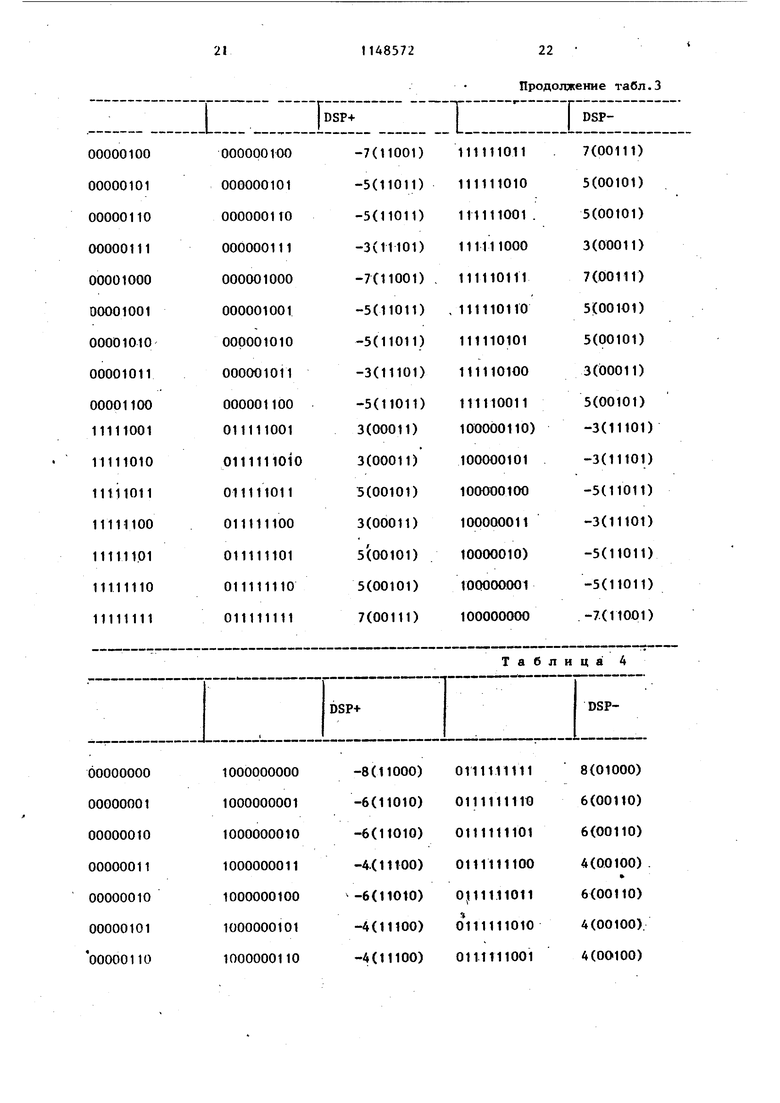

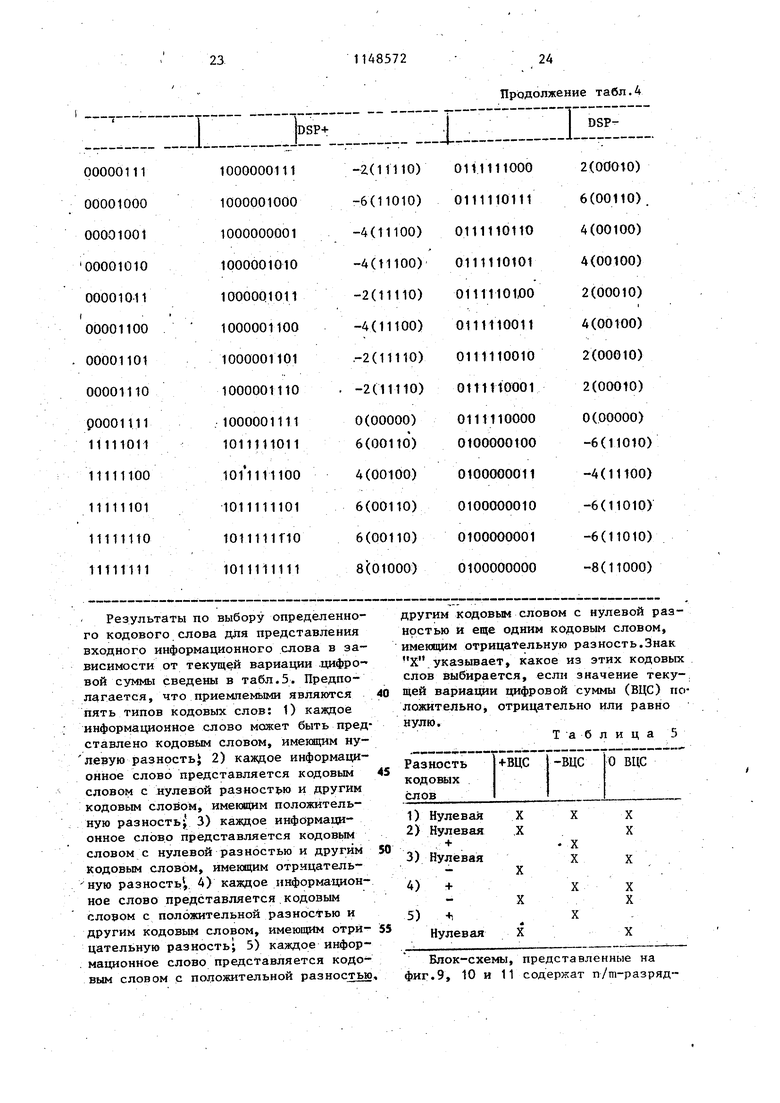

Результаты по выбору определенного кодового слова для представления входного информационного слова в зависимости от текущей вариации .цифровой суммы сведены в табл.5. Предполагается, что приемлемыми являются пять типов кодовых слов: 1) каждое информационное слово может быть представлено кодовым словом, имекяцим нулевую pasHOCTbJ 2) каждое информационное слово представляется кодовым словом с нулевой разностью и другим кодовым словом, имеювщм положительную разность 3) каждое информационное слово представляется кодовым словом с нулевой разностью и другим кодовым словом, имеющим отрицательную разность , 4) каждое информационное слово представляется кодовым словом с положительной разностью и другим кодовым словом, имеющим отрицательную разность; 5) каждое информационное слово представляется кодовым словом с положительной разностью

Продолжение табл.4

другим кодовым словом с нулевой разностью И еще одним кодовым словом, имеющим отрицательную разность.Знак X указывает, какое из этих кодовых слов выбирается, если значение теку-. щей вариахши цифровой суммы (ВЦС) положительно, отрицательно или равно нулю.

Таблица 5

+ВЦС

-ВЦС

о ВЦС

X X

X X

X

X

X

X X

X X

X X

л

X

X

Блок-схемы, представленные на фиг.9, 10 и 11 содержат п/т-разряд1 ный входной преобразователь 1 кода, сдвиго1вый регистр 2 и селектор 48 ко дового слова, В каждом из вариантов реализахщи п-разрядире информационно слово передается в преобразователь 1 в параллельном коде. Входной преобразователь предназначен для перевода п-разрядного информационного слова в I соответствующее ему т-разрядное кодо вое слово , причём указанное ш-разряд ное кодовое слово передается в парал .лельном коде is сдвиговый регистр 2, который осуществляет последовательную передачу т-разрядного кодового 4 слова. Кроме того, каявдый селектор кодового слова осуществляет формирование сигнала выбора S , который используется для выбора положительного ИЛИ отрицательного кодового слова Седактор 48 содержит блок выяислеши текущей разности, однбразрядную схену сравнения -и интегратор разности. Как показано на фиг.10, селектор 48 кодового слова подключен к выходу сдвигового регистра 2 и содержит интегратор разности,показанный на фиг.S. В варианте реализации, представленньм на фиг.11, в селектор 48 кодо72вого слова передается т-разрядное кодовое слово, формируемое входным преобразователем 1, и в соответствии с этим кодовым с лов ом указанный селектор формирует сигнал выбора S. Селектор кодового слова содержит блок 3 вычисления текущей разности и интегратор 5 разности, показанные на фяг.7. В вариантах реализации показанных на фиг.9-11, могут быть предусмотрены блоки 24 сравнения разности с константой (например, такие, как показано на фиг.5) для ограиичения нежелательной длины двоичных нулей или единиц в тех случаях, когда текущее значение вариации цифровой суммы равно, наперед заданной величине, например нулю. Помимо этого, предполагалось, что разность равна числу двоичньос единиц, содержащихся В кодовом слове, минус число двоичных нулей, содержащихся в этом слове. При неободимости разность может быть вычисена как функ1щя г,исла двоичных иуей минус число двоичных единиц одержащихся в кодовом слове.

ч/ -f

ш

J--g:-y.4

9 в 999

JBJV

;f 7f if

/rJ J,

д№

Miff.

w

fM

91 t

Off в

9 9 t 0

9 99 t I

.. -if ;

f f Of t

t ft 90

: -.jJ. ; t

9

9№,

JXP П-1Tfn l У (OOP О) yCW 00 и (О о 1 g (г / 1 f

& Qn -Г H z: I/ g ff & 0 t опт gjxr/ 1 t о f)yC / / / eJT

Г Г «я

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США S« 4201980, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1985-03-30—Публикация

1980-11-03—Подача