1

Изобретение относится к цифровой вычислительной технике и может быть использовано в цифровых измерительных устройствах различного назначения с визуальной индикацией результатов измерения, иапрнмер, для измерения случайных импульсов.

Известно пересчетное устройство с предварительной установкой времени счета, содержаи1,ее делитель частоты для выдачи сигнала времени счета, счетчики импульсов, дешифратор, мультиплексер, накапливающий счетчик, схемы И и две схемы совпадения для унравления счетом |1.

Недостатком такого устройства следует считать сложность управления счетом, что снижает надежность работы счетчика, а также отсутствие схемы сравнения по величине амплитуды и частоты повторения входных импульсов, из-за чего снижается точность счета, например, для случайных сигналов.

Пересчетное устройство, содержащее усилитель, компараторы верхнего и нижнего уровней, генератор времени счета, буферный элемент, счетчик импульсов, дешифратор и индикатор, вход которого соединен с выходом дешифратора, вход которого соединен с выходом счетчика импульсов, вход которого соединен с выходом генератора

времени счета. Вход устройства соединен через усилитель с первыми входами компараторов верхнего и нижнего уровней, вторые входы которы.х соединены с выходами источника опорного напряжения 21.

Недостатком этого устройства является относительно низкая точность счета.

Целью изобретения является повышение точности счета.

Поставленная цель достигается тем, что в пересчетное устройство, содержащее усилитель, компараторы верхнего и нижнего уровней, генератор времени счета, буферный элемент, счетчик импульсов, дешифратор и иидикатор, вход которого соединен с выходом дешифратора, вход которого соединен с выходом счетчика импульсов, вход которого соединен с выходом генератора времени счета, вход устройства соединен

через усилитель с первыми входами компараторов верхнего и нижнего уровней, вторые входы которых соединены с выходами источника опорного напряжения, введены триггер и логический узел, входы которого

соединены с выходами компараторов верхнего и нижнего уровней, выход логического узла соединен с первым входом буферного элемента, выход и второй вход которого соединены соответственно с вторым входом

счетчика импульсов и выходом триггера.

первый и второй входы которого соединены со вспомогательным выходом генератора времени счета и через контакты кнопки - с дополнительным выходом источника опорного напряжения.

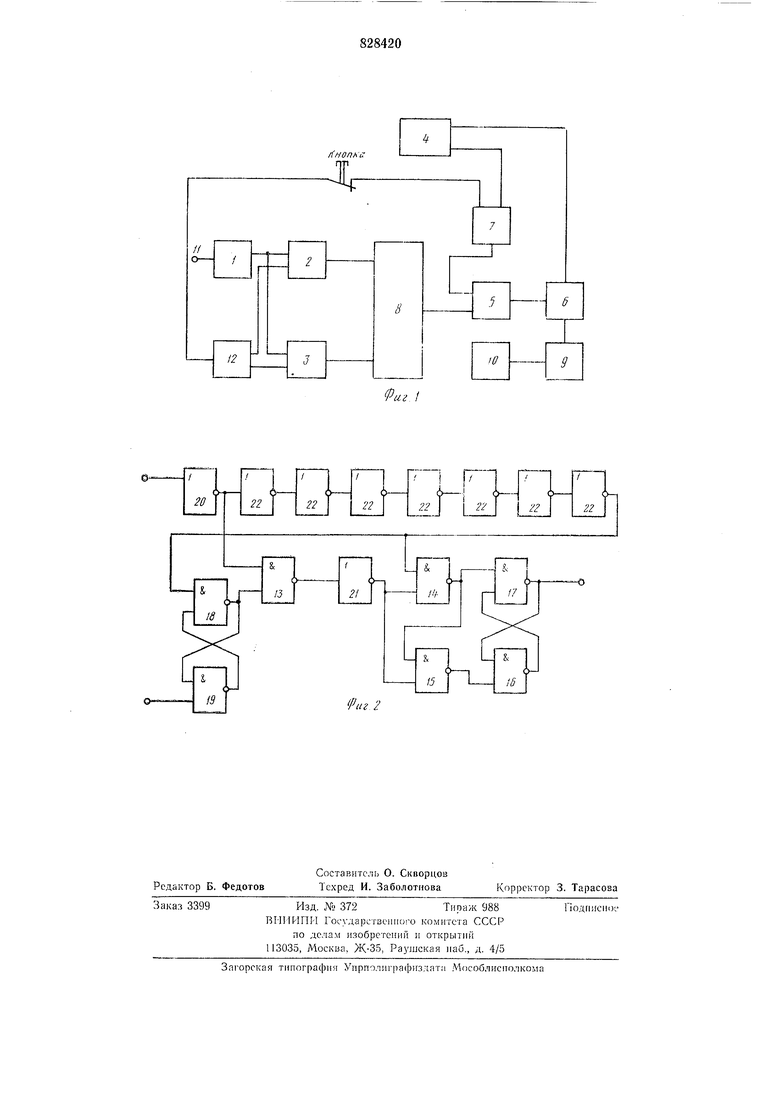

Логический узел содержит семь элементов И-НЕ, первый и второй инверторы и нечетное число вспомогательных инверторов, вход каждого из которых соединен с выходом предыдущего вспомогательного инвертора соединен с выходом первого ининвертора, вход первого вспомогательного инвертора соединен с выходом первого инвертора и первым входом первого элемента И-НЕ, выход которого через второй ийвертор соединен с первыми входами второго и третьего элементов И-НЕ, выход второго элемента И-НЕ соединен с вторым входом третьего элемента И-НЕ, выход которого соединен с первым входом четвертого элемента И-НЕ, выход которого соединен с первым входом пятого элемента И-НЕ, выход которого соединен с выходом логического узла и вторым входом четвертого -злемента М-НЕ; второй вход пятого элемента Н-НЕ соединен с выходом второго элемента Н-НЕ; второй вход, которого соединен с выходом последнего вспомогательного инвертора и первым входом шестого элемента И-НЕ, выход которого соединен с вторым входом первого и первым входом седьмого элементов И-НЕ; выход седьмого элемента И-НЕ соединен с вторым входом шестого элемента , а вход первого инвертора и второй вход седьмого элемента Н-НЕ соединены с входами логического узла.

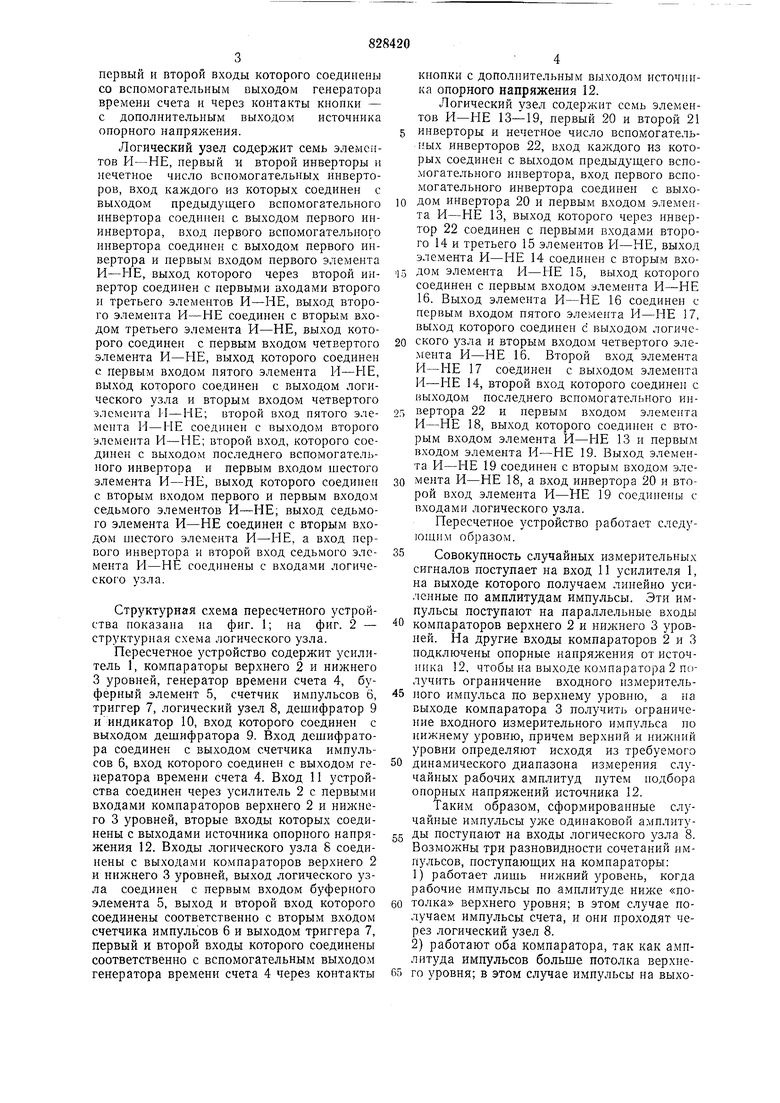

Структурная схема пересчетного устройства показана на фиг. 1; на фиг. 2 - структурная схема логического узла.

Пересчетиое устройство содержит усилитель 1, компараторы верхнего 2 и нижнего 3 уровней, генератор времени счета 4, буферный элемент 5, счетчик импульсов 6, триггер 7, логический узел 8, дешифратор 9 и индикатор 10, вход которого соединен с выходом дешифратора 9. Вход дешифратора соединен с выходом счетчика импульсов 6, вход которого соединен с выходом геператора времени счета 4. Вход 11 устройства соединен через усилитель 2 с первыми входами компараторов верхнего 2 и нижнего 3 уровней, вторые входы которых соединены с выходами источника опорного нанряжения 12. Входы логического узла 8 соедииены с выходами компараторов верхнего 2 и нижнего 3 уровней, выход логического узла соединен с первым входом буферного элемента 5, выход и второй вход которого соединены соответственно с вторым входом счетчика импульсов 6 и выходом триггера 7, первый и второй входы которого соединены соответственно с вспомогательным выходом генератора времени счета 4 через контакты

кнопки с дополнительным выходом источшгка опорного напряжения 12.

Логический узел содержит семь элементов И-НЕ 13-19, первый 20 и второй 21 инверторы и нечетное число вспомогатель1 ых инверторов 22, вход каждого из которых соединен с выходом предыдущего вспомогательного инвертора, вход первого вспомогательного инвертора соединен с выходом инвертора 20 и первым входом элемента И-НЕ 13, выход которого через инвертор 22 соединен с первыми входами второго 14 и третьего 15 элементов , выход элемента И-НЕ 14 соединен с вторым входом элемента И-НЕ 15, выход которого соединен с первым входом элемента И-НЕ 16. Выход элемента И-НЕ 16 соединен с первым входом пятого элемента И-НЕ 17, выход которого соединен с выходом логического узла и вторым входом четвертого элемента И-НЕ 16. Второй вход элемента И-НЕ 17 соединен с выходом элемента И-НЕ 14, второй вход которого соединен с выходом последнего вспомогательного инвертора 22 и первым входом элемента И-НЕ 18, выход которого соединен с вторым входом элемента И-НЕ 13 и первым входом элемента И-НЕ 19. Выход элемента И-НЕ 19 соединен с вторым входом элемента И-НЕ 18, а вход инвертора 20 и второй вход элемента И-НЕ 19 соединены с входами логического узла.

Пересчетное устройство работает следующим образом.

Совокупность случайных измерительных сигналов поступает на вход 11 усилителя 1, на выходе которого получаем лииейно уси.ченные по амплитудам импульсы. Эти импульсы поступают на параллельные входы компараторов верхнего 2 и нижнего 3 уровней. На другие входы компараторов 2 и 3 подключены опорные напряжения от источника 12, чтобы на выходе компаратора 2 получить ограничение входного измерительного импульса по верхнему уровню, а на выходе компаратора 3 получить ограничение входного измерительного импульса по нижнему уровню, причем верхний и нижний уровни определяют исходя из требуемого динамического диапазона измерения случайных рабочих амплитуд путем подбора опорных напряжений источника 12.

Таким образом, сформированные случайные импульсы уже одинаковой а.мплитуды поступают на входы логического узла 8. Возможны три разновидности сочетаний импульсов, поступающих на компараторы:

1)работает лишь нижний уровень, когда рабочие импульсы по амплитуде ниже «потолка верхнего уровня; в этом случае получаем импульсы счета, и они проходят через логический узел 8.

2)работают оба компаратора, так как амплитуда импульсов больше потолка верхнего уровня; в этом случае импульсы на выходе компараторов ложные и пе подлежат счету, поэтому посредством логического узла 8 они снимаются со счета. 3) амплитуды случайных импульсов ниже «потолка компаратора нижнего уровня; в этом случае па выходах компараторов сигналы отсутствуют, и счета не происходит. Таким образом, на выходе логического узла 8 получают сч ггываемый импульс той же последовательности, что и на входе 11 пересчетпого устройства, но ностоянной ампотитуды и удобный для счета; он поступает на один из входов буферного элемента 5, который одновременно служит формирователем импульсов счета необходимой полярности и управляющим устройством для счетчика 6. Управляющие импульсы на другой вход буферного элемента 5 нриходят с выхода триггера 7, работа которого синхроиизируется генератором времени счета 4 н источНИКОМ опорного напряжения 12 через контакты кнопки. Напряжение прекращения счета поступает с выхода генератора времени счета 4 па вход счетчика 6. В этой последовател: ности уп-равляюнщх сигналов триггер 7 для поддержания открытого состояиия буферного элемента 5 для считываемых импульсов, поступающих с выхода логического узла 8: триггер 7 управляет каналом прохождения всей совокупности случайных импульсов, который благодаря двойному управлению счетчика 6 практически считывает все импульсы, подлежангие считывапию. Кпопкой одновременно осуществляются сброс и начало работы триггера 7. Формула изобретен и я 1. Пересчетное устройство, содержащее усилитель, компараторы верхнего и нижнего уровней, генератор времени счета, буферный элемент, счетчик импульсов, деншфратор и индикатор, вход которого соединен с выходом дещифратора, вход которого соединен с выходом счетчика импульсов, вход которого соединен с выходом генератора времени счета, вход устройства соедииен через усилитель с первыми входами компараторов верхнего и нижнего уровней, вторые входы которых соединены с выходами источника опориого напряжения, отличающееся тем, что, с пелью новыщения точ82ности счета, в него введены триггер н логический узел, входы которого соединены с выходами компараторов верхнего и нижнего уровней, выход логического узла соединен с первым входом буферного элемента, выход п второй вход которого соединены соответственно с вторым входом счетчика импульсов и выходом триггера, первый и второй входы которого соединены соответственно с вспомогательным выходом генератора времени счета п через контакты кнопки - с дополнительным выходом 1СТОЧНИка онорного нанряжения. 2. Устройство по п. 1, отличающеес я тем, что логический узел содержит семь элементов И-НЕ, первый н второй инверторы и нечетное число вспомогательных инверторов, вход каждого из которых соедиие1 с выходом предыдущего вспомогательного инвертора, вход первого вспомогательпого инвертора соединен с выходом первого инвертора п первым BXO.JIOM первого элемента Н-НЕ, выход которого через второй инвертор соединен с первыми входами второго и третьего элементов И-НЕ, выход второго элемента И-НЕ соединен с вторым входом третьего элемента И-НЕ, выход которого соединен с первым входом четвертого элемента М-НЕ, выход Ktrroporo соединен с первым входом пятого элемента Н-НЕ, выход которого соединен с выходом логического узла и вторым входом четвертого элемента И-НЕ, второй вход нятого элемента И-НЕ соединен с выходом второго элемента И-НЕ, второй вход которого соедииен с выходом последнего вспомогательного инвертора н первым входом щестого элемента И-НЕ, выход которого соединен с вторым входом первого и первым входом седьмого элементов Н-НЕ, выход седьмого элемента И- НЕ соединен с вторым входом щестого элемента И-НЕ, а вход первого инвертора н второй вход седьмого элемента И-НЕ соединены с входами логического узла. Источники информацни, принятые во внимание при экспертизе 1.Натент ФРГ № 2314570, кл. Н 03 К 21/00, 1974. 2.Натент США № 3930142, кл. 235/92, 1975 (прототип). - jT-q f-I f-. mJ fPaz 2 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Пересчетное устройство | 1982 |

|

SU1129741A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Устройство для регистрации информации | 1984 |

|

SU1234858A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ АВТОМАТОМ ДЛЯ УКЛАДКИ КИРПИЧА | 1991 |

|

RU2028208C1 |

| Программно-управляемый генератор синусоидальных колебаний | 1985 |

|

SU1451830A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Устройство для дискретной записи и воспроизведения функций | 1981 |

|

SU982034A1 |

| Устройство для контроля параметров | 1985 |

|

SU1254441A1 |

| СИНХРОННЫЙ ДЕТЕКТОР | 1997 |

|

RU2124804C1 |

Авторы

Даты

1981-05-07—Публикация

1979-06-04—Подача