Изобретенце относится к цифровой вычислительной технике и может быть использовано в цифровых вычислительных машинах, в устройствах для отладки программ задач цифровых вычислительных управляняцих систем. Известны устройства для обработки цифровых данных, содержащие постоянные запоминающие устройства (ПЗУ) и полупостоянные запоминающие устройства (ППЗУ), подключенные через блок приема и вывода к числовым шина распределитель, осуществляющий выбор инфо мации из ПЗУ или ППЗУ в зависимости от текущего адреса и состояния регистров установки, причем по одним и тем же адресам информация может быть считана из ПЗУ или из ППЗУ LlJ. Недостатком этих устройств являет ся низкая пропускная способность, так как отсутствует режим одновремен ного считывания информации из ПЗУ и ППЗУ и формирования на ее основе новых кодовых комбинаций. Наиболее близким к предлагаемому по технической сущности является уст ройство, содержащее постоянное запоминающее устройство, полупостоянное запоминающее устройство, регистр адраса, подключенный выходом ко входам постоянного и полупостоянного запоминающих устройств, вторые входы которых связаны с шиной опроса, регистр базового адреса, подключенный выходом к третьему входу постоянного запоминающего устройства, выход которого и выход полупостоянного запоминающего устройства подключены к соответствующим входам регистра 2 Недостатком данного устройства является низкая пропускная способность, что обусловлено отсутствием средств формирования на выходе устройства кодовых комбинаций на основе информации, одновременно считанной из постоянного и полупостоянного запоминающих уст- . роиств.. Обычно в вычислительных машинах ППЗУ используется для хранения информации, которая может либо формироваться автоматически в процессе решения какой-либо задачи, либо записывается оператором для использования в течении заданного времени. Эта информация не имеет самостоятельного значения и дополняет основную, которая хранится в ПЗУ. Этим достигается, например, сокращение общего объема и оптимизация программ, фиксируемых в ПЗУ. Однако указанное

свойство устройства не позволяет формировать кодовые комбинадии на основе информации, считанной одновременно из ПЗУ и ППЗУ, что значитально повышает эффективность использования ППЗУ при повышении пропускной способности устройства. Например, в команде перехода, хранящейся в ПЗУ, может быть заменен адрес перехода, если эта часть команды приформировывается из ППЗУ, в другом случае в команде может быть заменен код операции, либо- гсризнаки ее модификации

Цель изобретения - повышение пропускной способности устройства.

Поставленная цель достигается тем что в устройство, содержащее блок постоянной памяти, соединенный первым входом с выходом регистра адреса и первым входом блока полупостоянной памяти, вторым входом - со вторым входом блока полупостоянной памяти и входной шиной опроса, а третий вход с выходом регистра базового адреса, введены блок анализа кодов л блок анализа признаков, причем первая группа информационных входов блока анализа кодов со.единена с группой выходов блока постоянной памяти, вторая группа информационных входов с -группой выходов информационных разрядов блока полупостоянной памяти, а группа управляющих входов с соответствующими выхода1 и блока анализа признаков, первый, второй и третий входы которого подключены соответствен но к первому и второму выходам дополнительных разрядов бло ка полупостоянной памяти и выходу регистра базового адреса, выходы блока анализа кодов являются соответствующими выходными кодовыми ЩИ нами устройства,.а также тем, что блок анализа кодов содержит первую и вторую группы элементов И, группу элементов ИЛИ, выходы которых являются соответствующими выходами блока, и группу элементов НЕ, входы которых являются соответствующими управляквдими входами блокА, первые входы элементов И первой группы подключены к соответствующим входам первой группь информационных входов блока, а вторые входы - ко входам соответствующих элементов НЕ, группы первые входы элементов И второй группы соединеныС соответствующими входами второй группы информационныхВХОДОВ блока, а вторые входы - с,вы ходами соответствующих элементов НЕ группы, первые входы элементов ИЛИ группы соединены с выходами соответствующих элементов И первой группы, а вторые входы - с выходами соответствугацих элементов И второй группы, а также тем, что блок анализа признаков содержит два регистра, входы которых являются соответственно

первым и вторым входами блока, схему сравнения, первый вход которой подключен к выходу второго регистра, второй вход к третьек у входу блока, а выход.- через злементыНЕ к первым входам элементов ИЛИ лруппь, выходы которых являются соответствующими выходами блока, а вторые ВХОДЫ подключены к выходам соответствуквдих элементов И групйы/ первымивходами соединенных с выходами соответствующих разрядов первого регистра, а вторыми входами - с выходом схемы сравнения.

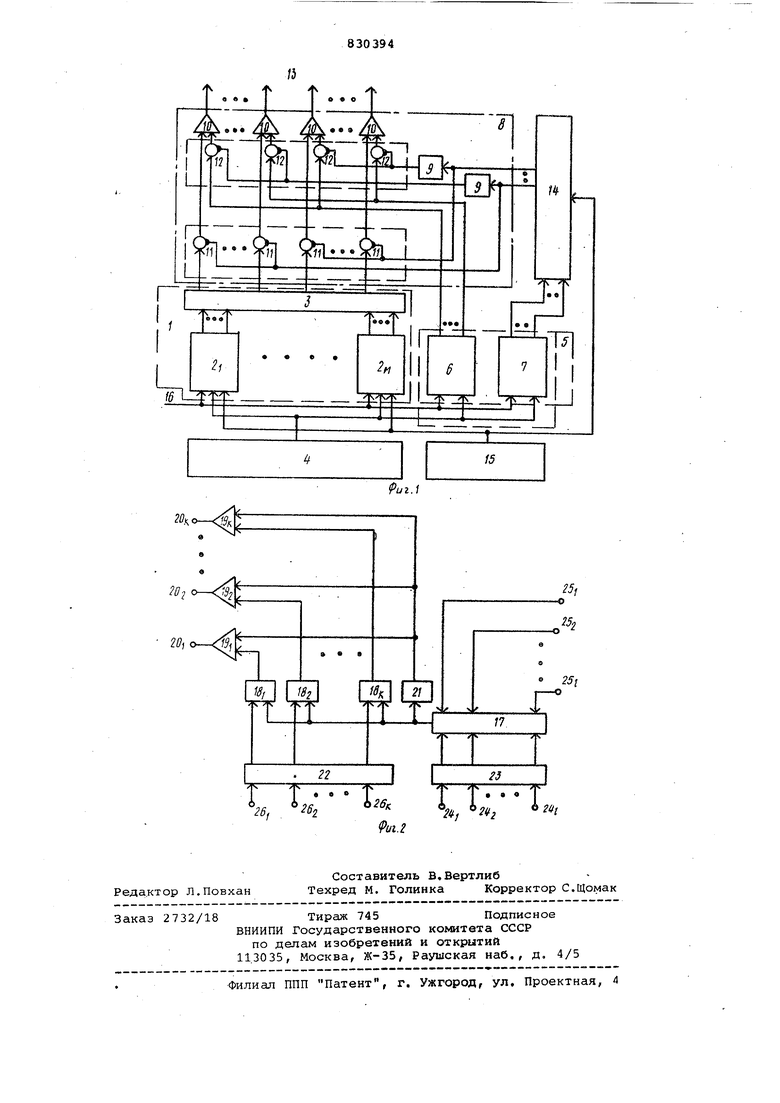

На фиг. 1 представлена блок-схема устройства; на фиг„2 - функциональная схема .блока анализа признаков.

Устройство содержит блок 1 постоянной памяти, состоящий из М модулей 2 постоянной памяти и группы элементов 3 ИЛИ, регистр 4 адреса, блок 5 полупостоянной памяти, состоящий ИЗ модулей 6 и 7, блока 8 формирования кодов, состоящего из элементов 9 НЕ группы, элементов 10 ИЛИ группы, элементов 11 И первой группы и элементов 12 И второй группы, выходные кодовые шины 13 устройства, блок 14 анализа признаков, регистр

15базового адреса и входную шину

16опроса. Блок 14 анализа признаков включает схему 17 сравнения, элементы 18 И группы, элементы 19 ИЛИ

.группы, выходы 20 блока, элемент 121 НЕ, первый 22 и второй 23 регистры, второй 24, третий 25 и первый 26 входы блока.

Устройство работает след ющим образом.

По коду в регистре 15 выбирается один из модулей 2 блока 1 постоянной памяти, а по коду в регистре 4 при появлении сигнала на шИне 16 производят считывание информации из выбранных модулей 2,6 и 7, причем из модуля 6 - информационные разряды, а из модуля 7 - разряды управляюдах признаков. Информация, считанная из модуля 7, расшифровывается в блоке 14 который, в первую очередь, производит сравнение кода управляющих признаков на входах 24 с содержимым регистра 15 поступакяцим по входам 25. Если код текущего базового адреса на входах 25 не совпадает с кодом управляющих признаков на входах 24, то с элемента21 НЕ на элементы 19 ИЛИ и выходы 20 блока на входы элементов 12 И выдается запрещающий сигнал, а на управлякадие входы элементов 11 и - разрешающий сигнал. Информация, с-читанная с одного из модулей 1, проходит через элементы 3 ИЛИ, ИИ и 10 ИЛИ на выходнне-шины 13, а информация, считанная из модуля 6, блокируется на элементах 12 И, в результате информация на выходах 13 точно соответствует информации, считанной из блока 1. Если же коды на входах 24 и 25 совпа дают,, то в блоке 14 через элементы 18 И формируется сигнал запрета определенных элементов 11 И. С помощью этого же сигнала, инвертированного на элементе 9 НЕ, открываются одноименные элементы 12 И. В резул тате этого на выходных шинах 13 формируется кодовая комбинация, составленная из информации, считанной из модулей 2 и 6. Таким образом, информация, записанная в модуле 7, указывает номера, модулей блока 1 постойнной памяти, а также адреса, при обращении к которым группа разрядов, также указанная в модуле 7, будет замаскирована и заменена rpynnofi разрядов, считанных из модуля 6. Таким образом, устройство обеспечивает повышение пропускной способности и повышает эффективность использования запоминающих устройств. По сравнению с известными устройствами для обработки цифровых данных предлагаемое позволяет сократить емкость ППЗУ, что снижает общую стоимость оборудования. Формула изобретения 1..Устройство для обработки цифро вых данных, содержеицее блок постоянной памяти, соединенный первым входом и с выходом регистра адреса и первым входом блока полупостоянной памяти, вторым входом - со вторым входом блока полупостоянной памяти и входной шиной опроса, а третий с выходом регистра базового адреса, отличающееся тем, что, с целью повышения пропускной способности устройства, в него введены блок анализа кодов и блок анализа признаков, причем первая группа информационных входов блока анализа кодов соединена с г упйой выходов блока ПОСТОЯННОЙ памят, вторая груп па информационных входов - с группо выходов информационных разрядов .блок полупостоянной памяти, а группа управлягацих входов - с соответствующими выходами блока анализа признаков первый, второй и третий входы которо подключены соответственно к первому и второму выходам дополнительных разрядов блока - полупостоянной памяти и выходу регистра базового адреса, выходы блока анашиза кодов являются соотбетствующигии выходными кодовыми щинами устройства. 2.Устройство по П.1, отличающееся тем, что блок анализа кодов содержит первую и вторуЛ группы элементов И, группу элементов ИЛИ, выходы которых являются соответствующими выходами блока, и группу элементов НЕ, входы которых являются сортветствукадими .управляющими входами блока, первые входы элементов И. первой группы подключены соответственно к входам первой группы информационных входов блока, а вторые входы - ко входам-соответствующих элементов НЕ группы, первые входы элементов И второй группы соединены соответственно со второй группой информационных входов блока, а вторые входы - с выходами соответствующих элементов НЕ группы, первые входы элементов ИЛИ группы соединены, с выходами соответствующих элементов И первой группы, а вторые входы с выходами соответствующих элементов И второй группы. 3.Устройство по П.1, о т л ичающееся тем, что блок анализа признаков содержит два регистра. Входы которых являются соответствен о первым и вторым вхсдс1МИ блока, схему сравнения, вход которой подключен к выходу второго {регистра, второй вход - к третьему входу блока, авыход через элементы НЕ - к первым входам элементов ИЛИ группы , выходы которых являются соответствующими выходами блока, а вторые входы подключены к выходам соответствующих элементов И группы, первыми входами соединенных с выходами соответствукхцих разрядов первого регистра, а вторыми входами - с выходом схемы сравнения. Источники информации принятые во внимание при экспертизе 1.Авторское свидетельство СССР 489107, кл. G 06 F 11/00, 1973. 2.Авторское свидетельство СССР по заявке № 2412295/18-24-, кл. 6 Об F 15/06, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией информации | 1986 |

|

SU1392596A1 |

| Устройство для отладки программ | 1980 |

|

SU960828A1 |

| Устройство для коррекции информации в блоках постоянной памяти | 1981 |

|

SU955213A1 |

| Устройство для управления памятью | 1979 |

|

SU834704A1 |

| ИНФОРМАЦИОННО-СПРАВОЧНОЕ УСТРОЙСТВО | 1994 |

|

RU2102789C1 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Кодер телевизионного сигнала | 1990 |

|

SU1753596A2 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ АНОМАЛЬНЫХ ЦИФРОВЫХ ОШИБОК ПРИ ПЕРЕДАЧЕ РЕЧИ МЕТОДОМ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИИ | 1999 |

|

RU2159470C1 |

| Цифровая логическая машина | 1974 |

|

SU558278A1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

Авторы

Даты

1981-05-15—Публикация

1979-02-14—Подача