(5) УСТРОЙСТВО для ОТЛАДКИ ПРОГРАММ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления памятью | 1979 |

|

SU834704A1 |

| Устройство для отладки программ | 1983 |

|

SU1104521A1 |

| Устройство для управления памятью | 1979 |

|

SU943726A1 |

| Устройство для обработки цифровых данных | 1980 |

|

SU964650A1 |

| Запоминающее устройство с кор-РЕКциЕй пРОгРАММы | 1979 |

|

SU809400A1 |

| Устройство для коррекции программ | 1982 |

|

SU1092514A1 |

| Устройство для откладки программ | 1987 |

|

SU1474656A1 |

| Устройство для модификации адреса зон памяти при отладке программ | 1987 |

|

SU1465887A1 |

| Запоминающее устройство | 1979 |

|

SU826423A1 |

| Устройство для отладки программ | 1984 |

|

SU1166122A1 |

1

Изобретение относится к вычислительной технике и может быть использовано при отладке программ цифровых вычислительных управляющих систем (ЦВС).

Известно устройство для отладки программ ЦВС, фиксируемых в постоянных запоминающих блоках (ПЗБ) цифровых вычислительных управляющих машин ШВУМ), содержащее ПЗБ и полупостоянный запоминающий блок (ППЗБ). На этапе отладки программ блок ППЗБ замещает один из блоков ПЗБ, т.е. информация, записанная в блоке ППЗБ, считывается в регистр команд вместо информации, записанной в блоке ПЗБ UJ.

Недостатком указанного устройства является отсутствие оборудования для выборки информации из ППЗБ по содержащимся в нем признакам и вывода для ее для регистрации, например, на цифропечатающее устройство.

Наиболее близким по технической сущности к предлагаемому являет.ся

устройство отладки программ для постоянного запоминающего устройства, содержащее ППЗБ, в.ыходы которого соединены с первыми входами коммутатора (блок приема и вывода команд совместно с блоком подключения ПЗУ), , подключенного вторыми входам к ПЗБ, ЦВУМ, а выходами - к числовым шинам, адресные шины, соединенные с входом регистра адреса (блоки формирования

10 адреса и адреса участка), первые выходы которого связаны с парными адресными входами ПЗБ, и через блок переадресации (распределитель), с первыми адресными входами ППЗБ, а вто15рые выходы - с вторыми адресными входами ПЗБ и ППЗБ, блок управления, первый вход которого подключен к управляющей шине, а выходы - к регистру адреса. Оборудование управления,

20 входящее в состав распределителя, Связано с входом блока переадресации, управляющими входами ППЗБ, коммутатора и ПЗБ. Устройство также содержит

39608284

шины для подключения регистрирующегоной и полупостоянной памяти и являютустройства, связанные с выходом бло- .ся группой адресных выходов устройстка управления, регистром адреса ива, управляющий вход устройства соевыходами коммутатора 2 .динен с первым входом блока управлеНедостатком известного устройства 5 адресный выход устройства соедиявляется отсутствие в нем средствнен с информационным входом счетчика

автоматизации получения систематичес-адреса, Т1Нформационный выход которокой информации о характеристиках от-го соединен с входом блока задания

лаживаемых программ и процесса отлад-адреса, адресный и управляющий выходы

ки. Так, например, при отладке про- юблока задания адреса соединены соотграмм необходимо знать структурныеветственно с вторым входом блока поособенности алгоритмов, в частностилупостоянной памяти и с вторым вхостатистику использования логических,дом блока управления, введены первая

арифметических и других операций ви вторая группы элементов И, блок

управляющих алгоритмах, знать распре- isсравнения, регистр маски, регистр

деление памяти, находить свободные .эталонов и второй коммутатор, причем

ячейки. Кроме того, ППЗУ может со-выход блока постоянной памяти соедидержать дополнительную информацию внен с первым информационным входом

виде идентификаторов, с помощью кото-второго коммутатора, выход которого

рь1Х определяются команды, содержимое JQсоединен с первыми входами элементов

которых в продессе отладки корректи-И первой группы, выход регистра масруется, а также определяется- времяки соединен с первыми входами элеменвведения и характер корректуры. Дна-тов И второй группы и с вторыми вхолиз такого рода данных позволяет болеедами элементов И первой группы, выхообосноваПно подходить к организации jjды которых соединены с первой группой

процесса отладки математического обе-входов схемы сравнения, выход блока

спечения ЦВМ.полупостоянной памяти соединен с втоКроме того, в процессе отладки воз-рыми входами элементов И второй .групникает необходимость сравнения ин-пы, выходы которых соединены с второй

формации, содержащейся в ПЗУ и ППЗУ, ,группой входов схемы сравнения, выход

с регистрацией соответствующих отли-схемы сравнения соединен с третьим

чий содержимого той или иной памяти.входом блока управления, шестой выЦелью изoбpeteния является расши-ход которого соединен с управляющим

рение функциональных возможностей уст-входом второго коммутатора, выход реройства за счет обеспечения возможно-гистра эталонов соединен с вторым упсти получения статистической информа- равляющим входом второго коммутатора, ции о характеристиках отлаживаемых Кроме того, блок управления содерпрограмм и процесса отладки.жит первый, второй и третий элементы

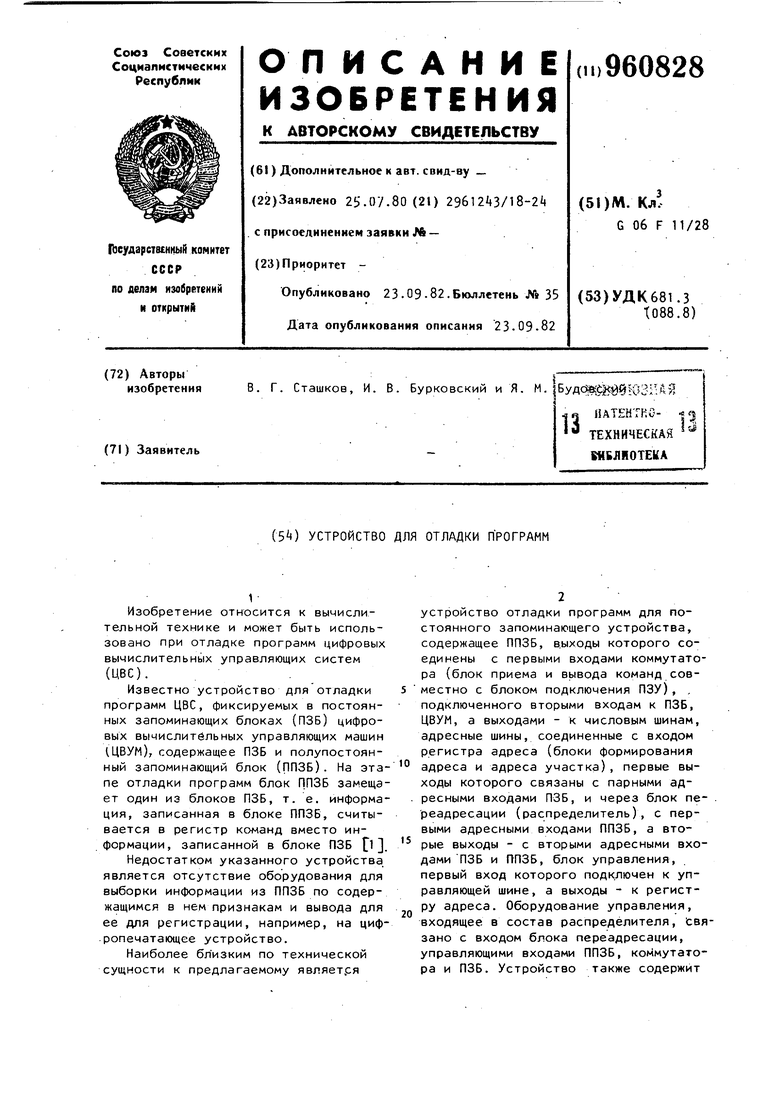

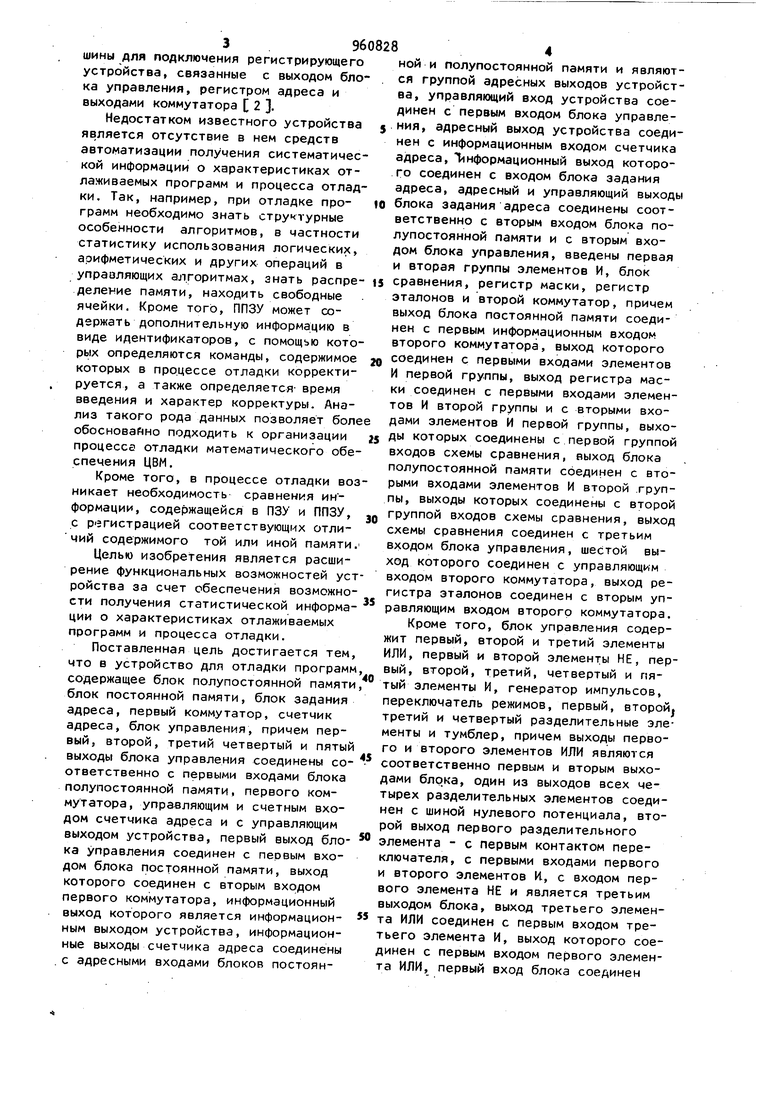

Поставленная цель достигается тем,ИЛИ, первый и второй элементы НЕ, перчто в устройство для отладки программ,вый, второй, третий, четвертый и пясодержащее блок полупостоянной памяти,тый элементы И, генератор импульсов,

блок постоянной памяти, блок заданияпереключатель режимов, первый, второй|

адреса, первый коммутатор, счетчиктретий и четвертый разделительные элеадреса, блок управления, причем пер-менты и тумблер, причем выходы первовый, второй, третий четвертый и пятыйго и второго элементов ИЛИ являются

выходы блока управления соединены со- соответственно первым и вторым выхоответственно с первыми входами блокадами блока, один из выходов всех чеполупостоянной памяти, первого ком-тырех разделительных элементов соедимутатора, управляющим и счетным вхо-нен с шиной нулевого потенциала, втодом счетчика адреса и с управляющимрой выход первого разделительного

выходом устройства, первый выход бло- элемента - с первым контактом перека управления соединен с первым вхо-ключателя, с первыми входами первого

дом блока постоянной памяти, выходи второго элементов К, с входом перкоторого соединен с вторым входомвого элемента НЕ и является третьим

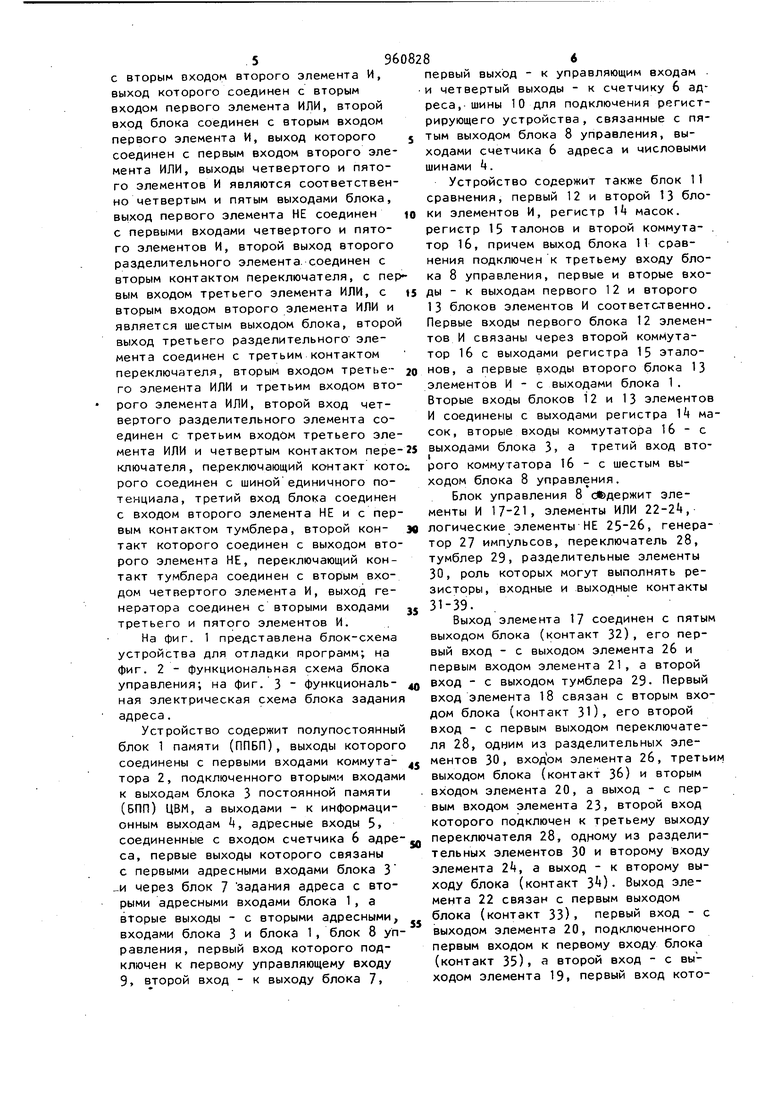

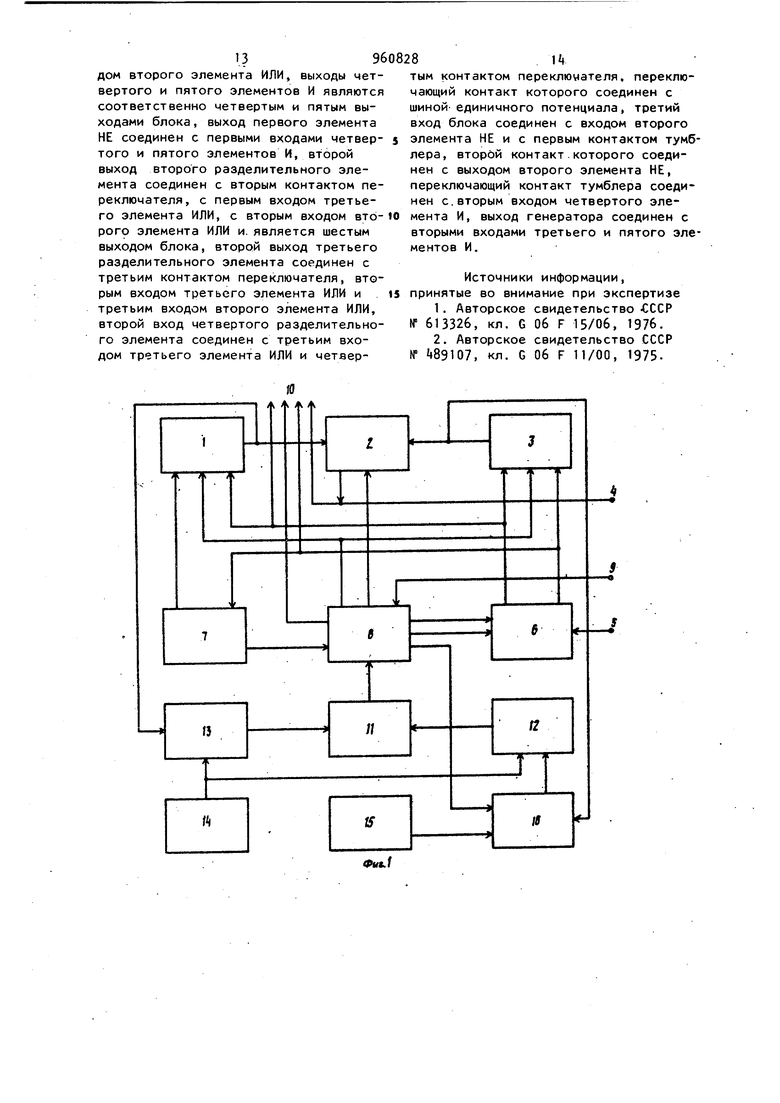

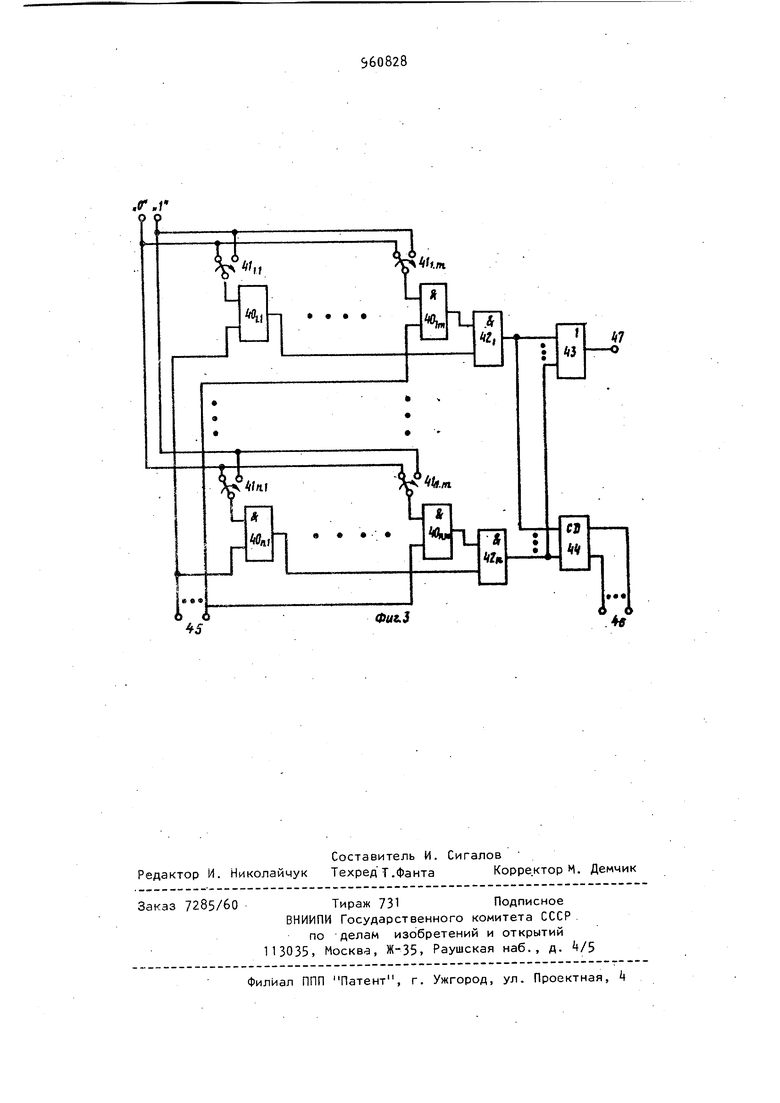

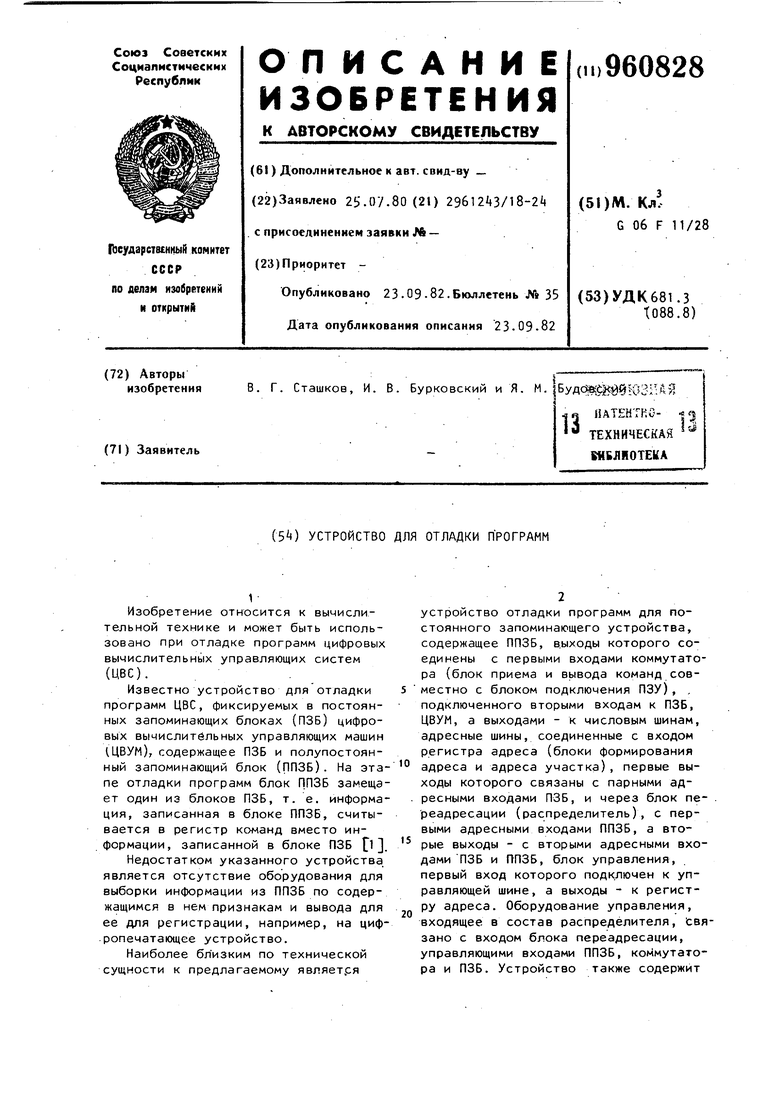

первого коммутатора, информационныйвыходом блока, выход третьего элеменвыход которого является информацион- та ИЛИ соединен с первым входом треным выходом устройства, информацион-тьего элемента И, выход которого соеные выходы счетчика адреса соединеныдинен с первым входом первого элеменс адресными входами блоков постоян-та ИЛИ, первый вход блока соединен с вторым входом второго элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, второй вход блока соединен с вторым входом первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выходы четвертого и пятого элементов И являются соответственно четвертым и пятым выходами блока, выход первого элемента НЕ соединен с первыми входами четвертого и пятого элементов И, второй выход второго разделительного элемента, соединен с вторым контактом переключателя, с пер вым входом третьего элемента ИЛИ, с вторым входом второго элемента ИЛИ и является шестым выходом блока, второй выход третьего разделительного элемента соединен с третьим контактом переключателя, вторым входом третьего элемента ИЛИ и третьим входом второго элемента ИЛИ, второй вход четвертого разделительного элемента соединен с третьим входом третьего элемента ИЛИ и четвертым контактом переключателя, переключающий контакт кото рого соединен с шиной единичного потенциала, третий вход блока соединен с входом второго элемента НЕ и с первым контактом тумблера, второй контакт которого соединен с выходом второго элемента НЕ, переключающий контакт тумблера соединен с вторым входом четвертого элемента И, выход генератора соединен с вторыми входами третьего и пятого элементов И. На фиг. 1 представлена блок-схема устройства для отладки программ; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - функциональная электрическая схема блока задания адреса. Устройство содержит полупостоянный блок 1 памяти (ППБП), выходы которого соединены с первыми входами коммутатора 2, подключенного вторыми входами к выходам блока 3 постоянной памяти (ВПП) ЦВМ, а выходами - к информационным выходам k, адресные входы 5, соединенные с входом счетчика 6 адреса, первые выходы которого связаны с первыми адресными входами блока 3 -И через блок 7 задания адреса с вторыми адресными входами блока 1, а вторые выходы - с вторыми адресными, входами блока 3 и блока 1, блок 8 управления, первый вход которого подключен к первому управляющему входу 9, второй вход - к выходу блока 7, первый выход - к управляющим входам и четвертый выходы - к счетчику 6 адреса,-шины 10 для подключения регистрирующего устройства, связанные с пятым выходом блока 8 управления, выходами счетчика 6 адреса и числовыми шинами 4. Устройство содержит также блок 11 сравнения, первый 12 и второй 13 блоки элементов И, регистр I масок. регистр 15 талонов и второй коммута- . тор 16, причем выход блока П сравнения подключен к третьему входу блока 8 управления, первые и вторые входы - к выходам первого 12 и второго 13 блоков элементов И соответственно, Первые входы первого блока 12 элементов И связаны через второй коммутатор 16 с выходами регистра 15 эталонов, а первые входы второго блока 13 элементов И - с выходами блока 1. Вторые входы блоков 12 и 13 элементов И соединены с выходами регистра 1А масок, вторые входы коммутатора 16 - с выходами блока 3, а третий вход второго коммутатора 16 - с шестым вырого коммутатора ходом блока 8 управления. Блок управления 8 (Задержит элементы И 17-21, элементы ИЛИ , логические элементы НЕ 25-26, генератор 27 импульсов, переключатель 28, тумблер 29, разделительные элементы 30, роль которых могут выполнять резисторы, входные и выходные контакты 31-39. Выход элемента 17 соединен с пятым выходом блока (контакт 32), его первый вход - с выходом элемента 26 и первым входом элемента 21, а второй вход - с выходом тумблера 29. Первый вход элемента 18 связан с вторым входом блока (контакт 31), его второй вход - с первым выходом переключателя 28, одним из разделительных элементов 30, входЪм элемента 26, третьим выходом блока (контакт 36) и вторым входом элемента 20, а выход - с первым входом элемента 23, второй вход которого подключен к третьему выходу переключателя 28, одному из разделительных элементов 30 и второму входу элемента , а выход - к второму выходу блока (контакт З). Выход элемента 22 связан с первым выходом блока (контакт 33), первый вход - с выходом элемента 20, подключенного первым входом к первому входу блока (контакт 35), я второй вход - с выходом элемента 19, первый вход которого соединен с выходом генератора 27и вторым входом элемента 21, а вто рой вход - с выходом элемента 2k, пер вый вход которого связан с четвертым выходом переключателя 28 и одним из разделительных элементов 30. Второй выход переключателя 28 подключен к одному из разделительных элементов 30, третьему входу элемента 2k, шестому выходу блока (контакт 38) и третьему входу элемента 23. Третий вход блока (контакт 39) соединен с первым входом тумблера 29 и входом элемента 25, выход которого связан с вторым входом тумблера 29, четвертый выход блока (контакт 37) соединен с выходом элемента 21. На вход переключателя 28подается сигнал .логической 1, а на резисторы 30 - сигнал логического О. Блок 7 задания адреса (фиг. 3) содержит элементы И kO г, т организован ные в группы, где п - номер группы, m - порядковый номер элемента в группе. Блок Содержит также тумблеры tl , п, т, организованные в группы аналогично элементам 0 п, т. Каждая группа тумблеров образует регистр установки. В состав блока входят также логические элементы И , логический элемент ИЛИ 43, шифратор 4, входные kS и выходные адресные 46 контакты, выходной управляющий контак 47. Первые входы всех элементов kO п, m подключены на выходах одноименных тумблеров 41 п, т, вторые входы всех элементов 40 п, m с одинаковым первым индексом соединены с одним из входных контактов 45. Выходы элементов 40 п, m каждой группы связаны с входами одного из элементов . Выходы элементов подключены на входы элементов 43 и 44. Выход элемента 43 связан с выходным управляющим контактом 47, а выходы шифратора 44 - с выходными контактами 46. На первые входы всех тумблеров 41 п, m подключен сигнал логического О, на вторые входы - сигнал логической 1. Устройство работает совместно с ДВУМ, программы которой подлежат отладке. При этом числовые 4, адресные 5 и управляющие 9 шины подключаются к соответствующим шинам ЦВУМ. Регистрирующее устройство, в качестве которого может быть использована, например, печатающая машинка, соединяется с шинами 10. Перед началом работы в блок 1 тем или иным способом записы988 вается информация, которая , представляет собой коды команд отлаживаемой программы. С этой целью устройство отладки должно содержать дополнительное оборудование записи. В противном случае блок 1 извлекается из устройства отладки и подключается к автономному оборудованию, с помощью которого производится запись информации. В режиме Отладка устройство обеспечивает совместную работу блоков 3 и 1 таким образом, что необходимая информация извлекается на числовые шины 4 либо из блока 3, либо из блока 1. Наличие блока 7 задания адреса обеспечивает разбиение всего массива адресов блока 1 на участки. С помощью регистров установки блока 7 каждому участку блока 1 присваивается определенное место в массиве адресов блока 3. В режиме Отладка переключатель 28 блока 8 управления устанавливается в положение Т. При этом с переключателя 28 на один из входов элемента 20 поступает сигнал 1. Сигнал, поступающий из ЦВУМ на шину 9 устройства, проходит через элементы 20 и 22 на первый выход 33 блока 8 и далее на управляющие входы блоков 1 и 3- Код адреса поступает в блок 3 с выходов счетчика 6. В блок 1 со счетчика 6 адреса поступают только младшие разряды адреса, старшие разряды подаются на входы блока 7. При этом входной код адреса на элементах 40 п, m сравнивается с кодом, набранным на регистрах установки, выполненных на тумблере 41 п, т. При совпадении кода, пост;,пившего в блок 7, с кодом, установленным, например, на тумблерах ,, на всех входах элемента 42 имеются сигналы 1. Таким образом, и на выходе 47 блока сигнал 1, который поступает через второй вход блока 8 (контакт 31) на элемент 18. На втором входе элемента 18 в установленном режиме имеется сигнал 1. Следовательно, на выходе элемента 23 (втором выходе блока 8, контакт 34) сигнал такой же, как и на контакте 31. Поскольку этот сигнал поступает на управляющий вход коммутатора 2, то в результате на выходах его, т. е. на числовых шинах устройства, находится информация,поступившая на входы коммутатора 2 из блока 1 в том случае. если в блоке 7 произойдет совпадение входного кода с содержимым одного из регистров установки, или информация на выходе блока 3, если такого совпадения в блоке 7 нет, Старшие разряды кода адреса поступают на входы блока I с шифратора kk блока 7 через его выходы 6. Код на выходе элемента 0 зависит от содержимого регистров установки (тумблера 41) и кода на его контактах Ц. Та ким образом производится произвольное наложение зон блока 1 на массивы адре сов блока 3. В этом режиме на третьем выходе блока 8 (контакт 36) формирует ся сигнал 1, который разрешает поступление в счетчик 6 кода адреса с адресных шин 5. На выходе элемента 2б находится сигнал О, благодаря чему запрещается прохождение через элемент 21 и контакт 37 (четвертый выход блока 8) в блок 6 счетных импульсов с генератора 27. В этом режиме, также бла годаря сигналу, на входе элемента 2б, запрещается выдача в регистрирующее устройство шины 10 управляющего сигна ла с выхода элемента 17 (контакт 32 блока 8). В режиме вывода информации из блока 1 на регистрирующее устройство по результатам сравнения его содержимого с содержимым регистра 15 эталонов переключатель 28 блока 8 устанавливается в положение II. При этом через резистор 30 на один из входов элемента 20 поступает сигнал О, что блокирует поступление в блок 8 сигналов с шины 9. Поскольку на выходе элемента 26 в этом режиме сигнал 1., то импульс с генератора 27 через элемент 21 и контакт 37 поступает на счетчик 6 адреса, на его счетный вход Поступление в него кода с шины 5 блокируется сигналом О с третьего выхода блока 8 (контакт Зб). Сигналы с генератора 27 через элементы 19 и 22 проходят на первый выход блока 8 (контакт 33), обеспечивая запуск блоков 1 и 3i так как сигнал 1 на втором входе элемента 19 обеспечивается элементом 2k. Поскольку на одном из входов элемента 23 в этой режиме постоянно присутствует сигнал, поступающий с переключателя 28, на втором входе блока 8 (контакт 3), сигнал 1, Благодаря этому на числовых шинах 4 в этом режиме находится только информация, считываемая из бло ка 1. Работа блока 7 в этом режиме и всех последующих аналогична работе в режиме Отладка. Сигнал 1 на шестом выходе блока 8 (контакт 33) разрешает поступление в блок 12 через коммутатор 16 содержимого регистра 15 эталонов. С помощью кода, установленного на регистре It масок, часть разрядов кода эталона в блоке 12 маскируется, что означает выработку на соответствующих выходах блока 12 постоянных потенциалов, не зависящих от содержимого указанных разрядов регистра 15. Аналогичным образом происходит маскирование в блоке 13 тех же разрядов информации, поступающей в блок 13 с выходов блока 1. Результат сравнения кодов в блоке 11 поступает на третий вход блока 8 (контакт 39)- При этом, например, сигнал равнозначности . Тумблер 29 соответствует уровню в блоке 8 устанавливается в соответствии с тем, что требуется вывести на регистрирующее устройство коды совпадающие или не совпадающие с эталоном. Во втором случае производится инверсия сигнала, поступающего с контакта 39, с помощью элемента 25- Управляющий сигнал на шины 10 для подключения регистрирующего устройства поступает с элемента 17 через пятый выход блока 8 (контакт 32) . Кроме того, на шинах 10 присутствует выводимая информация и соответствующий ей код адреса. В режиме вывода информации из блока 1. на регистрирующее устройство по результатам сравнения его содержимого с содержимым блока 3 переключатель 28 8 устанавливается в положение III. В отличие от предыдущего режима на шестом выходе блока 8 (контакт 38) постоянно формируется сигнад О. В результате на выход блока 16 поступает информация не с регистра 15i а с выходов блока 3. В остальном устройство работает так же, как и в предыдущем режиме. В режиме вывода информации из блока 3 на регистрирующее устройство по результатам сравнения его содержимого с содержимым блока 1 переключатель 28 блока 8 устанавливается в положение IV. В отличие от предыдущего режима на любом из входов элемента 23 блока 8 находится сигнал О , такой же сигнал и на втором выходе блока 8 (контакт. З). В результате на числовых шинах k в этом режиме присутствует информация, считываемая из бло1196ка 3- Следовательно, она и выводится в устройство регистрации вместе с кодом адреса через шины О, В предлагаемом устройстве обеспечена автоматизация получения статис тинеской информации о характере отлаживаемых программ и процесса отладки. Таким образом, появляется возможность оперативного получения необходимой систематической информации, например, О о ходе отладочных работ. На основании полученной информации могут быть обоснованно сделаны переходы от одного технологического этапа отладки к другому. В результате этого оптимизи- 5 И руется процесс отладки, что приводит к повышению качества работ, к сокращению сроков отладки или к повышению степени отлаженности математического обеспечения при заданных сроках отладки. Формула изобретения 1. Устройство для отладки программ содержащее блок полупостоянной памяти блок постоянной памяти, блок задания адреса, первый коммутатор-, счетчи адреса и блок управления, причем первый, второй, третий, четвертый и пятый выходы блока управления соединены соответственно с первыми входами блока полупостоянной памяти, первого ком мутатора, управляющим и счетным вхо--, дом счетчика адреса и с управляющим выходом устройства, первый выход блока управления соединен с первым входом блока постоянной памяти, выход которого соединен с вторым входом первого коммутатора, информационный выход которого является информационным выходом устройства, информационные выходы счетчика адреса соединены с адресными- входами блоков постоянной и полупостоянной памяти и являются группой адресных выходов устройства j управляющий вход устройства соединен с первым входом блока управления, адресный выход устройства соединен с информационным входом счетчика адреса, информационный выход которого соединен с входом блока задания адреса, адресный и управляющий выход блока задания адреса соединены соответственно с вторым входом блока полу постоянной памяти и с вторым входом блока управления, отличающееся тем, что, с целью расширения 8 функциональных возможностей устройства за счет обеспечения возможности получения статистической информации о характеристиках отлаживаемых программ и процесса отладки., в него введены первая и вторая группы элементов И, блок сравнения, регистр маски, регистр эталонови второй коммутатор, причем выход блока постоянной памяти соединен с первым информационным входом второго коммутатора, выход которого соединен с первыми входами элементов И первой группы, выход регистра маски соединен с первыми входами элементов второй группы и с вторыми входами элементов И первой группы, выходы которых соединены с первой группой входов схемы сравнения., выход блока полупостоянной памяти соединен с вторыми входами элементов И второй группы, выходы которых соединены с второй группой входов схемы сравнения, выход схемы сравнения соединен с третьим входом блока управления, шестой выход которого соединен с управляющим входом второго коммутатора, выход регистра эталонов соединен с вторым управляющим входом второго коммутатора . 2, Устройство по п. 1, отличающееся тем, что блок управления содержит первый, второй и третий элементы ИЛИ, первый и второй элементы НЕ, первый, второй, третий, четвертый и пятый элементы И, генератор импульсов, переключатель режимов, первый, второй, третий и четвертый разделительные элементы и тумблер, причем выходы первого и второго элементов ИЛИ являются соответственно первым и вторым выходами блока, один из выходов всех четырех разделительных элементов соединен с шиной нулевого потенциала, второй выход первого разделительного элемента соединен с первым контактом переключателя, с первыми входами первого и второго элементов И, с входом первого элемента НЕ и является третьим выходом блока, выход третьего элемента ИЛИ соединен с первым входом третьего элемента И, выход которого соединен с первым входом первого элемента ИЛИ, первый вход блока соединен с вторым входом BTOpord элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, второй вход ,блока соединен с вторым входом первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выходы четвертого и пятого элементов И являются соответственно четвертым и пятым выходами блока, выход первого элемента НЕ соединен с первыми входами четвертого и пятого элементов И, второй выход второго разделительного элемента соединен с вторым контактом переключателя, с первым входом третьего элемента ИЛИ, с вторым входом второг9 элемента ИЛИ и. является шестым выходом блока, второй выход третьего разделительного элемента соединен с третьим контактом переключателя, вторым входом третьего элемента ИЛИ и . третьим входом второго элемента ИЛИ, второй вход четвертого разделительного элемента соединен с третьим входом третьего элемента ИЛИ и четаер98 тым контактом переключателя, переключающий контакт которого соединен с шиной единичного потенциала, третий вход блока соединен с входом второго элемента НЕ и с первым контактом тумблера, второй контакт.которого соединен с выходом второго элемента НЕ, переключающий контакт тумблера соединен с.вторым входом четвертого элемента И, выход генератора соединен с вторыми входами третьего и пятого элементов И. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 613326, кл. G Об F 15/06, 1976. 2.Авторское свидетельство СССР If 89107, кл. G 06 F 11/00, 1975.

О Л

63

Фиг. 2

Авторы

Даты

1982-09-23—Публикация

1980-07-25—Подача