(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СИСТЕМЫ ПЕРЕДАЧИ ДИСКРЕТНЫХ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля системы передачи дискретных сигналов | 1980 |

|

SU920813A2 |

| Устройство для контроля систем передачи сигналов | 1978 |

|

SU711610A1 |

| Устройство для контроля систем передачи сигналов | 1988 |

|

SU1522269A2 |

| Система передачи и приема цифровой информации | 1988 |

|

SU1559361A1 |

| Устройство для ввода-вывода информации | 1989 |

|

SU1615694A2 |

| Адаптивное вычислительное устройство | 1977 |

|

SU734679A1 |

| Генератор псевдослучайных чисел | 1980 |

|

SU935951A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1990 |

|

SU1795520A1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА ПЕРЕДАЧИ ДАННЫХ С ЗАЩИТОЙ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА | 2010 |

|

RU2422885C1 |

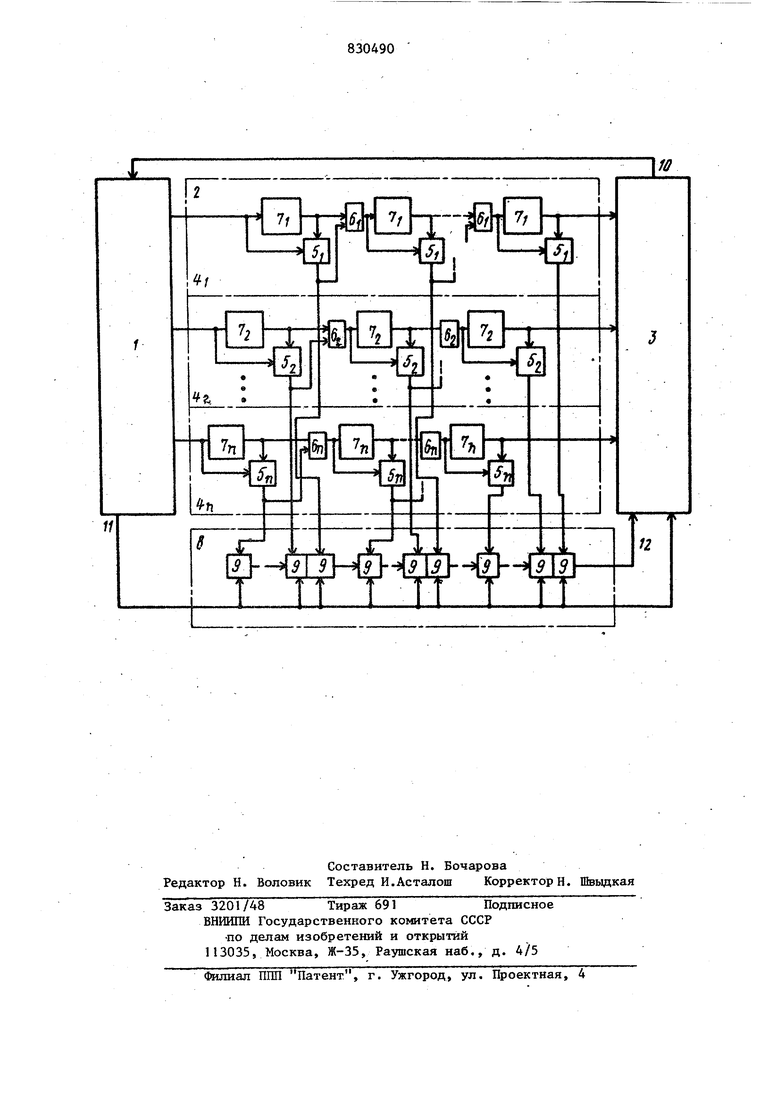

Изобретение относится к вычислительной технике и передачи информаци и может быть использовано для отыска ния места отказов в линиях связи меж ду цифровыми вычислительными устройс Известно устройство для контроля систем передачи дискретных сигналов, содержащее передающий цифровой вычис лительный блок, соединенный с приемным цифровым вычислительным блоком каналами связи, каждый из которых со держит соединенные последовательно усилители, кроме того, выходы одноимённых усилителей всех каналов соединеил со ВХОДШ4И соответствующего элемента И, выход которого соединен с первым входом соответствующего триггера, причем вторые входы всех триггеров объединены и соединеп | с выходом приемного цифрового вычислительного блока, входы которого соединены с соответствующими выходами триггеров ПЗ-. Недостатком указанного устройства являются его узкие функциональные возможности, заключающиеся в том, что при нескольких отказах в линии связи выявляется только один отказ, а множественные отказы выявляются только последовательно. Это приводит к непроизводительным затратам времени на ремонт линий связи. Наиболее близким по технической сущности к изобретению является устройство для контроля систем передачи сигналов, содержащее передающий цифровой блок, который через линии связи, содержащие последовательно включенные усилители, соединен с информационнымн входами приемного цифрового вычнслительного блока, выходы одноименных усилителей соединены со входами соответствующих элементов И, регистр сдвига, первые входы ячеек которого соединены с выходами соответствукнцих элементов И, вторые входы объединены и .соединены с первым управпяющим выходом передающего цифрового вычислительного блока, второй управляюпщй выход которого соединен с третьими входами ячеек регистра сдвига и первым управляющим входом приемного цифрового вычиспительного блока, ячейки регистра сдвига соединены последлвательно и выход последней из них соединен со вторым управляющим входом приемного цифрового вычислительного блока f.}. Недостаток такого устройства заключается в том, что при нескольких отказах в различных усилителях или линиях связи выявляется только один отказ, т.е. точность работы устройства невысокая, Кроме того, в устройстве не фикси руется момент появления отказов, а д контроля работоспособности системы либо необходимо регулярно выделять специальные временные интервалы - ци лы контроля, либо иметь дополнительное устройство определения наличия отказов. Это резко снижает эффективность функционирования системы. Цель изобретения - повьшение точности устройства. Поставленная цель достигается тем что в устройство для контроля систем передачи дискретных сигналов, содержащей передающий цифровой вычислител ный блок, первые выходы которого сое динены со входами первых усилителей П-канальной линии связи, выходы последних усилителей которой соединены с первыми входами приемного цифровог вычислительного блока, регистр сдвиг первые входы ячеек которого объединен и соединены со вторым выходом переда щего цифрового вычислительного блока и вторым входом приемного цифрового вычислительного блока, выход каждой предьщущей ячейки регистра сдвига соединен со входом последующей ячейк выход последней ячейки регистра сдви роединен с третьим входом приемного /цифрового вычислительного блока, выход приемного цифрового вычислительн го блока соединен со входом передающего цифрового вычислительного блока и в каждый канал линии связи введены элементы неравнозначности и элементы ИЛИ, первый и второй входы каждого элемента неравнозначности соединены соответственно со входом и выходом соответствующего усилителя выход-с тр тьим входом соответствующей ячейки егистра сдвига -И с первым .входом оответствующего элемента ИЛИ, второй ход которого соединен с выходом преыдущего усилителя,,- а. выход - со. вхоом последующего усилителя ,. На чертеже представлена схема предагаемого устройства. Устройство содержит передающий ифровойвычислительный блок 1, п-каальную линию 2 связи, приемный цифовой вычислительный блок. 3. Каждый канал 4-- лнйии 2 связи содержит элементы 5 -З неравнозначности (суматоры по модулю 2) 5 элементы ИЛИ 6 -6. усилители 7 7. Устройство также содержит регистр 8 сдвига с ячейками 9, управляющуто шину 10, щинь 1 1 и 12 импульсов сдвига. Устройство работает следующим образом. Данные от передающего цифрового вычислительного блока 1 по п-канальной. линии 2 связи поступают в приемный цифровой вычислительный блок 3. При этом постоянно контролируется работоспособность усилителей 7 путем сравнегжя значений сигналов на входе и на выходе элементами 5 неравнозначности. При нормальной работе линий 2 связи на выходе элемента 5 - низкий уровень. В случае .нарушения, работоспособности усилителя 7 на выходе элемента 5 неравйозначности появится сигнал высокого уровня, который обеспечит запись 1 в соответствующую ячейку {Регистра 8 сдвига. Импульсы сдвига на регистр 8 по шине 11 поступают постоянно, поэтому 1, продвигаясь по регистру 8, в дальнейшем по. шине 12 передается в приемный цифровой вычислительный блок 3, и ее«появление будет свидельствовать о иарущении работоспособности одного из -канагюв линий связи и необходимости перехода к режиму контроля. Начало режима контроля задает управляющий сигнал, поступаюгций в блок по шине 10. В режиме контроля определяется место отказа с точностью до элемента. В исходном состоянии все ячейки 9 регистра 8 сдвига обнулены. Дпя отыскания отказов, например Устойчивый О, а именно такой тип отказа наиболее часто встречается при передаче дискретных сигналов, передающий цифровой вычислительный блок I посыпает в линию 2 связи комбинацию 1...1. Элементы 5 неравнозначности, подключенные к отказавшим усилителям 7s формируют входной сигнал высокого уровня, который записывает 1 в сО ответствующую ячейку 9 регистра 8 сдвига. Затем передающий цифровой вычислительный блок I вьщает серию импульсов сдвига по шине i1, обеспе° чивающих последовательную передачу содержимого всех ячеек регистра 8 сдвига по шине I2 в приемный цифрово вычислительный блок 3 для анализа. Допустим, что в первом канале отказали первые два усилителя , во вто ром - последний усилитель7 , а в последнем канале - первый и последни усилитель. 7. Тогда в приемный цифровой вычислительный блок 3 за перио контроля последовательно поступит следующая комбинация с регистра 8 сдвига: 01...110....О 10...1 гГ 2 1 Скобками выделены разряды комбина ции, указывающие на состояние однойменных усилителей всек каналов. В записи опущены разряды, значение которых равны О. Предлагаемое устройство по сравне нию с известным .позволяет обнаружить факт нарушения работоспособности лини связи в процессе работы, уменьшить время контроля системы и определить расположение неисправных элементов независимо от количества и места одповременно возникших отказов, т.е. точность работы устройства повышаетс Формула изобретения Устройство для контроля системы .передачи дискретных сигналов, содержащее передающий цифровой вычислитель1&ш блок, первые входы которого соединены со входШШ первых, усилителей п-кайальной линх-ш связи, выходы последних ус шителей которой соединены с nepBbiMif входами приемного цифрового вычислительного блока, регистр сдвига, первые входы ячеек которого объединены и соединегл со вторым выходом передающего цифрового вычислительного блока и вторым входом приеьшого цифрового вычислительного блока, выход каждой предыдущей ячейки регистра сдвига соединен со входом послед тощей ячейки, выход последней ячейю регистра сдвига соединен с третьим входом приемного цифрового вычислительного блока, отличающееся тем, что, с целью повьш вния точности устройства, выход приемного цифрового вычислительного блока соединен со входом передающего цифрового вычислительного блока и в каждый канал линии связи введены элементы неравнозначности и элементы ИШ, первый и второй входы каждого элемента неравнозначности соединены соответственно со входом и выходом соответствующего ус1-тителя, выход - с третьим входом соответствующей ячейки регистра сдвига и с первым входом соответствующего элемента ИЛИ, второй вход которого соединен с выходом предыдущего усилителя, а выход, со входом последующего усилителя. Источш1ки информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 576573,.кл. G Об F 11/00, 1975. 2.Авторское свидетельство СССР по заявке № 2640064/18-24, кл. G 08 С 25/00, 1978.

Авторы

Даты

1981-05-15—Публикация

1979-08-01—Подача