Изобретение относится к вычисли- тельной технике передачи информацииj и может быть использовано для отыскания места отказа в линии связи между цифровыми вычислительными устройствами и является усовершенствованием технического решения по авт. ев о № 711610.

Цель изобретения - повьшение точности устройства.

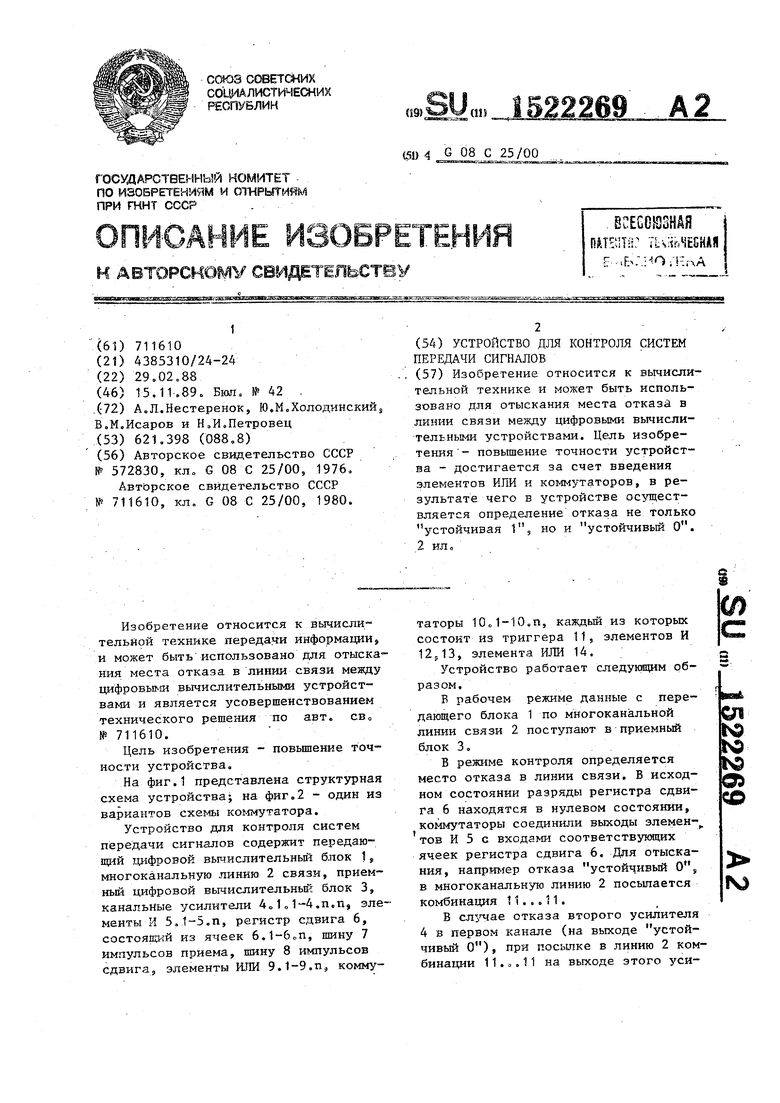

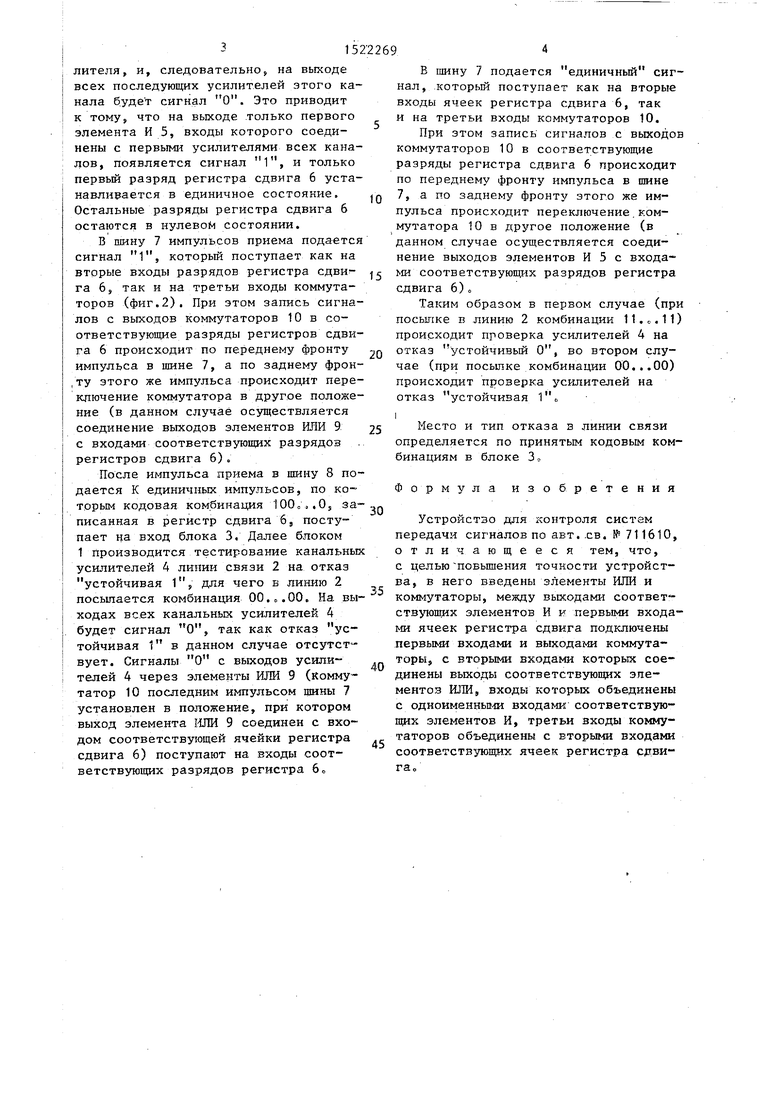

На фиг.1 представлена структурная схема устройства; на фиг.2 - один из вариантов cxej-tt. коммутатора.

Устройство для контроля систем передачи сигналов содержит передающий цифровой вычислительньй блток |, многоканальную линию 2 связи, прием ный цифровой вычислительный блок 3, канальные усилители 4,, 1 „ 1-4,п,п, элементы И 5,1-5,п, регистр сдвига 6, состоящий из ячеек 6.1-6оП, шину 7 импульсов приема, шину 8 импульсов сдвига, элементы ИЛИ 9.1-9.п коммутаторы 10,1-10.п, каждый из которых состоит из триггера 11, элементов И , элемента ИЛИ 14.

Устройство работает следукицим образом.

В рабочем режиме данные с пере дающего блока 1 по многоканальной линии связи 2 поступают в приемный блок 3.

В режиме контроля определяется место отказа в линии связи. В исходном состоянии разряды регистра сдвига 6 находятся в нулевом состоянии, коммутаторы соединили выходы элемен- тов И 5 с входами соответствующих ячеек регистра сдвига 6. Для отыскания, например отказа устойчивый в многоканальную линию 2 посылается комбинация 11... 11.

В отказа второго усилителя 4 в первом канале (на выходе устойчивый О), при посылке в линию 2 комбинации 11.0.11 на выходе этого уси М

лителя, и, следовательно, на выходе всех последующих усилителей этого канала буде т сигнал О. Это приводит к тому, что на выходе только первого элемента И 5, входы которого соединены с первыми усилителями всех каналов, появляется сигнал 1, и только первый разряд регистра сдвига 6 устанавливается в единичное состояние. Остальные разряды регистра сдвига 6 остаются в нулевой состоянии.

В шину 7 импульсов приема подается сигнал 1, который поступает как на вторые входы разрядов регистра сдви га 6, так и на третьи входы коммутаторов (фиг,2). При этом запись сигналов с выходов коммутаторов 10 в соответствующие разряды регистров сдвига 6 происходит по переднему фронту импульса в шине 7, а по заднему фрон- ,ту этого же импульса происходит переключение коммутатора в другое положение (в данном случае осуществляется соединение выходов элементов ИЛИ 9 с входами соответствующих разрядов регистров сдвига 6).

После импульса приема в шину 8 подается К единичных импульсов, по ко- торым кодовая комбинация 100,,.О, записанная в регистр сдвига б, поступает на вход блока 3. Далее блоком 1 производится тестирование канальных усилителей 4 линии связи 2 на отказ устойчивая 1, для чего в линию 2 посыпается комбинация 00..00. На выходах всех канальных усилителей 4 будет сигнал О, так как отказ устойчивая 1 в данном случае отсутствует. Сигналы О с выходов усилителей 4 через элементы ИЛИ 9 (коммутатор 10 последним импульсом щины 7 установлен в положение, при котором выход элемента ИЛИ 9 соединен с вхо дом соответствующей ячейки регистра сдвига 6) поступают на входы соответствующих разрядов регистра 6 о

0

5

Q 5

-

5

0

5

В шину 7 подается единичный сигнал, который поступает как на вторые входы ячеек регистра сдвига 6, так и на третьи входы коммутаторов 10.

При этом запись сигналов с выходов коммутаторов 10 в соответствующие разряды регистра сдвига 6 происходит по переднему фронту импульса в шине 7, а по заднему фронту этого же импульса происходит переключение.коммутатора 10 в другое положение (в данном случае осуществляется соединение выходов элементов И 5 с входами соответствующих разрядов регистра сдвига 6)о

Таким образом в первом случае (при посьшке в линию 2 комбинации 11.0.11) происходит проверка усилителей 4 на отказ устойчивый О, во втором случае (при посылке комбинации 00...00) происходит проверка усилителей на отказ устойчивая 1

I

Место и тип отказа в линии связи

определяется по принятым кодовым комбинациям в блоке Зо

Формула изобретения

Устройство для контроля систем передачи сигналов по авт. .св. № 711610, отличающееся тем, что, с целью повьщ1ения точности устройства, в него введены элементы ИЛИ и коммутаторы, между выходами соответ- ствуюш 1х элементов И и первыми входа™ ми ячеек регистра сдвига подключены первыми входами и выходами коммутаторы, с вторыми входами которых соединены выходы соответствующих элементов ИЛИ, входы которых объединены с одноименнь ми входами соответствующих элементов И, третьи входы коммутаторов объединены с вторыми входами соответствующих ячеек регистра сдвига

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля системы передачи дискретных сигналов | 1980 |

|

SU920813A2 |

| Устройство для контроля систем передачи сигналов | 1978 |

|

SU711610A1 |

| Устройство для контроля системыпЕРЕдАчи диСКРЕТНыХ СигНАлОВ | 1979 |

|

SU830490A1 |

| Измерительная система с автоматическим контролем аналого-цифрового преобразования и блок задания нечувствительности | 1991 |

|

SU1837261A1 |

| Устройство для контроля многоканального аппарата цифровой магнитной записи | 1988 |

|

SU1607011A1 |

| Многоканальная стабилизирующая система электропитания | 1987 |

|

SU1444736A1 |

| Многоканальный цифроаналоговый преобразователь | 1989 |

|

SU1709527A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| Устройство для управления обменом информации процессора с внешними устройствами | 1988 |

|

SU1508223A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037272C1 |

Изобретение относится к вычислительной технике и может быть использовано для отыскания места отказа в линии связи между цифровыми вычислительными устройствами. Цель изобретения - повышение точности устройства - достигается за счет введения элементов ИЛИ и коммутатор, в результате чего в устройстве осуществляется определение отказа не только "устойчивая 1", но и "устойчивый 0". 2 ил.

| Устройство для контроля каналов связи | 1976 |

|

SU572830A1 |

Авторы

Даты

1989-11-15—Публикация

1988-02-29—Подача