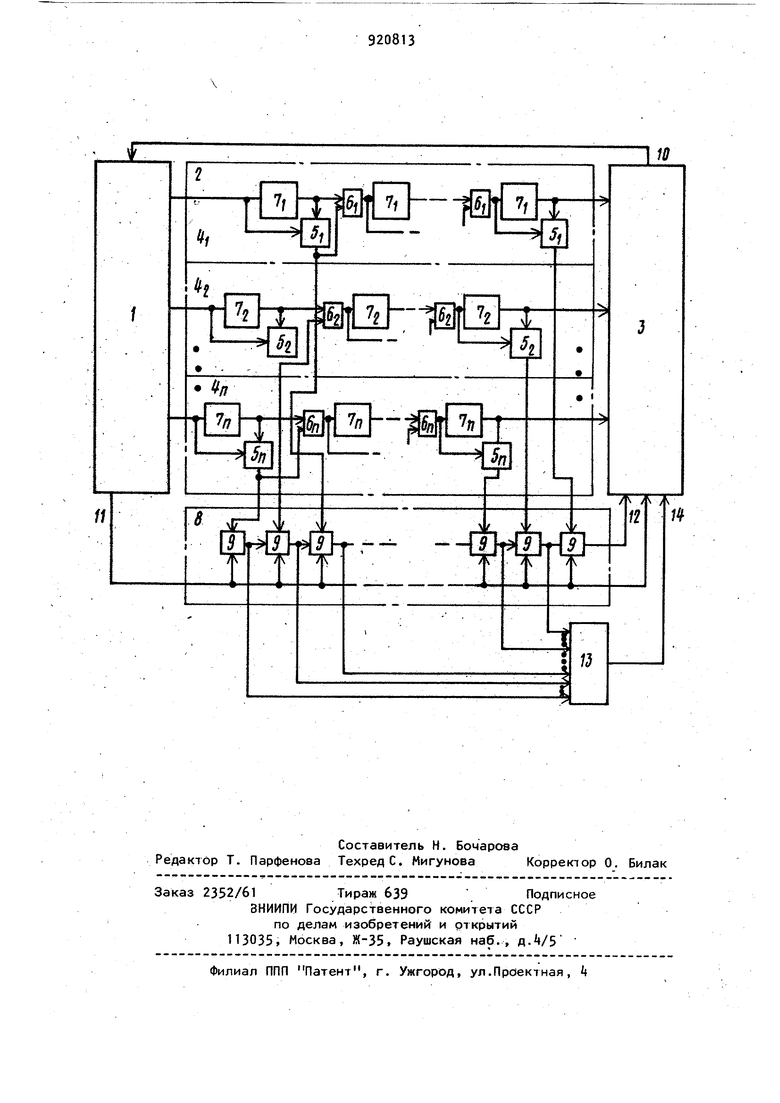

I . Изобретение огносится к вычислительной технике и передаче информации и может быть использовано для отыскания места отказов в линиях ,; связи между цифровыми вычислительными устройствами. По основному авт.св. № . известно устройство для контроля темы передачи дискретных сигналов, . которое содержит передающий цифровой вычислительный блок, первые выходы которого соединены со входами первых усилителей п-канальной линии свя зи, выходы последних усилителей которой соединены с первыми входами приемного цифрового вычислительного блока, регистр сдвига, первые входы ячеек которого объединены и соединены со вторым входом приемного цифров го вычислительного блока, выход каждой предыдущей ячейки регистра сдвига соединен со входом последующей ячейки, выход последней ячейки регистра сдвига соединен с третьим вхр дом приемного, цифрового вычислительного блока, выход приемного цифрового вычислительного блока соединен со входом передающего цифрового вычислительного блока, элементы неравнозначности и элементы ИЛИ, первый и второй входы каждого элемента неравнозначности соединены соответственно со входом и выходом соответствующего усилителя, выход - с третьим входом соответствующей ячейки регистра сдвига и с первым входом соответствующего элемента ИЛИ, второй вход которого соединен с выхо- . дом предыдущего усилителя, а выход со входом последующего усилителя 1. Недостатком этого устройства является то, что оно не позволяетопределить момент появления отказа, а лишь фиксирует факт нарушения работоспособности системы через некоторое время. Кроме того, для выявления .неисправных элементов необходимо обязательно переходить к режиму контроля независимо от количества отказов. Цель изобретения - повышение точ ности и оперативности контроля за счет возножности определения момента возникновения отказа и места однократного отказа без перехода в режим контроля. Поставленная цель достигается гем, что в устройство для контроля системы передачи дискретных сигналов введен многовходовый элемент ИЛИ, выход которого соединен с чётвертым входом приемного цифрового в числительного блока, выходы всех, кроме последней, ячеек регистра сдвига соединены с соответствукхцими входами многовходового элемента ИЛИ. , На чертеже представлена структур ная схема предлагаемого устройства. Устройство содержит передающий .цифровой вычислительный блок 1, пканальную линию 2 связи, приемный цифровой вычислительный блок 3- Каж дый канал содержит элементы неравнозначности (сумматоры по моду лю 2) , элементы ИЛИ и усилители InУстройство также содержит регист 8 сдвига с ячейками 9 управляющую шину 10, шины 11 и 12 импульсов сдв га, многовходовый элемент ИЛИ 13 и шину 1 контроля. Устройство работает следукицим образом. Данные от передающего цифрового вычислительного блока I по многоканальной линии 2 связи поступают в приемный цифровой вычислительный блок 3. При этом постоянно контроли руется работоспособность уси литеяей 7 путем сравнения значений сигналов на входе и на выходе с помощью элементов неравнозначности 5- При отсутствии нарушений в работе линий 2 связи на выходе элементов 5 - низки уровень. В случае нарушения работоспособности усилителя 7 на выходе элемента неравнозначности 5 появляется сигнал высокого уровня, которы обеспечит запись 1 в соответствую щую ячейку 9 регистра 8 сдвига. Импульсы сдвига на регистр 8 по шине 11 поступают с частотой выдачиданных постоянно, поэтому 1 при пода че первого же импульса сдвига посту пает на вход элемента ИЛИ 13 и пере писывается в соседнюю ячейку 9 реги ctpa сдвига 8. С выхода элемента ИЛИ 13 единичный сигнал поступает по шине Н на вход приемного цифрового вычислительного блока 3 и обеспечивавает фиксацию момента появления отказа в линии 2. Единица, записанная в соседнюю ячейку регистра 8 сдвига, под воздействием импульсов сдвига продвигается по регистру 8 и затем по шине 12 поступает в приемный вычислительный блок 3 через время, определяемое количеством импульсов сдвига, необходимым для выдачи 1 на выход регистра 8. Таким образом, фиксируя момент возникновения отказа по сигналу, поступившему с элемента ИЛИ 13 по шине И, и определив количество тактов, необходимое для сдвига 1 на выход регистра 8, можно однозначно установить номер ячейки 9 регистра 8 сдвига, определить отказавший усилитель 7, не переводя устройство в режим контроля. 4 отказал Например, если в канале последний усилитель 7, то с выхода ссютветствующего ему элемента неравнозначности 5 единичный сигнал поступает на п-ю справа ячейку 9 регистра сдвига 8. При поступлении импульса сдвига по шине 11 1 поступает через элемент ИЛИ 13 по шине 1 на вход блока 3 и, кроме того, сдвигается в соседнюю ячейку регистра 8. Начиная с с этого момента в блоке 3 производится подсчет импульсов сдвига до момента появления.1 на шине 12. В данном Случае она появляется на входе блока 3 после подачи еще (п-1) импульса сдвига. Следовательно, первоначально единица была записана в ту ячейку 9.регистра сдвига 8, для сдвига 1 из которой на выход регистра потребовалось (п-1) импульсов сдвига, т.е. в п-ю справа ячейку. А этой ячейке однозначно соот тствует последний усилитель 7„ +, канала. Для обнаружения нескольких, одновременно возникших, отказов следует перейти к режиму контроля, поскольку в худшем -случае от элемента неравнозначности 5 подключенного к неисправному усилителю 7 (в примере это последний усилитель 4 канала), в каждом такте передачи данных поступает высокий уровень в соответствующую ячейку 9 регистра 8 сдвига, чт,о делает возможным выявление других, одновременно отказавших, усилитеВ режим конт1эоля, если это необхо димо, т.е. велика вероятность нескольких одновременных отказов, устройство переходит по управляющему сигна лу, подаваемому в блок 1 по шине 10, после прихода в блок 3 первой Ле еди ницы по шине 12. В режиме контроля определяются места отказов. В исходном состоянии все ячейки 9 регистра 8 сдвига обнулены. Для отыскания отказов, нап ример, наиболее часто встречающихся типа Устойчивый О, блок 1 посылает в линию 2 связи комбинацию 11-11. Элементы 5 Подключенное к отказавшим усилителям 7, формируют единичнь сигналы, которые заносят 1 в соответствующие ячейки 9 регистра 8 сдвига. Затем блок 1 выдает серию импульсов сдвига по шине 11, обеспечивающих последовательную передачу содер жимого всех ячеек 9 регистра В сдвига по шине 12 в блок 3 для анализа. Предположим, что в первом кан§1ле 4. отказали первые два усилителя 7, во BiopoM - последний усилитель, а в последнем канале k - первый и последний усилители. Тогда в блок 3 за период кон1роля последовательно поступит по шине 12 следующая комбинация сигналов: 01-1 - .10-0 п Т Скобками выделены разряды комбинации , указывающие на состояние одноименных усилителей 7 всех п каналов. В записи опущены разряды, значения которых равны О. Таким образом, предлагаемое устройство по сравнению с известным позволяет не только обнаружить факт нарушения рг отоспособности, но и зафиксировать момент нарушения, т.е. момент качала приема искаженной информации, что повышает точность контроля. Кроме того, предлагаемое устройство позволяет определить неисправностный элемент при однократномг отказе без прохода в режим контроля, что повышает оперативность контроля . Формула изобретения Устройство для контроля системы передачи дискретных сигналов по авт.св. № , отличающееся тем, что, с целью повышения точности и оперативности контроля , в устройство введен многовходовый элемент ИЛИ, выход которого соединен с четвертым входом приемного цифрового вычислительного блока, выходы всех, кроме последней, ячеек регистра сдвига соединены с соответствующими входами многовходового элемента ИЛИ. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № , кл. G 08 С 25/00, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля системыпЕРЕдАчи диСКРЕТНыХ СигНАлОВ | 1979 |

|

SU830490A1 |

| Устройство для контроля систем передачи сигналов | 1978 |

|

SU711610A1 |

| Устройство для контроля систем передачи сигналов | 1988 |

|

SU1522269A2 |

| Адаптивный восстанавливающий орган | 1984 |

|

SU1292216A1 |

| Резервированная система | 1988 |

|

SU1584137A1 |

| Устройство для ввода-вывода информации | 1989 |

|

SU1615694A2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386442A1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1990 |

|

SU1795520A1 |

| Адаптивное вычислительное устройство | 1977 |

|

SU734679A1 |

| Генератор псевдослучайных чисел | 1980 |

|

SU935951A1 |

Авторы

Даты

1982-04-15—Публикация

1980-05-05—Подача