1

Изобретение относится к импульсной технике и может быть использовано в распределителях импульсов и кодирующих устройствах.

Известен распределитель импульсов, содержащий двоичный счетчик, импульсов и выходные ячейки. Каждая ячейка представляет собой дешифратор, число входоь которого зависит от количества триггеров в двоичном счетчике. Число триггеров определяется требуемым количеством каналов устройства 1 .

Недостатками этого устройства являются наличие кратковременных ложных включений каналов устройства, а также сложность схемы, зависимость числа входов каждого дешифратора от количества выходов всего устройства, что обусловлено принципом его построения.

Известен также распределитель импульсов, содержащий N-разрядный двоичный счетчик и однотипные выходные ячейки, каждая из которых выполнена на логическом элементе И, рассчитанном на соответствующую комбинацию входных сигналов. В общем случае дешифратор содержит 2 N-BXOдовых элементов И. Кроме того, для исключения возможности кратковременного ложного включения каналов каждый логический элемент И снабжен дополнительным входом, на который подаются тактовые импульсы 2.

Недостатком данного устройства является невысокая достоверность, так как оно итиеет неопределенные состояния, когда на всех его выходах отсутствуют выходные сигналы (длительность этих неопределенных состояний достигает половины длительности выходных импульсов, кроме этого, время формирования выходных импульсов на выходах распределителя задержано на 1/2 Тех, на такую же величину, т. е. вдвое уменьшена и их длительность), и невысокая надежность, что обусловлено сложностью и большим числом взаимосвязей между двоичным счетчиком и дешифратором распределителя.

Цель изобретения - повышение надежности и достоверности.

Поставленная цепь достигается тем, что

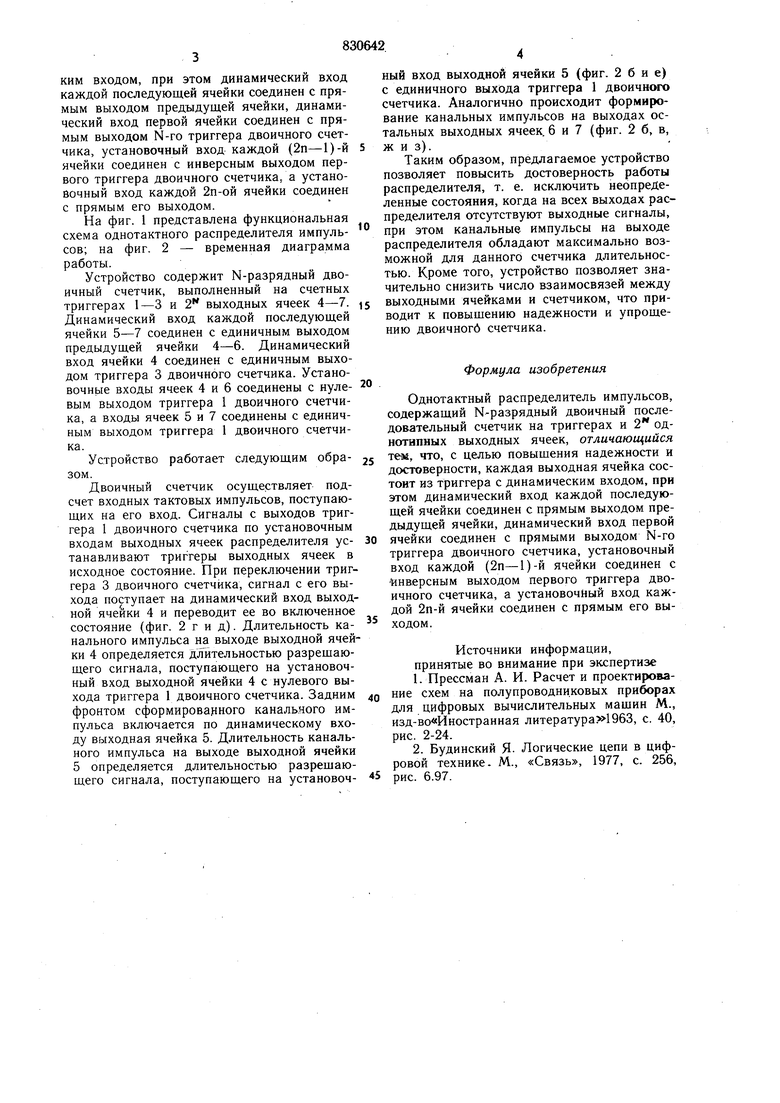

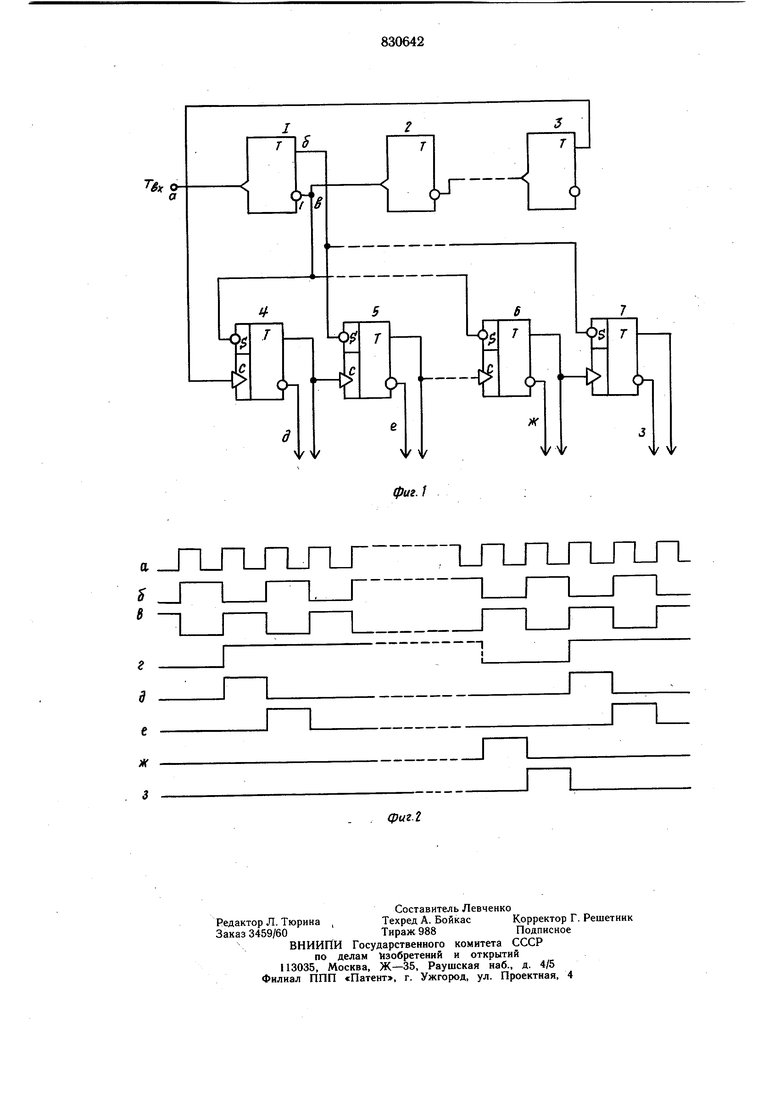

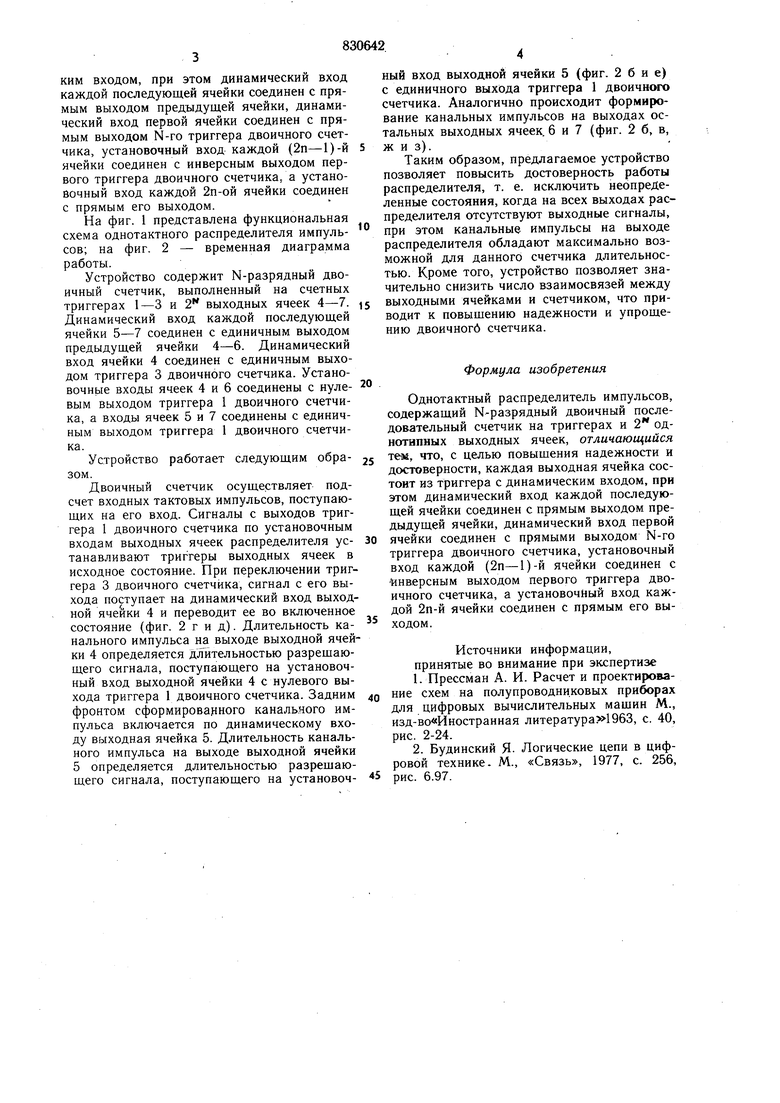

.в однотактном распределителе импульсов, содержащем N-разрядный двоичный последовательный счетчик на триггерах и однотипных выходных ячеек, каждая выходная ячейка состоит из триггера с динамичесКИМ входом, при этом динамический вход каждой последующей ячейки соединен с прямым выходом предыдущей ячейки, динамический вход первой ячейки соединен с прямым выходом 4-гo триггера двоичного счетчика, установочный вход каждой (2п-1)-й ячейки соединен с инверсным выходом первого триггера двоичного счетчика, а установочный вход каждой 2п-ой ячейки соединен с прямым его выходом. На фиг. 1 представлена функциональная схема однотактного распределителя импульсов; на фиг. 2 - временная диаграмма работы. Устройство содержит N-разрядный двоичный счетчик, выполненный на счетных триггерах 1-3 и 2 выходных ячеек 4-7. Динамический вход каждой последующей ячейки 5-7 соединен с единичным выходом предыдущей ячейки 4-6. Динамический вход ячейки 4 соединен с единичным выходом триггера 3 двоичного счетчика. Установочньге входы ячеек 4 и 6 соединены с нулевым выходом триггера 1 двоичного счетчика, а входы ячеек 5 и 7 соединены с единичным выходом триггера 1 двоичного счетчика. Устройство работает следующим образом. Двоичный счетчик осуществляет подсчет входных тактовых импульсов, поступающих на его вход. Сигналы с выходов триггера 1 двоичного счетчика по установочным входам выходных ячеек распределителя устанавливают триггеры выходных ячеек в исходное состояние. При переключении триггера 3 двоичного счетчика, сигнал с его выхода поступает на динамический вход выходной ячейки 4 и переводит ее во включенное состояние (фиг. 2 г и д). Длительность канального импульса на выходе выходной ячейки 4 определяется Дл ительностью разрешающего сигнала, поступающего на установочный вход выходной ячейки 4 с нулевого выхода триггера 1 двоичного счетчика. Задним фронтом сформированного канального импульса включается по динамическому входу выходная ячейка 5. Длительность канального импульса на выходе выходной ячейки 5 определяется длительностью разрешающего сигнала, поступающего на установочный ВХОД ВЫХОДНОЙ ячейки 5 (фиг. 2 б и е) с единичного выхода триггера 1 двоичного счетчика. Аналогично происходит формирование канальных импульсов на выходах остальных выходных ячеек, б и 7 (фиг. 2 б, в, ж и з). Таким образом, предлагаемое устройство позволяет повысить достоверность работы распределителя, т. е. исключить неопределенные состояния, когда на всех выходах распределителя отсутствуют выходные сигналы, при этом канальные импульсы на выходе распределителя обладают максимально возможной для данного счетчика длительностью. Кроме того, устройство позволяет значительно снизить число взаимосвязей между выходными ячейками и счетчиком, что приводит к повышению надежности и упрощению двоичногб счетчика. Формула изобретения Однотактный распределитель импульсов, содержащий N-разрядный двоичный последовательный счетчик на триггерах и 2 однотипных выходных ячеек, отличающийся тем, что, с целью повышения надежности и достоверности, каждая выходная ячейка состоит из триггера с динамическим входом, при этом динамический вход каждой последующей ячейки соединен с прямым выходом предыдущей ячейки, динамический вход первой ячейки соединен с прямыми выходом N-ro триггера двоичного счетчика, установочный вход каждой (2п-1)-й ячейки соединен с инверсным выходом первого триггера двоичного счетчика, а установочный вход каждой 2п-й ячейки соединен с прямым его выходом. Источники информации, принятые во внимание при экспертизе 1.Прессман А. И. Расчет и проектирование схем на полупроводниковых приборах для цифровых вычислительных машин М., изд-во«Иностранная литература 1963, с. 40, рис. 2-24. 2.Будинский Я. Логические цепи в цифровой технике. М., «Связь, 1977, с. 256, рис. 6.97.

, фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-регулируемый электропривод с широтно-импульсной модуляцией | 1982 |

|

SU1310987A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1983 |

|

SU1111140A1 |

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

| Распределитель | 1979 |

|

SU830359A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

| Коммутирующее устройство | 1982 |

|

SU1078614A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| ЛИНИЯ ЗАДЕРЖКИ | 1996 |

|

RU2100900C1 |

Авторы

Даты

1981-05-15—Публикация

1979-06-12—Подача