Изобретение о,тносится к вычислительной технике и может быть использовано в импульсной технике и устройствах автоматики Б качестве временного распределителя или адресного счетчика с дешифратором гщреса.

-Известен распределитель на основе сдвигающего регистра, в котором сдвигается унитарный код, содержащий одну единицу, которая последовательно проходит разряды 1, 2 ... Г1Х

Однако такой распределитель требует больших аппаратных затрат, так как число триггеров в нем равно, где п - число выходов распределите- ля.

Наиболее близким к предлагаемому по технической сущности является распределитель, содержащий двоичный счетчик и дешифратор. Счетчик последовательно переключается в состояния 0,1,2, ..., 2 -1 Г2,

Недостатком такого распределителя является возможность ложных срабатываний дешифратора.

Цель изобретения - устранение ложных срабатываний дешифратора распределителя без ограничения длительност его выходных сигналов стробирующим

импульсом, т.е. повышение надежности распределителя.

Указанная цель достигается тем, что распределитель, содержащий п-разрядный счетчик и дешифратор, имеющий 2п выходов, импульсный вход распределителя подключен к счетному входу первого разряда счетчика, имеет п-1 триггеров, причем выход каждого разряда счетчика, кроме последнего, соединен со счетным входом соответствующего триггера, а инверсные и прямые выходы п-1 триггеров и последнегоп-го разряда счетчика соединены со входами дешифратора.

Такой распределитель содержит int log N триггеров счетчика и (intlog N)-1 вспомогательных триггеров, т.е. всего содержит (2 Intlog N)-1 триггеров, где N - число выходов дешифратора.

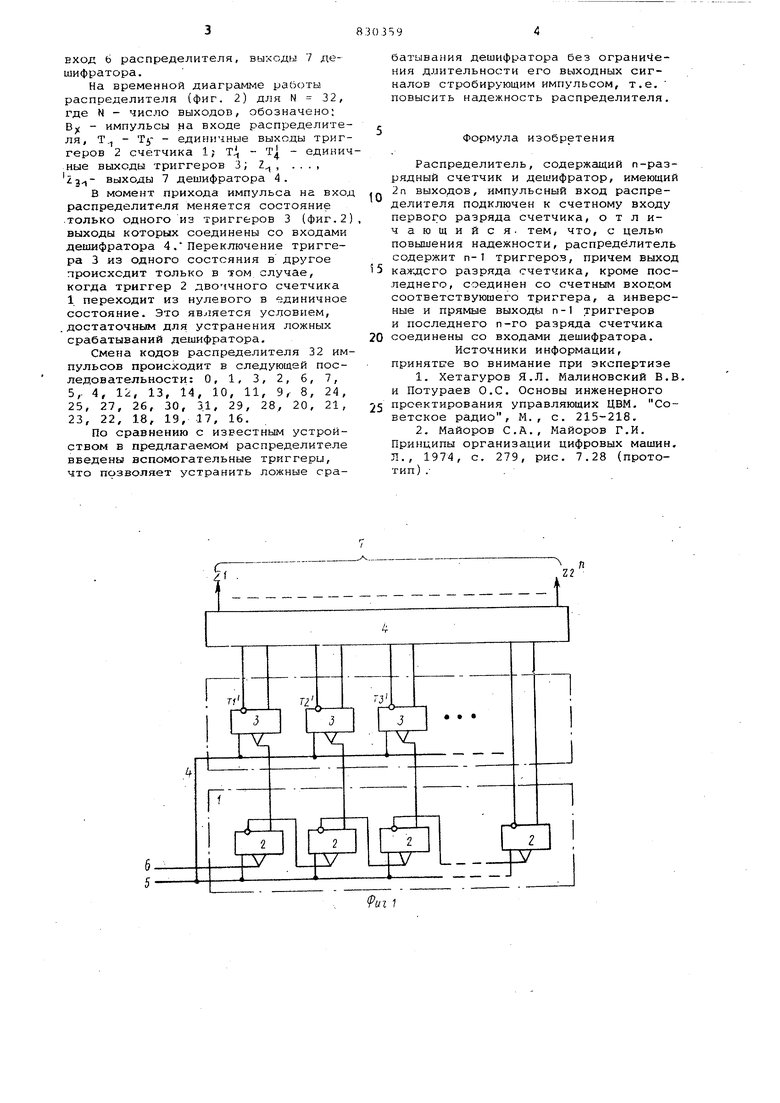

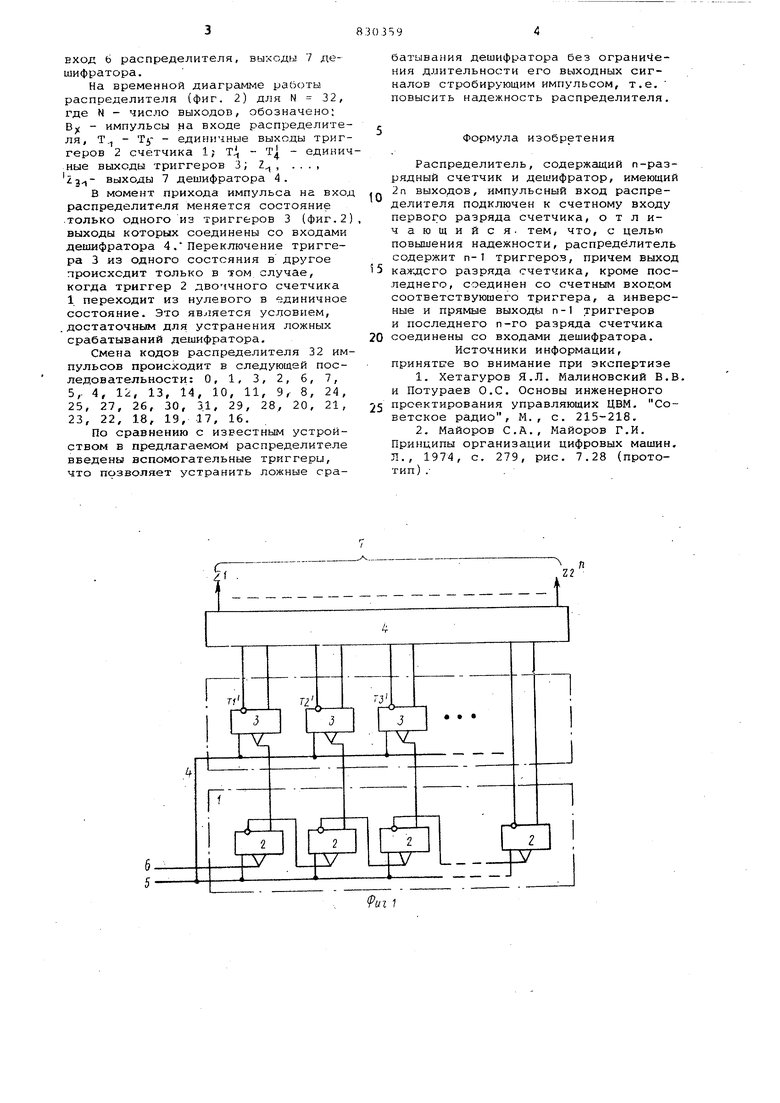

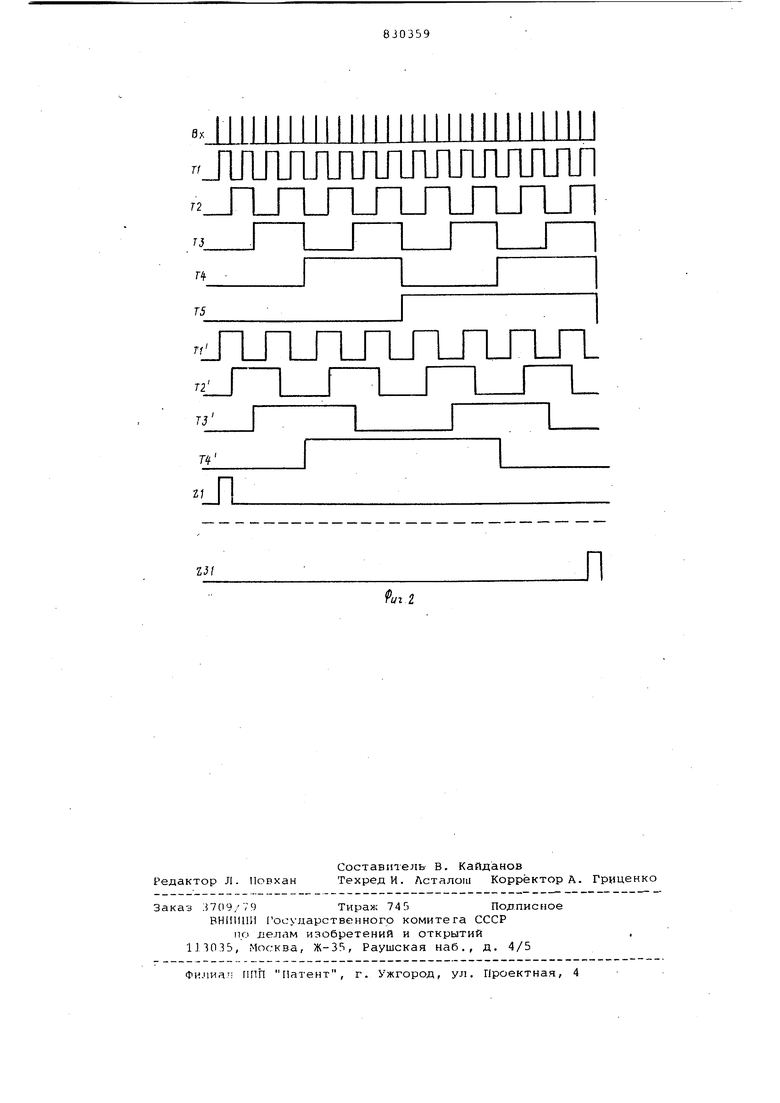

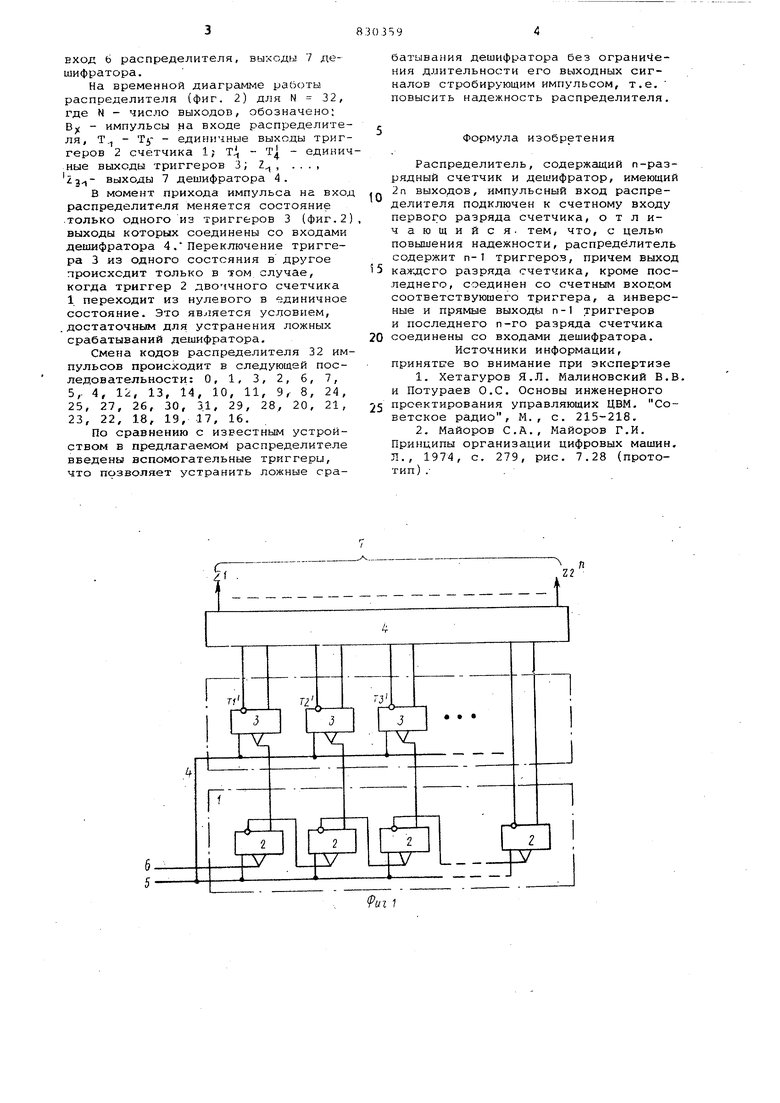

На фиг. 1 изображена схема распределителя; на фиг. 2 - временная диаграмма распределителя.

Схема распределителя содержит двоичный счетчик 1, содержащий в каж- . дом разряде триггер 2, триггер 3, дешифратор 4, вход начальной установки О распределителя 5, импульсный

Еход ь распределителя, выходы 7 дешифратора.

На временной диаграмме работы распределителя (фиг. 2) для N 32, где N - число выходов, обозначено; Bj( - импульсы на входе распределителя, Т., - Ti,- - единичные выходы триггеров 2 счетчика 1; Tj, - т| - едининые выходы триггеров 3; 2, ..., выходы 7 дешифратора 4.

В момент прихода импульса на вхо распределителя меняется состояние только одного из триггеров 3 (фиг.2 выходы которых соединены со входами дешифратора 4.Переключение триггера 3 из одного состояния в другое происходит только в том случае, когда триггер 2 двоччного счетчика 1 переходит из нулевого в единичное состояние. Это является условием, .достаточным для устранения ложных срабатываний дешифратора.

Смена кодов распределителя 32 импульсов происходит в следующей последовательности: О, 1, 3, 2, б, 7, 5,. 4, Ik, 13, 14, 10, 11, 9, 8, 24, 25, 27, 26, 30, ЗД, 29, 28, 20, 21, 23, 22, 18, 19, 17, 16.

По сравнению с известным устройством в предлагаемом распределителе введены вспомогательные триггеры, что позволяет устранить ложные срабатывания дешифратора без ограничения длительности его выходных сигналов стробирующим импульсом, т.е. повысить надежность распределителя.

Формула изобретения

Распределитель, содержащий п-разрядный счетчик и дешифратор, имеющий

Q 2п выходов, импульсный вход распределителя подключен к счетному входу первого разряда счетчика, отличающийся, тем, что, с целью повышения надежности, распределитель содержит п-1 триггеров, причем выход

J каждого разряда счетчика, кроме последнего, соединен со счетным входом соответствующего триггера, а инверсные и прямые выходы п-1 триггеров и последнего п-го разряда счетчика 0 соединены со входеиии дешифратора.

Источники информации, принятое во внимание при экспертизе

1.Хетагуров Я.Л. Малиновский В.В. и Потураев О.С. Основы инженерного

5 проектирования управляющих ЦВМ. Советское радио, М., с. 215-218.

2.Майоров С.Д., Майоров Г.И. Принципы организации цифровых машин, Л., 1974, с. 279, рис. 7.28 (прототип) .

шишшшшшжшл

Т

| название | год | авторы | номер документа |

|---|---|---|---|

| Однотактный распределитель импульсов | 1979 |

|

SU830642A1 |

| Устройство для управления @ -фазным автономным инвертором напряжения | 1983 |

|

SU1089753A1 |

| Устройство для цифрового управления тиристорным регулятором | 1990 |

|

SU1744774A1 |

| Устройство для цифрового управления тиристорным регулятором | 1980 |

|

SU860266A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для контроля и сигнализации | 1990 |

|

SU1795494A1 |

| Устройство для контроля электронных устройств | 1984 |

|

SU1231505A1 |

| Устройство для приема команд телеуправления | 1984 |

|

SU1229791A1 |

| Недвоичный синхронный счетчик | 1990 |

|

SU1742994A1 |

| Генератор псевдослучайных последовательностей | 1990 |

|

SU1758851A2 |

Г Т5

Г1 Т 2

г,Л

ZJf

Авторы

Даты

1981-05-15—Публикация

1979-07-18—Подача