(54) ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайных процессов | 1981 |

|

SU985786A1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Многоканальное устройство для обработки информации датчиков с частотным выходом | 1984 |

|

SU1196892A1 |

| Синусно-косинусный функциональный преобразователь | 1980 |

|

SU888111A1 |

| Устройство для трассировки межсоединений | 1984 |

|

SU1208560A1 |

| Цифровой согласованный фильтр для импульсных эхо-сигналов | 1981 |

|

SU964979A1 |

| Устройство для вычисления уровня жидких сред | 1984 |

|

SU1251101A1 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1988 |

|

SU1541663A1 |

1

Изобретение относится к области вычислительной техники и предназ начается для использования в вычислительных устройствах различного назначения, в частности в специализированных вычислительных устройствах

Известен цифровой генё1)атор функций, содержащий преобразователь временного интервала в последователь ность импульсов, блок весовых коэффициентов, выходной счетчик регистр, блок декодирования и блок памяти, вход преобразователя временного интервала соединен со входом генератор а выход подключен через блок весовых коэффициентов к первому входу выходного счетчика-регистра,входы которого соединены с клеммами ввода начального значения кода функции,а - выходы выходного счетчика-регистра подключены через последовательно соединенные блок декодирования и блок пгиляти к соответствующей группе входов блока весовых коэффициентов, причем второй вход выходного счетчика.-регистра соединен с дополнительными выходами блока памяти l.

Недостатки устройства - ограниченная точность и невозможность

воспрЬиэведения немонотонных функций.

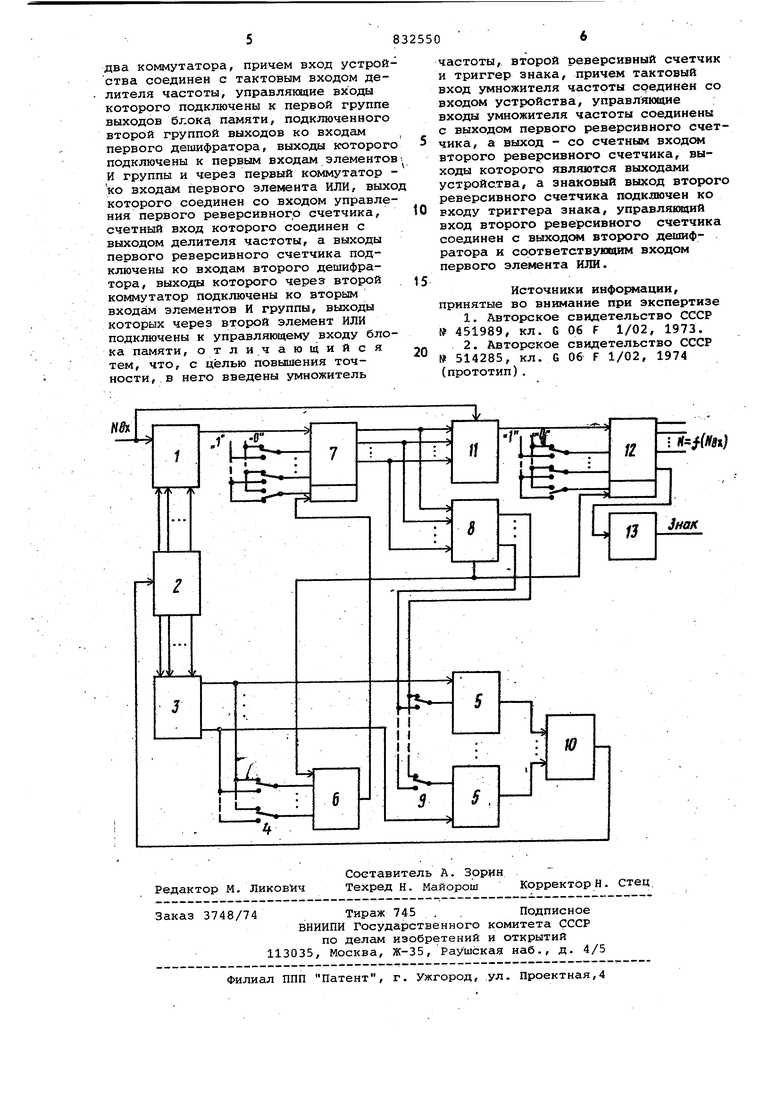

Наиболее близким по технической сущности к предлагаемому является цифровой функциональный преобразователь, содержащий делитель частоты, блок памяти, первый и второй дешифраторы, первый реверсивный счетчик, группу элементов И, два элемента ИЛИ два колочутатора, причем вход устройства соединен с тактовым входом делителя частоты, управляющие входы которого подключены к первой группе выходов блока памяти, подключенного второй группой выходов ко входам первого дешифратора,выходы которого подключены к первым входам элементов И группы и через первый коммутатор - ко входам первого элемента ИЛИ, выход которого соединен со входом управления первого реверсивного счетчика, счетный вход которого соединен с выходом делителя частоты, а выходы первого реверсивного счетчика подключены ко входам второго дешифратора,. выходы которого через второй коммутатор подключены ко вторым входам элементов и группы, выходы которых через второй элемент ИЛИ подключены к управляющему входу блока памяти 2. Однако описанный цифровой функциональный преобразователь обладает ограниченной точностью аппроксимации функции, так. как она производится отрезками полинома первой степени () Цель изобретения - повышение точности генерируемых функций. С этой целью в цифровой функциональ-ный генератор дополнительно введены умножитель частоты, второй реверсивный счетчик и триггер знака, причем тактовый вход умножителя частоты соединен со входом устройст ва, управляющие входы умножителя частоты соединены с выходом первого реверсивного счетчика, а выход - с счетным входом второго реверсивного счетчика, выходы которого являются выходами, устройства, а знаковый выход второго реверсивного счетчика подключен- ко входу триггера знака, управляющий вход второго реверсивного счетчика соединен с-выходом второго дешифратора и соответствующ входом первого элемента ИЛИ, На чертеже представлена блок-схе устройства. Устройство содержит делитель 1 частоты, блок 2 памяти, первый деши ратор 3, первый коммутатор 4, групп элементов И 5, первый элемент ИЛИ 6 первый реверсивный счетчик 7, второ дешифратор 8, второй коммутатор 9, второй элемент ИЛИ 10, у ножитель 1 частоты, второй реверсивный счетчик 12, триггер 13 знака. Устройство работает следующим образом. Перед началом преобразования на счетчиках записываются начальные ус ловия. Со входа устройства на такто вый вход управляемого делителя 1 частоты подаются входные импульсы.П этом коэффициент пересчета делителя зависит от состояния блока 2 памяти и при его начальном состоянии равен К1. После пересчета на коэффициент К1 импульсы подаются на вход счетчика 7, который в зависимости от кода, записанного в триггере реверса, работает на сложение или вычита ние . Двоичный код с выхода реверсивно го счетчика 7 управляет умножителем 11 частоты, на тактовый вход умножителя частоты поступают входные импульсы. Выходные импульсы умножителя час тоты следуют с частотой, прямо про-. порциональной коду управления.Выходные импульсы постудаиот на тактовый вход реверсивного счетчика 12, . работающего на сложение или вычитание. Выходной код счетчика 12 предтавляет алгебраическую сумму чиса выходных импульсов умножителя астоты и прямо пропорционален инегралу от выходного кода счетчика 7 по времени. Таким образом, на умножителе 11 частоты и реверсивном счетчике 12 осуществляется интегрирование кода, вырабатываемого счетчикс)М 7, и аппроксимация участка функции производится отрезком полинома второй степени. При достижении кода, соответствующего первой точке перегиба, на соответствующих выходах дешифратора 8 появляется код, который через переключатели поступает на элементы И 5. Сигналы с логических элементов И 5 собираются вторыз элементом Или 10 и переключают блок 2 памяти в новое состояние. При этом с его выхода поступает новый код, соответствующий коэффициенту пересчета входных импульсов для следующего участка. Дальнейшие переходы от одного линейного участка,производной к другому осуществляются аналогично. В случае, когда в точке излома производной меняется и ее знак код с первого дешифратора 3 выбирается коммутатором 4 и проходит на первый.элемент ИЛИ 6 и переключает первый реверсивный счетчик 7. При переходе кода прюизвбдной через ноль с выхода дешифратора снимается сигнал, поступающий на первый элемент ИЛИ б и так же, как в предьщущем случае, на вход реверсивного счетчика 12. При этом реверсируются оба реверсивных счетчика 7 и 12. , - . : Производная получается в прямом коде, а функция - в дополнительном коде. Триггер 13 знака служит для индикации знака функции и переключается при прохождении кода функции через ноль. Таким образом, аппроксимация функций производится полиномом второго порядка S (с1 -D-I х + . что позволяет повысить точность генерируемых функциональным генератором функций. Предлагаемый функциональный генератор воспроизводит код соответствующий первой производной функции, который воспроизводится на первом реверсивном счетчике. Формула изобретения Цифровой функциональный генератор, содержащий делитель частоты, блок памяти, первый и второй дешифраторы, первый реверсивный счетчик, группу элементов И, два элемента ИЛИ,

два коммутатора, причем вход устройства соединен с тактовым входом делителя частоты, управляющие входы которого подключены к первой группе выходов блока памяти, подключенного второй группой выходов ко входам первого дешифратора, выходы которого подключены к первым входам элементов И группы и через первый коммутатор ко входам первого элемента ИЛИ, выхо которого соединен со входом управления первого реверсивного счетчика, счетный вход которого соединен с выходом делителя частоты, а выходы первого реверсивного счетчика подключены ко входам второго дешифратора, выходда которого через второй коммутатор подключены ко вторым входам элементов И группы, выходы которых через второй элемент ИЛИ подключены к управляющему входу блока памяти, отличающийс я тем, что, с целью повышения точности, в него введены умножитель

частоты, второй реверсивный счетчик и триггер знака, причем тактовый вход умножителя частоты соединен со входом устройства, управляющие входы умножителя частоты соединены с выходом первого реверсивного счетчика, а выход - со счетным входе второго реверсивного счетчика, выходы которого являются выходами устройства, а знаковый выход второго реверсивного счетчика подключен ко

o входу триггера знака, управлякхций вход второго реверсивного счетчика соединен с выходом второго дешифратора и соответствующим входом первого элемента ИЛИ.

5

Источники инфо ялации, принятые во внимание при экспертизе

0 № 514285, кл. G 06 F 1/02, 1974 (прототип).

Авторы

Даты

1981-05-23—Публикация

1979-03-02—Подача