(54) СИНУСНО-КОСИНУСНЫЙ ФУНКЦИОНАЛЬНЫЙ

1

Изобретение относится к вычисли тельной технике, в частности, к устройствам формирования радиально-круговой развертки.

Известен функциональный преобразователь 1, содержащий приемный регистр, старшие разряды которого подключены к входным шинам схемы декодирования с присоединенной к ее выходу схемой памяти, делительный . счетчик, соединенный управляющими входами с выходами схемы памяти, которые подключены к управляющему и установочным входам реверсивного регистра, и преобразователь параллельного кода,в последовательность импульсов. Входные шины преобразователя параллельного кода в последовательность импульсов присоединены к младшим разрядам приемного регистра, а его выход подключен к счетному входу делительного счетчика, выход которого соединен со счетным входом реверсивного регистра.

Недостатком известного устройства является невозможность формирования двух функциональных зависимостей одновременно, а также большой объем используемой аппаратуры. ПРЕОБРАЗОВАТЕЛЬ

Наиболее близок к предлагаемому аинусно-косинусный функциональный лреобразователь 2, содержащий датчик прямого и инвертированного кода, два коммутатора кодов/ два преобразователя код-временной интервал , подключенные к выходам счетчиков аргумента, дешифратор , подключенный к выходам старших разря10дов, счетчика аргументГа,, постоянное запоминающее устройство, подключенное к выходам дешифратора, множительное устройство, подключенное к выходам постоянного запоминающего устройства и выходам младший разрядов счетчика аргумента, элементы И, одни входы которых подключены к выходу множительного устройства, а другие через триггеры - к преобразова20

телям код-временной интервал .

Недостатком описанного функционального преобразователя является неравномерное распределение во времени выходных импульсов. Количество

25 импульсов, поступающих на выходы описанного преобразователя, определяется кодом, считанным из запоминающего устройства, входы которого через дешифратор подключены к выхо30дам счетчика. Содержимое счетчика в

процессе вычисления синуса и косин са угла изменяется от О до тех пор, пока записанное в счетчике число не станет равным величине угла. Следствием изменения состояния счетчика в процессе функционального преобразования является то, что за однаковые интервалы времени на один и тот же выход поступает разное количество импульсов.

Целью изобретения является получение равномерного распределения во времени выходных импульсов функционального преобразования, что повы- шает быстродействие преобразователя.

Поставленная цель достигается тем, что в функциональный преобразователь, содержащий регистр угла, коммутатор, элементы И, триггеры, входной счетчик, первый умножитель канала синуса и блок памяти, выход синуса которого соединен с первым входом первого умножителя канала синуса, второй вход которого соединен с выходом входного счетчика, дополнительно введены два канала, причем в первый канал введены делитель импульсов, счетчик, второй умножитель и элемент ИЛИ, во второй канал введены два умножителя, .делитель импульсов, счетчик и элемент ИЛИ, в каждом канале выходы первых умножителей через соответствующие делители импульсов подключены к входам счетчиков , выходы которых соединены с первыми входами вторых умножителей, выходы которых соединены с первыми входами триггеров, выходы которых подключены к первым входам элементов ИЛИ. Выходы элементов ИЛИ каждого канала соединены соответственно с первым и вторвлм входами коммутатора, управляющий вход которого подключен к выходу одиннадцатого разряда регистра угла, выходы разрядов с седьмого по десятый которого подключены к входам блока памяти, выход косинуса которого соединен с первым входом первого умножителя второго канала, второй вход которого подключен к выходу входного счетчика. Выходы умножителей каждого канала подключе.. ны ко вторым входам элементов И и ИЛ другого канала. Прямые и инверсные выходы с Первого по шестой разрядов регистра угла подключены ко вторым входа 4 соответственного второго умножителя первого канала и второго умножи|еля второго канала. Третьи входы элементов И каждого канала чсоединeны c тактовым входом преобразователя и счетным входом входного счетчика, выходы элементов И каждого канала соединены со вторыми входами триггеров тех же каналов, выходы коммутатора являются выходами преобрагзователя.

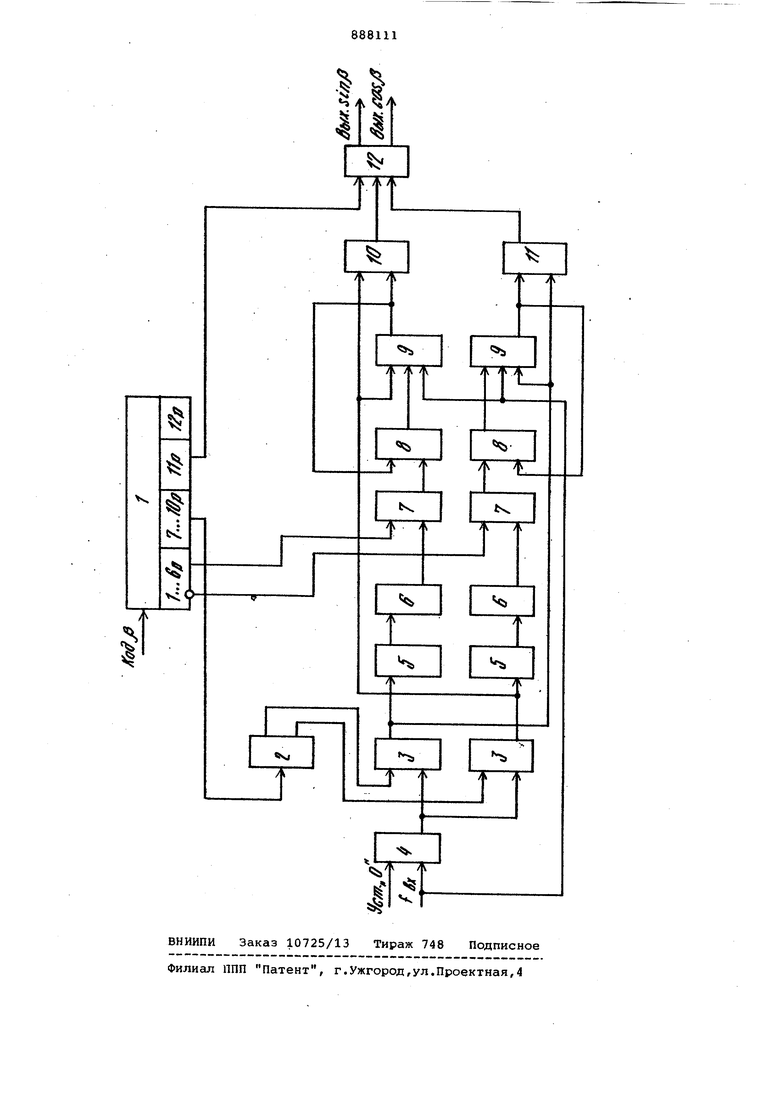

Блок-схема преобразователя представлена на чертеже.

Преобразователь содержит регистр 1 .угла, блок 2 памяти, умножители 3, входной счетчик 4, делители импульсов 5, счетчики 6, умножители 7, триггеры 8, элементы И 9, элементы ИЛИ 10 и 11, коммутатор 12.

Преобразователь работает следующим образом.

Код угла вводится в регистр угла 1. Из блока 2 считываются начальные значения косинуса и синуса угла, соответствующие одному из 16 участ-. ков, на которые разбиты функциональные зависимости. К выходам блока 2 подключены одни входы умножителей 3, вторые входы которых объединены и подсоединены к выходу двоичного счетчика 4, на вход которого во время преобразования поступгиот импульсы. С выходов умножителей 3 импульсы поступают на входы элементов И 9, ИЛИ 10, 11 и входы делителей импульс®в 5. С выходов делителей 5 импульсы поступают на входы счетчиков б, к выходам которых подключены входы умножителей 7.

Вторые входы умножителей подключены соответственно к прямым и инверсным выходамс первого по шестой разрядов, регистра угла 1. С помощью дёлителейз ; импульсов 5, счетчиков б и умножителей 7 вычисляются значения функций с учетом младших разрядов кода угла. Триггеры 8 и элементы И 9 предотвращают наложение импульсов, поступающих на выходы умножителей 3 и 7. Триггеры 8 после поступления на них импульсов с выходов умножителей 7 разрешают прохождение импульсов на выходы элементов И 9 и возвращаются этими же импульсами в исходное положение, запрещая прохождение импульсов на выходы элементов И 9 до поступления следующих импульсов на выходы умножителей 7.

Импульсы с выходов элементов И 9 поступают на входы элементов ИЛИ 10, 11, на вторые входы которых поступают импульсыс выходов умножителей 3. Эти же импульсы возвращают прохождение импульсов на выходы элементов И 9. Таким образом, предотвращается одновременное поступление импульсов на оба входа элементов ИЛИ 10, 11. С выходов элементов ИЛИ 10, 11 импульсы поступают на входы коммутатора 12, управляющий вход которого подключен к выходу одиннадцатого разряда регистра 1 угла. При нулевом состоянии одиннадцатого разряда регистра 1 угла на выход sin устройства поступают импульсы с выхода элемента ИЛИ 10, а на выход cos fb 0 с выхода элемента ИЛИ 11. При единичном состоянии одиннадцатого разряда на выход sin |% поступают импульсы с выхода элемента ИЛИ 11, а на выход сов ft - с выхода элемента 5 или 10. Делители импульсов 5 служат для веса младших разряуравниваниядов умножителей 3, 7. При 10-разрядном входном счетчике 4 и умножителях 3 и б-разрядных счетчиках б и умножителях 7 коэффициент деления дели-, телей 5 должен был бы быть равным 2 Однако, как известно, при вычислении синуса угла на вычислитель нужно подать в iC/2 раз больше импульсов, чем значение угла. Поэтому коэффициент деления делителей импульсов 5 должен быть в раз меньше, т.е. коэффициент деления .2. В предлагаемом устройстве коэф-фициент деления равен десяти. Так как при вычислении синуса и косинуса угла состояние регистра угла не.изменяется, то выходные импуль сы преобразователя во времени распре делены приблизительно равномерно. Перед началом преобразования вход ной счетчик ,4 и счетчики б, делители импульсов 5 триггеры 8 устанавливаются в исходное состояние(цепь установки на схеме не показана). Использование изобретения для фор мирования радиальнокруговой развертки позволяет повысить быстродействие устройства и одновременно упростить его. При формировании радиально-круговой развертки обычно вначале вычисляются .значения синуса и косинуса угла, а затем эти значения используются в качестве множителей для 1двух цифровых умножителей, на которые поступают импульсы от счетчика импульсов дальности. При использовании предла.гаемого изобретения импульсы дуальности поступают непосредственно на вход преобразователя, т.е не тратится время на предварительное вычисление синуса и косинуса угла. Упрощение устройства проявляетсяi во-первых, в уменьшении количества используемых микросхем, во-вторых, в упрощении алгоритма работы устройства. Формула изобретения Синусно-косинусный функциональный преобразователе), содержащий регистр угла, коммутатор, элементы и, триггеры, входной счетчик, первый умножитель канала синуса и блок памяти, выход синуса которого соединен с первым входом первого умножителя канала синуса, второй вход которого соединен с выходом входного счетчика, отлИчающийс я тем, что, с целью повышения быстродействия, он содержит два канала, причем в первый канал введены делитель импульсов, счетчик, второй умножитель и элемент ИЛИ, во второй канал введены два умножителя, делитель импульсов, счетчик и элемент ИЛИ, в каждом канале выходы первых умножителей через соответствующие делители импульсов подключены K входам счетчиков, выходы которых соединены с первыми входами вторых умножителей, выходы которых соединены с первыми входами триггеров, выходы которых подключены к первым входам элементов ИЛИ, выходы элементов ИЛИ каждого канала соединены соответственно с первым . ;И вторым .: коммутатора, уп равляющий вход которого подключен к выходу одиннадцатого разряда регистра угла, выходы разрядов с седьмого по десятый которого подключены к входам блока памяти, выход косинуса которого соединен с первым входом первого умножителя второго канала, второй вход которого подключен к выходу входного счетчика, выходы умножителей каждого канала подключены ко вторым входам элементов И и ИЛИ другого канала, прямые и инверсные выходы с первого по шестой разряды регистра угла подключены ко вторым входам соответственно второго умножителя первого канала и второго умножителя второго канала, третьи входы элементов И каждого канала соединены с тактовым входом преобразователя и счетным входом входного счетчика, выходы элементов И каждого канала соединены со вторыми входами триггеров тех же каналов, выходы коммутатора я вл яют с я выходами прео бразоват ел я. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 364938, кл. G 06 F 15/20, 1973. 2. Авторское свидетельство СССР 362448, кл. Н 03 К 5/156, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1989 |

|

SU1691880A1 |

| Двухотсчетный преобразователь синусно-косинусно-модулированных сигналов переменного тока в код | 1985 |

|

SU1283969A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Устройство для формирования векторов на экране электронно-лучевой трубки | 1985 |

|

SU1251161A1 |

| Устройство для вычисления функций синуса и косинуса | 1974 |

|

SU531161A1 |

| Устройство для ввода информации | 1980 |

|

SU955007A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1141404A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1986 |

|

SU1513506A2 |

| Цифровой преобразователь координат | 1979 |

|

SU842801A1 |

Авторы

Даты

1981-12-07—Публикация

1980-03-24—Подача