Изобретение относится к обларти вычислительной техники, предназначено для организации обмена информацией между оперативной памятью и высокоскоростными внешними устройствами. .

По основному авт.св. № 762591 известен блок-к ультиплексный канал, содержащий регистр информации, регистр маркеров, регистр ключа защиты, регистр признака результата, ретистр адреса внешних устройств, регистр байта СОСТОЯ.НИЯ канала, регист кода команд, регистр адреса оперативной памяти, регистр флажков, регистр счета, схему сравнения-, узел управления каналом, узел местной памяти узел модификации адресов и счета данных, блок буферизации данных, узел управления местной памятью, регистр состоянияподканала,блок сопряжения с внешними устройствами, блок динамического назначения, причем первые входы регистров адреса внешних устройств, признака результата, ключа защиты, маркеров, информации, бай та состояния канала, кода команд, адреса оперативной памяти , флажков, счета, узла модификации адресов и счета данных и четвертые входы блока бу(еризации данных, блока сопряжение с внешними устройствами соединены с третьим выходом узла управления ка. налом, второй вход и выход регистра адреса внешних устройств соединены соответственно со вторыми выходом |И входом блока сопряжения с внешними устройствами, третий вход регистра адреса внешнего устройства, первый вход схемы сравнения и первый вход узла управления каналом соединены с входной шиной сопряжения с центральным процессором, первый выход регистра признака результата, четвертый выход регистра адреса внешних устройств и второй выход узла управления каналом соединены с выходной шиной связи с центральным процессором, второй выход регистра признака результата соединен с восьмым входом узла местной памяти, первые выходы регистров информации, адреса оперативной памяти, маркеров, ключа защиты и узла управления каналом соединены с выходной шиной связи с управлением оперативной памятью, второй вход регистра ключа заадаты соединен с третьим выходом узла местной памяти, третий вход регистра ключа защиты и второй вход узла местной памяти соединены с первым выходом регистра кода команд, вторые входы регистра маркеров и-регистра информации соединены с первым выходом блока буферизации данных, третьи входы регистра информации и регистра адреса оперативной памяти соединены с вторым выходом узла местной памят,.

четвертый вход регистра информации, вторые входы регистра кода команд, адреса оперативной памяти, флажков, счета данных и шестой вход узла управления каналом соединены с входной шиной связи с управлением оперативной памятью, пятый вход и второй выход регистра информации соединены соответственно с вторыми выходом и входом блока буферизации данных, первый выход регистра байта состояния канала соединен с первым входом узла местной памяти, второй выход регистра байта состояния- канала соеднен с пятым входом узла управления каналом, второй выход регистра кода команд соединен с третьим входом блока сопряжения с внешними устройствами и с четвертым входом узла управления каналом, третий выход регистра адреса оперативной памяти соединен с третьим входом узла местной памяти, второй выход регистра адреса оперативной памяти соединен с первым входом блока буферизации данных, -первый выход регистра флажков соединен с третьим входом узла управления каналом, первый выход регистра счета соединен с четвертым входом узла .местной памяти, первый выход схемы сравнения соединен с вторым входом узла управления каналом, чет.вертый выход узла управления каналом соединен с вторым входом узла управления местной памятью, седьмой вход узла управления каналом соедине с первым выходом регистра состояния подканала, восьмой вход узла управления каналом соединен с. третьим выходом блока сопряжения с внешними устройствами, первый выход и седьмой вход узла местной памяти соединены соответственно с вторим входом и выходом регистра состояния подканала, шестой вход узла местной памяти соединен .с первым выходом узла управления местной памятью, девятый вход узла местной памяти и третий вход блка буферизации данных соединены с пятым выходом блока сопряжения с внешнми устройствами, четвертый выход и пятый вход узла местной памяти соединены соответственно с третьим входом и вторым выходом узла модификации адресов и счета данных, первый выход и второй вход узла модификации адресов и счета данных соединены соответственно с четвертым выходом и пятым входом блока буферизации данны третий выход блока буферизации данны соединен с пятым входом блока .сопря жения с внешним устройством, второй выход узла управления местной память соединен с первым входом регистра сотояния подканала, первые вход и выход блока сопряжения с внешннЛри- устройствами соединены соответственно с выходной и входной шинами.рвязи с внешними устройствс1ми, третий

вход и третий выход узла управления местной памятью соединены соответственно с выходом и входом блока динамического наэначенияП.

В указанном канале возникающее во внешнем устройстве (ВУ) по окончании канальной программы условие . прерывания не принимается на хранение в подканал, а сохраняется в ВУ. Это не позволяет, во-первых, освобождать ВУ сразу по окончании канальной программы и тем самым снижает интегральную производительност системы в тех случаях, когда ВУ используется в многоканальном режиме работы Анормальный режим работы быстродействующих ВУ), особенно для мультипроцессорных систем, имеющих общее поле внешней памяти, во-вторых, совмещат-ь во времени выполнение текущей канальной программы и учета прерывания заверишвшихся канальных программ для освобождения подканалов и тем самым снижает интегральную производительность канала.

Целью изобретения является повышение интегральной производительности в режиме блокового мультиплексирования за счет освобождения ВУ в многоканальном режиме и повышение интегральной производительности канала за счет освобождения подканалов завершающихся канальных проЬрамм во время выполнения текущей кнальной программы.

Это достигается тем, что в блокмультиплексный канал введены память очереди-и регистр прерываний , пер-вый и второй входы которого соединены соответственно с первым выходом регистра адреса внешних устройств и четвертым выходом узла управления местной памятью, первый и второй выходы регистра прерываний соединевы соответственно с выходной шиной связи с центральным процессором и пятым входом узла управления местной памятью, .соединенного двухстороней связью с памятью очереди, выход которой соединен с девятым входом узла управления каналом.

За счет введения памяти очереди и регистра прерываний появляется воможность освобождать ВУ сразу по окончании канальных программ, формировать внутри канала очередь -устройств, подканалы которых хранят пррывания, и совмещать во времени уче прерывания для закончившихся канальных программ с выполнением текущих канальных программ.

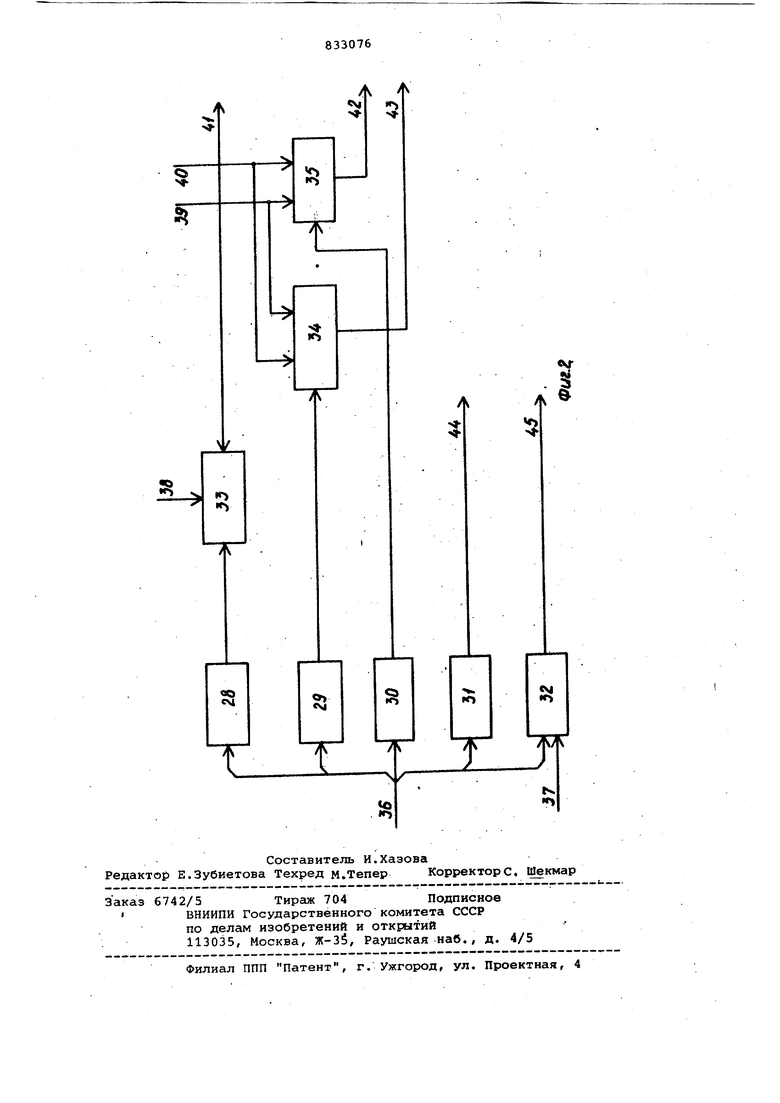

На фиг.1 приведена структурная схема блок-мультиплексного канала, на фиг,2 - структурная схема узла управления местной памятью.

Устройство содержит регистр 1 сщреса внешних устройств, регистр 2 признака результата, регистр 3 ключа защиты, регистр 4 млркороп, регистр 5 информации, .регистр б байта, состояния канала, регистр 7 кода команд, регистр 8 адреса оперативной памяти, регистр 9 флажков, регистр 1.0 Счета, схему 11 сравнения, узл 12 управления каналом, узел 13 местной памяти, узел 14 модификации адресов и счета данных, блок 15 буферизации данных, узел 16 управления местной памятью, регистр 17 состояния прдканала, блок 18 сопряжения с внешними устройствами, регистр 19 прерываний, память 20 очереди (устройств, подканалы которых хранят прерывания), блок 21 динамического назначения, входная шина 22 сопряжения с центральным процессором, выходная шина 23 связи с центральным процессором, входная шина 24 связи с управлением оперативной памятью, выходная шина 25 связи с управлением оперативной памятью, выходная шина 26 связи-с внешними устройствами, входная ишна 27 связи с внешними устройствами.

Узел 16.управления местной памятью (см. фиг.2) содержит: элементы ИЛИ 28 для формирования постоянных .адресов местной памяти, элементы ИЛИ 29 для управления определением адреса памяти назначения, элементы ИЛИ 30 для управления определением адреса памяти очереди подканалов, элементы ИЛИ 31 для управления приемом состояния подканала в регистр состояния подканала, триггер 32 за.нятости регистра прерываний, формирователь 33 адреса обращения местной памяти, формирователь 34 адреса обращения в память назначения, формирователь 35-адреса памяти очереди уст ройств,подканалы которых хранят преры вания,шина 36 управляющих сигналов из . Vзлa управления каналом, шина 37 из памяти очереди подканалов, хранящих прерывания, шина 38 номера подканала из блока динамического назначения, шина 39 адреса из регистра адре- . са внешних устройств, шина 40 адреса из регистра прерываний, шина 41 адреса обращения и управления в узел местной памяти, шина 42 адреса, и управления в память очереди устройств , подканалы которых хранят прерывание, шина 43 адреса и управления в блок динамического назначения, шина 44 управления регистром состояния подканала, шина 45

5. управления регистром прерываний.

Память 20 очереди/ПОЧ/предназначена для фиксации соответствия между адресами ВУ и соответствующими им двоичными признаками состояния.. Для каждого возможного значения адреса ВУ в памяти имеется одна однобитная ячейка, физический адрес которой совпадает с адресом ВУ, и в ней хранится признак состояния для соответствующего ВУ.

Единичное значение признака состояния означает, что для соответствующего ВУ есть назначенный подканал, который находится в состоянии хранения прерывания. Нулевое значение признака состояния означает, что для соответствующего ВУлибо нет назначенного подканала, либо он. не нахс/дился в состоянии хранения прерывания.

Регистр прерываний (РП) представляет собой счетчик, который может работать в режиме счета и в режиме хранения адреса...

Для определения режима работы регистра служит триггер занятости регистра прерываний в эле 16 управления местной памятью. Единичное состояние триггера означает,.что регистр находится в режиме хранения, т.е. занят.

Ддрес ВУ, для которого требуется прерывание, может либо приниматься с регистра 1 адреса внешнихустройств , либо образовываться на ,регистре 19 прерываний в результате просмотра в. счетном режиме очереди подканалов, хранящих прерывание. Просмотр очереди подканалов, храншцих прерывания, осуществляется всагда, когда регистр прерывания ос вободен,.так как триггер занятое- ти находится в нулевом состоянии. Единичное состояние триггера занятости регистра прерываний указыг. вает, что на регистре установлен адрес ВУ для прерывания либ1э -в результате приема адреса ВУ из регистра 1, либо по сигналу из памяти очереди 20 (подканалов,хранящих прерывания), os начающему, что в результате просмотра очереди найден подканал, хранящий прерывание.

Триггер занятости сохраняет единичное состояние до окончания учета прерывания, а затем сбрасывается по сигналу из узла управления каналом.

Перед началом работы блок-мультиплексного канала производится началь ная установка по сигналам НАЧАЛЬНАЯ УСТАНОВКА КАНАЛА (НУК) И НАЧАЛЬНАЯ .УСТАНОВКА КАНАЛА (КОРОТКИЙННУКК) .

НУК..„

НУКК - - - 1

По короткому сигналу регистр 19 прерываний, и триггер 32 устанавливаются в О.На регистре 19 начинается перебор адресов, начиная с нулевого. При этом в памятьназначения записываются нули во все разряды признаков назначения, в память 20 на один вход подается О, на другие входы - 1 и по вс.ем перебираемым адресам памяти записываются нули.

Во время работы канала на регистр 19 продолжается перебор адресов.

После завершения канальной прог граммы соответствующие условия nj eрывания, возникающие в ВУ, принимаюся в подканал, подканал переводится состояние ХРАНИТ ПРЕРЫВАНИЕ по сигналу УСТАНОВИТЬ ПОДКАНАЛ В ХРАНИТ ПРЕРЬтАНИЕ (УСПКвХП) и при этом в пмять 20 записывается 1 по aдpecy находящемуся на регистре 1. Внешнее устройство, работающее с каналом, освобождается .для работы.

Поскольку канал работает в муль типлексном режиме, после завершения одной канальной программы и до учета прерывания от процессора по результатам завершения в канале моггут начаться и завершиться еще несколько канальных программ. Поскольку сигнал ПОДКАНАЛ ДЛЯ УЧЕТА ПРЕРЫВАНИЯ УСТАНОВЛЕН (ПУПРУ), запрос на прерывание в процессор остается во время рабочего состояния канала, а адрес устройства, вызывающего прерывание, сохраняется на регистр 18.

После приема сигнала УЧЕТ ПРЕРЫВАНИЯ из процессора узел управления каналом 12 настраивается на запись в оперативную память слова состояни канала. Если в момент учета прерывания канал выполняет передачу данных по другой канальной программе, в блок динамического назначения по сигналу ВЬЮРАТЬ НА блок назначения /ВБН/ выбирается информация из памяти назначения по адресу, формируемому из адреса регистра 19. В оперативную память записывается слово состояния кан,ала. При завершении прюцедуЕИ учета прерывания из узла управления канаэтом 12 поступает сигнал ОТМЕНИТЬ НАЗНАЧЕНИЕ ПОДКАНАЛА /ОНПК/, по которому в память назначения по адресу на регистре 19 записывается О В признака йазн чения. В память 20 по адресу на регистре 19 записывается О.

Вслед за сигналом ОНПК подается сигнал ОСВОБОДИТЬ РП ОСРП, по которому сбрасывается триггер регистр 19. Как только триггер 32 сбросится, регистр 19 начинает работать в режиме счета. Один из триггеров регистра 19 устанавливается в 1, разрешаемся выборка из памяти очереди. Каждый такт к содержимому регистра 19 прибавляется 1, при этом-из памяти 20 выбирается содержимое по ещресу на регистре 19. Если из памяти 20 выбирается О, триггер .32 остается в нулевом состоянии и режим счета продолжется. Если из ПОЧ 20 выбирается 1, на регистре 19 остается адрес устройства, для которого в ПОЧ 20 записана 1.

Сигнал ПУПРУ поступает в даел управления каналом 12. Если канал в момент установки ПУПРУ находится в рабочем состоянии, устанав.пивается запрос на прерывание в процессор и ожидается учет прерывания. Если в момент установки ПУПРУ канал не находится в рабочем состоянии, устанавливается состояние канала и запрос на прерывание в процессор. До введения в канал памяти 20 регистра 19 в момент завершения канальной программы канал не имел возможности помнить, какой из подкана-. лов закончил работу, и поэтому в подканал не принимались условия окон чания канальной программы, а оставались в устройстве. Подканал же ос тавался в рабочем состоянии до учета прерывания от процессора с Учет прерывания по условиям завершения канал ной программы мог производиться толь ко при наличии нерабочего состояния кансша. В. момент работы канала в канале имеется возможность освободить от условий окончания подканал и устройство, т.е. принять в подканал условие окончания и выполнить учет прерывания. Однако сделать это без дополнительной памяти устройств, которые закончили работу, не представл ется возможным, так как подканалы пассивны и работают только при обращении к ним. Чтобы сделать подканалы харнящие прерывание, активными по от ношению к каналу, необходимы память очереди и счетчик, который постоянно проематривё1л бы ее. Если в канал ввводится: память оче реди (УСТРОЙСТВ, подканалы которых хранят прерывание, сразу послеокончания канальной программы .условия окончания принимаются в канал, подканал переводится в состояние ХРАНИТ ПРЕРЫВАНИЕ и ставится в очередь на учет прерывания, а устройство освобождается для работы по другому направлейию. . . Таким образом, время ожидания устройства практически сведено к минимуму. Снижая непроизводительное время ожидания устройства, мы тем самым увеличиваем интегральную производительность системы, так как средняя длина очереди супервизора ввода-вывода 10 программ и необходимость более быстрого освобождения устройства всегда существует. Освобождение подканалов параллельно с выполнением канальной программы приобретает особое значение в режиме насыщения канала, когда заняты все подканалы. Таким образом, введенное оборудование увеличивает интегральную производительность в режиме блокового мультиплексирования в случае исполь зования внешних устройств в многоканальном режиме, увеличивает интегральную производительность канала за счет совмещения во времени выполнения текущей канальной программы и прерывания ввода-вывода для ранее завершившихся канальных программ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок-мультиплексный канал | 1977 |

|

SU691841A1 |

| Устройство отсчета времени в цвм | 1977 |

|

SU691828A1 |

| Селекторный канал | 1983 |

|

SU1226477A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Мультиплексный канал | 1974 |

|

SU525941A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Система обмена | 1978 |

|

SU809138A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

БЛОК-МУЛЬТИПЛЕКСНЫЙ Ю\НАЛ . по авт.св. № 7'62591, о т л и. ч а ю- щ и и с я тем, что, с целью повьш1е- ния интегральной производительности в режиме блок,ового мультиплексирования, он содержит память очереди и регистр прерываний, первый и второй входы которого соединены соответственно с первым выходом регистра адреса внешних устройств и четвертым выходом узла управления'местной памятью, первый и второй выходы регистра прерываний соединены соответственно с выходной шиной связи с центральным процессором и с пятым входом узла управления местной памятью, соединенного двухсторонней связью с памятью очереди, выход' которой соединен с девятым входом узла управления каналом.^1 «0(g(Лс^-ч00iOOICOО<1о:>&

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР ».762591, кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| . | |||

Авторы

Даты

1983-04-23—Публикация

1979-07-17—Подача