(54) АНАЛОГОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматической коррекции массы кокса | 1986 |

|

SU1381165A1 |

| Устройство для деления аналоговых сигналов | 1990 |

|

SU1795479A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2549360C1 |

| Устройство компенсации помех | 1983 |

|

SU1107296A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство для коррекции массы кокса | 1987 |

|

SU1468917A1 |

| УСТРОЙСТВО КООРДИНИРОВАННОГО РЕГУЛИРОВАНИЯ УГЛОВОГО БОКОВОГО ДВИЖЕНИЯ ЛЕТАТЕЛЬНОГО АППАРАТА | 1990 |

|

RU2047888C1 |

| УСТРОЙСТВО СОПРОВОЖДЕНИЯ ЦЕЛЕЙ ПО НАПРАВЛЕНИЮ | 1983 |

|

SU1840107A1 |

| Регулятор | 1982 |

|

SU1092464A1 |

| Система управления мощностью турбины | 1984 |

|

SU1227823A1 |

Изобретение относится к вычислительной технике и может быть использовано в аналоговых вычислительных машинах (АВМ) для решения задач расчета оптимальных рецептов смесей различных продуктов - бензинов, дизельных топлив, смесей кормов и т.п., формулируемых в виде задач математического программирования, спецификой которых является то, что сумма переменных равна единице.

Известны аналоговые вычислительные устройства для решения смесевых задач, родержащие блок регулируемых интеграторов, блок весовых коэффициентов, сумматоры, блок определения ошибок и ограничители 1 и 2.

Основными недостатками этих устройств являются необходимость ручного подбора масштабного коэффициента при целевой функции во время решения задач и низкая точность устройства (порядка нескольких процентов).

Наиболее близким по технической сушности к предлагаемому является устройство, содержащее блок интеграторов, переключатель режимов работы, блок весовых коэффициентов, блок сумматоров, блок задания эталонного сигнала, блок вычитания, блок выделения максимального значения модуля ошибки, блок задания коэффициентов целевой функции и нелинейный преобразователь 3.

В этом устройстве выбор решения происходит автоматически, но устройство обладает низкой точностью из-за существенного влияния методических и аппаратурных погрешностей.

Цель изобретения - повышение точносустройства.

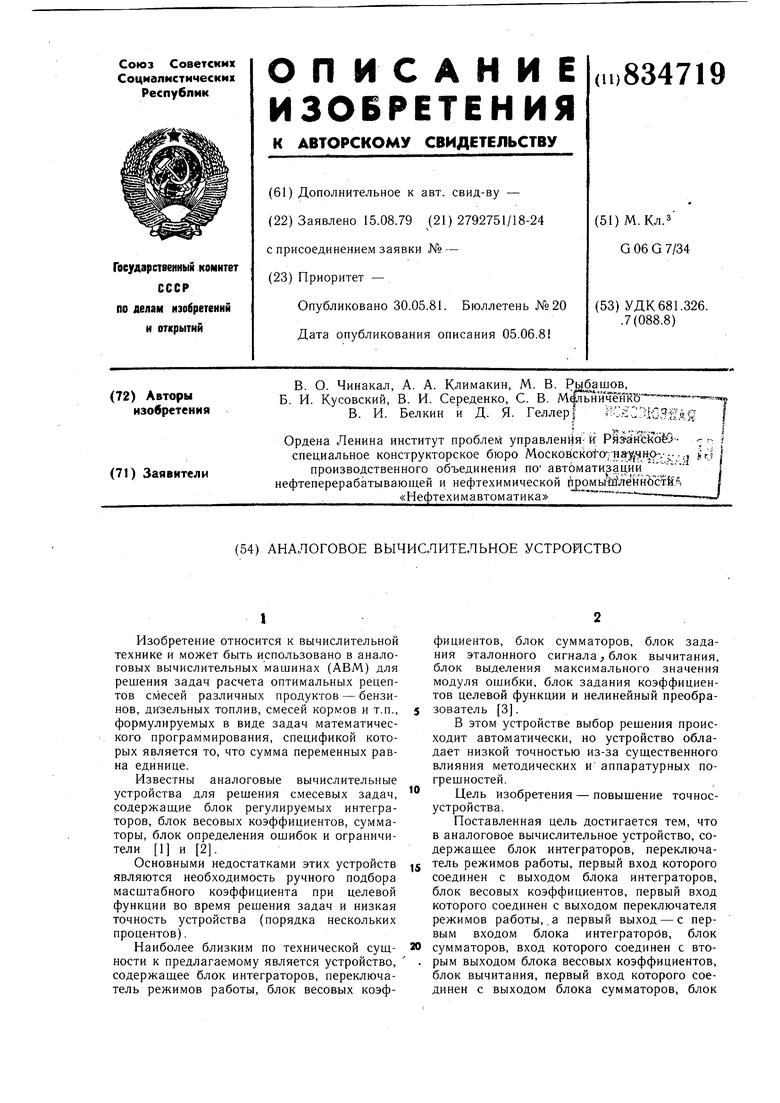

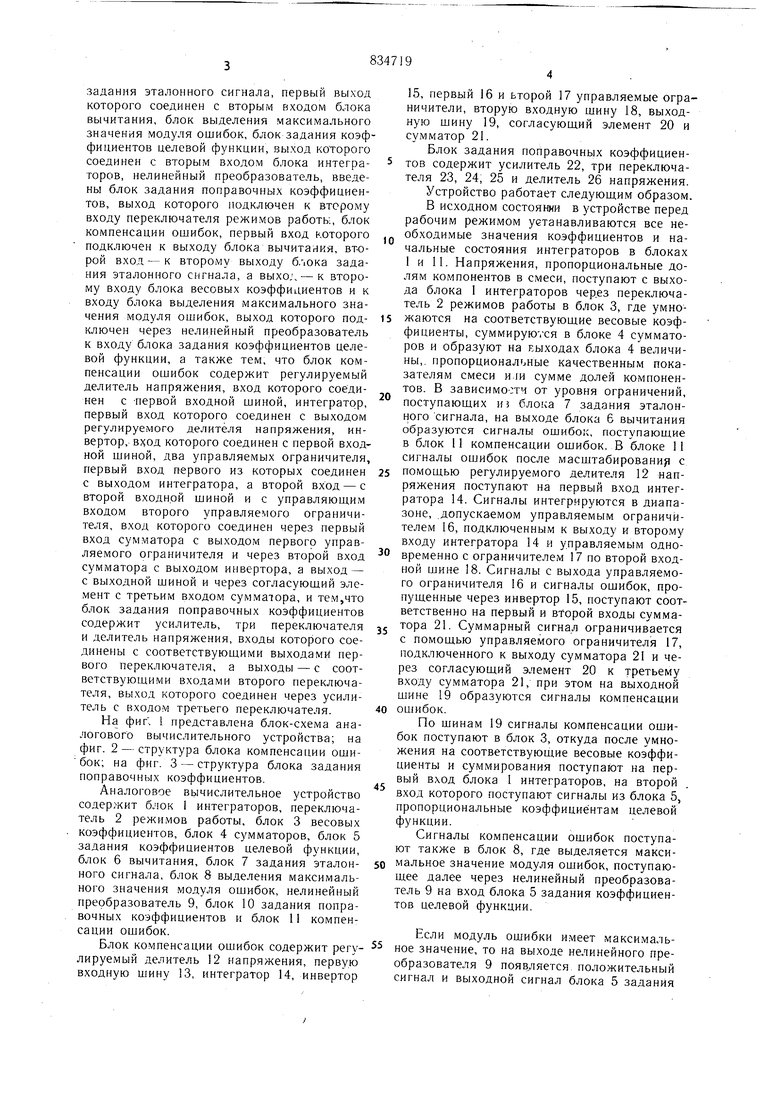

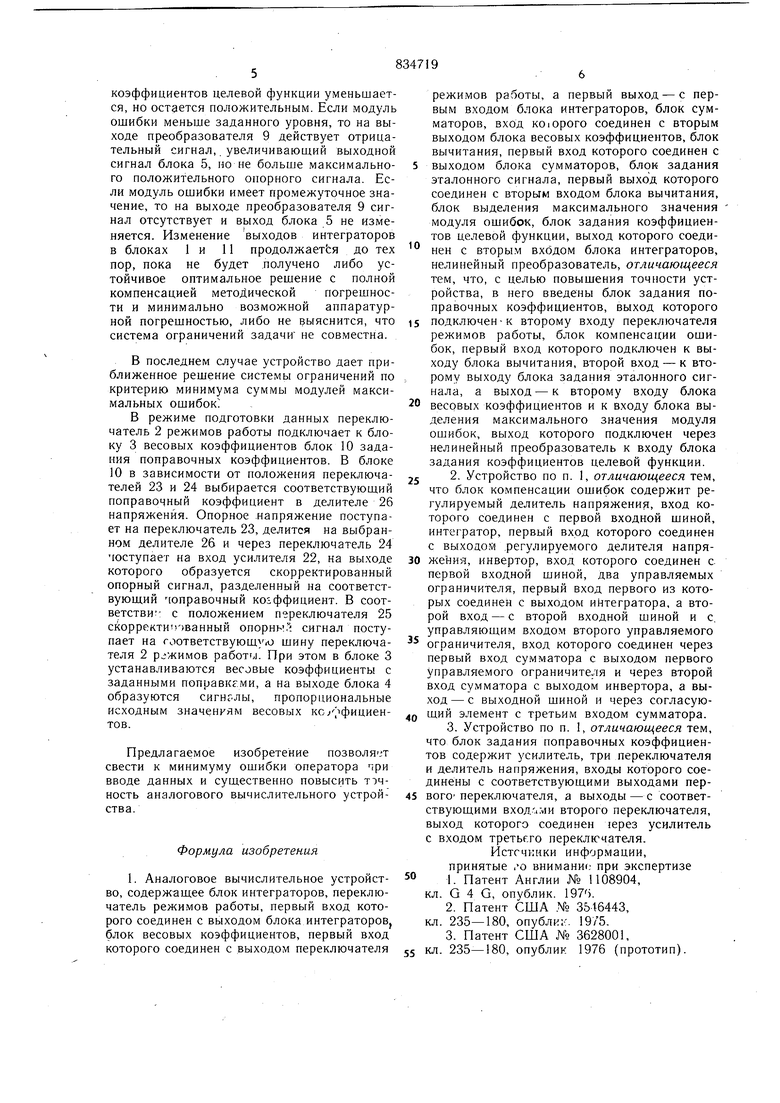

Поставленная цель достигается тем, что в аналоговое вычислительное устройство, содержащее блок интеграторов, переключатель режимов работы, первый вход которого соединен с выходом блока интеграторов, блок весовых коэффициентов, первый вход которого соединен с выходом переключателя режимов работы, .а первый выход - с первым входом блока интеграторбв, блок сумматоров, вход которого соединен с вторым выходом блока весовых коэффициентов, блок вычитания, первый вход которого соединен с выходом блока сумматоров, блок задания эталонного сигнала, первый выход которого соединен с вторым входом блока вычитания, блок выделения максимального значения модуля ошибок, блок задания коэффициентов целевой функции, выход которого соединен с вторьЕМ входом блока интеграторов, нелинейный преобразователь, введены блок задания поправочных коэффициентов, выход которого подключен к второму входу переключателя режимов работы, блок компенсации ошибок, первый вход которого подключен к выходу блока вычитания, второй вход - к второму выходу б.юка задания эталонного сигнала, а выхо;, - к второму входу блока весовых коэффи11иентов и к входу блока выделения максимального значения модуля ошибок, выход которого подключен через нелинейный преобразователь к входу блока задания коэффициентов целевой функции, а также тем, что блок компенсации ошибок содержит регулируемый делитель напряжения, вход которого соединен с -первой входной шиной, интегратор, первый вход которого соединен с выходом регулируемого делителя напряжения, инвертор, вход которого соединен с первой входной шиной, два управляемых ограничителя, первый вход первого из которых соединен с выходом интегратора, а второй вход - с второй входной шиной и с управляющим входом второго управляемого ограничителя, вход которого соединен через первый вход сумматора с выходом первого управляемого ограничителя и через второй вход сумматора с выходом инвертора, а выход - с выходной шиной и через согласующий элемент с третьим входом сумматора, и тем,что блок задания поправочных коэффициентов содержит усилитель, три переключателя и делитель напряжения, входы которого соединены с соответствующими выходами первого переключателя, а выходы - с соответствующими входами второго переключателя, выход которого соединен через усилитель с входом третьего переключателя. На фиг; 1 представлена блок-схема аналогового вычислительного устройства; на фиг. 2 - структура блока компенсасши оши бок; на фиг. 3 - структура блока задания поправочных коэффициентов. Аналоговое вычислительное устройство содержит блок 1 интеграторов, переключатель 2 режимов работы, блок 3 весовых коэффициентов, блок 4 сумматоров, блок 5 задания коэффициентов целевой функции, блок 6 вычитания, блок 7 задания эталонного сигнала, блок 8 выделения максимального значения модуля ошибок, нелинейный преобразователь 9, блок 10 задания поправочных коэффициентов и блок 11 компенсации ошибок. Блок компенсации ошибок содержит регулируемый делитель 12 напряжения, первую входную шину 13, интегратор 14, инвертор 15, первый 16 и ьторой 17 управляемые ограничители, вторую входную шину 18, выходную шину 19, согласующий элемент 20 и сумматор 21. Блок задания поправочных коэффициентов содержит усилитель 22, три переключателя 23, 24, 25 и делитель 26 напряжения. Устройство работает следующим образом. В исходном состоянии в устройстве перед рабочим режимом устанавливаются все необходимые значения коэффициентов и начальные состояния интеграторов в блоках 1 и П. Напряжения, пропорциональные долям компонентов в смеси, поступают с выхода блока I интеграторов через переключатель 2 режимов работы в блок 3, где умножаются на соответствующие весовые коэффициенты, суммируются в блоке 4 сумматоров и образуют на выходах блока 4 величины,, пропорциональные качественным показателям смеси или сумме долей компонентов. В зависимости от уровня ограничений, поступающих и5 блока 7 задания эталонного сигнала, на выходе блока 6 вычитания образуются сигналы ошибок, поступающие в блок 11 компенсации ошибок. В блоке И сигналы ошибок после масштабировани с помощью регулируемого делителя 12 напряжения поступают на первый вход интегратора 14. Сигналы интегрируются в диапазоне, .допускаемом управляемым ограничителем 16, подключенным к выходу и второ.му входу интегратора 14 и управляемым одновременно с ограничителем 17 по второй входной шине 18. Сигналы с выхода управляемого ограничителя 16 и сигналы ощибок, пропущенные через инвертор 15, поступают соответственно на первый и вtopoй входы сумматора 21. Суммарный сигнал ограничивается с помощью управляемого ограничителя 17, подключенного к выходу сумматора 21 и через согласующий элемент 20 к третьему входу сумматора 21, при этом на выходной щине 19 образуются сигналы компенсации ошибок. По шинам 19 сигналы компенсации ошибок поступают в блок 3, откуда после умножения на соответствующие весовые коэффициенты и суммирования поступают на первый вход блока 1 интеграторов, на второй вход которого поступают сигналы из блока 5, пропорциональные коэффициентам целевой функции. Сигналы компенсации ошибок поступают также в блок 8, где выделяется максимальное значение модуля ошибок, поступающее далее через нелинейный преобразователь 9 на вход блока 5 задания коэффициентов целевой функции. Если модуль ошибки имеет максимальное значение, то на выходе нелинейного преобразователя 9 появляется, положительный сигнал и выходной сигнал блока 5 задания коэффициентов целевой функции уменьшается, но остается положительным. Если модуль ошибки меньше заданного уровня, то на выходе преобразователя 9 действует отрицательный сигнал,. увеличивающий выходной сигнал блока 5, но не больше максимального положительного опорного сигнала. Если модуль ошибки имеет промежуточное значение, то на выходе преобразователя 9 сигнал отсутствует и выход блока 5 не изменяется. Изменение выходов интеграторов в блоках 1 и 11 продолжаетЬя до тех пор, пока не будет получено либо устойчивое оптимальное решение с полной компенсацией методической погрешности и минимально возможной аппаратурной погрешностью, либо не выяснится, что система ограничений задачи не совместна. В последнем случае устройство дает приближенное решение системы ограничений по критерию минимума суммы модулей максимальных ошибок В режиме подготовки данных переключатель 2 режимов работы подключает к блоку 3 весовых коэффициентов блок 10 задания поправочных коэффициентов. В блоке 10 в зависимости от положения переключателей 23 и 24 выбирается соответствующий поправочный коэффициент в делителе 26 напряжения. Опорное напряжение поступает на переключатель 23, делится на выбранном делителе 26 и через переключатель 24 чоступает на вход усилителя 22, на выходе которого образуется скорректированный опорный сигнал, разделенный на соответствующий поправочный коэффициент. В соответстви: с положением переключателя 25 скорректи))ванный опорнн сигнал поступает на соответствующую шину переключателя 2 р.;жимов работь. При этом в блоке 3 устанавливаются весовые коэффициенты с заданными поправками, а на выходе блока 4 образуются сигналы, пропорциональные исходным значениям весовых KG |1фициeнтов. Предлагаемое изобретение позволя т свести к минимуму ошибки оператора при вводе данных и существенно повысить точность аналогового вычислительного устройства. Формула изобретения 1. Аналоговое вычислительное устройство, содержащее блок интеграторов, переключатель режимов работы, первый вход которого соединен с выходом блока интеграторов блок весовых коэффициентов, первый вход которого соединен с выходом переключателя режимов работы, а первый выход - с первым входом блока интеграторов, блок сумматоров, вход KOioporo соединен с вторым выходом блока весовых коэффициентов, блок вычитания, первый вход которого соединен с выходом блока сумматоров, блок задания эталонного сигнала, первый выход которого соединен с вторым входом блока вычитания, блок выделения максимального значения модуля ошибок, блок задания коэффициентов целевой функции, выход которого соединен с вторым входом блока интеграторов, нелинейный преобразователь, отличающееся тем, что, с целью повышения точности устройства, в него введены блок задания поправочных коэффициентов, выход которого подключен-к второму входу переключателя режимов работы, блок компенсации ошибок, первый вход которого подключен к выходу блока вычитания, второй вход - к второму выходу блока задания эталонного сигнала, а выход - к второму входу блока весовых коэффициентов и к входу блока выделения максимального значения модуля ошибок, выход которого подключен через нелинейный преобразователь к входу блока задания коэффициентов целевой функции. 2.Устройство по п. 1, отличающееся тем, что блок компенсации ошибок содержит регулируемый делитель нанряжения, вход которого соединен с первой входной шиной, интегратор, первый вход которого соединен с выходом регулируемого делителя напряжения, инвертор, вход которого соединен с первой входной шиной, два управляемых ограничителя, первый вход первого из которых соединен с выходом интегратора, а второй вход - с второй входной шиной и с, управляющим входом второго управляемого ограничителя, вход которого соединен через первый вход сумматора с выходом первого управляемого ограничителя и через второй вход сумматора с выходом инвертора, а выход - с выходной щиной н через согласующий элемент с третьим входом сумматора. 3.Устройство по п. 1, отличающееся тем, что блок задания поправочных коэффициентов содержит усилитель, три переключателя и делитель напряжения, входы которого соединены с соответствующими выходами первого-переключателя, а выходы - с соответствующими вход .;«1и второго переключателя, выход которого соединен через усилитель с входом третьего переключателя. Источники информации, принятые .О внимание при экспертизе 1.Патент Англии № 1108904, кл. G 4 G, опублик. 197). 2.Патент США .4° 3546443, кл. 235-180, опублк;-:. 19/5. 3.Патент США № 3628001, кл. , опублик 1976 (прототип).

фиг..1

Авторы

Даты

1981-05-30—Публикация

1979-08-15—Подача